视频链接

USB PHY硬件电路设计---ULPI & UTMI+ & HSIC 01_哔哩哔哩_bilibili

USB PHY---ULPI & UTMI+ & HSIC

1、USB PHY基本介绍

芯片厂商开发了一些USB PHY芯片,可以把DP、DM上的差模信号转成共模信号。

USB PHY负责最底层的信号转换,作用类似于网口的PHY。

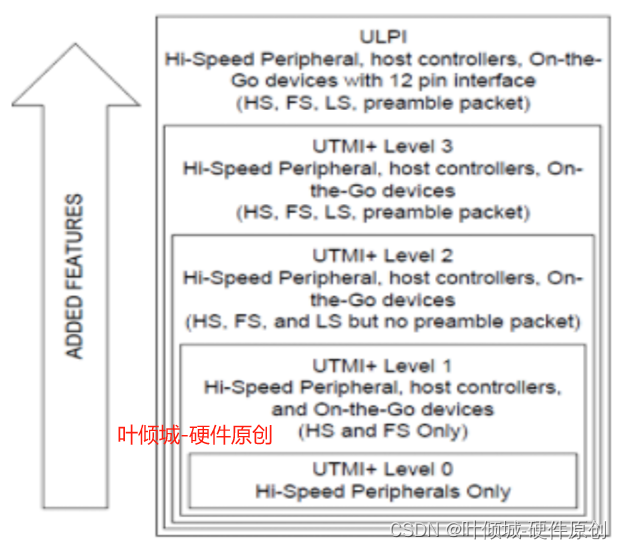

USB信号传输前,需要通过PHY把USB控制器的数字信号转成线缆上的模拟信号。usb控制器和phy之间的总线主要有3种:一种是ULPI,一种是UTMI+,还有一种是HSIC。

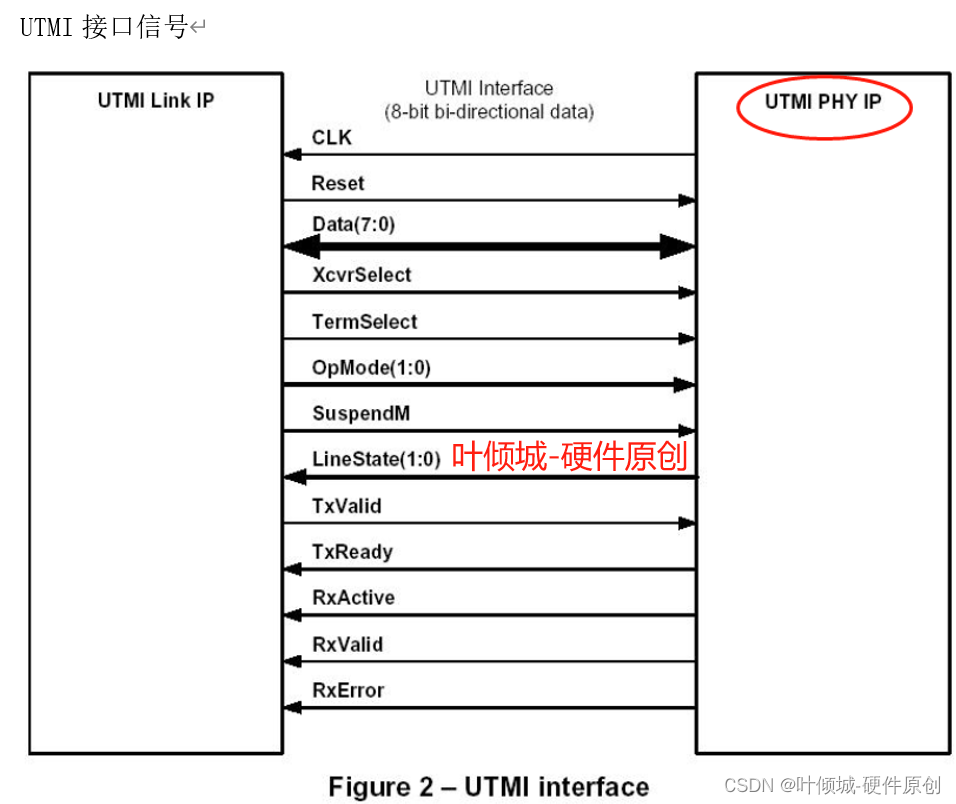

UTMI(USB2.0 Transceiver Macrocell Interface)是一种用于USB controller和USB PHY通信的协议。相对于ULPI,UTMI有更多的控制信号,支持8bit/16bit 数据接口。

ULPI协议的全称是UTMI+ Low Pin Interface。从名字上就可以看出ULPI是UTMI的Low Pin版本。

2、ULPI和UTMI+区别

1、线的数量

2、ULPI需要读写寄存器,而UTMI+只需直接拉高或拉低信号线。

ULPI是在UTMI+的基础上封装了一层。

具体的框图可以参考附件《UTMI+ SPECIFICATION》

UTMI+ level 0 P8

UTMI+ level 1 P10

UTMI+ level 2 P18

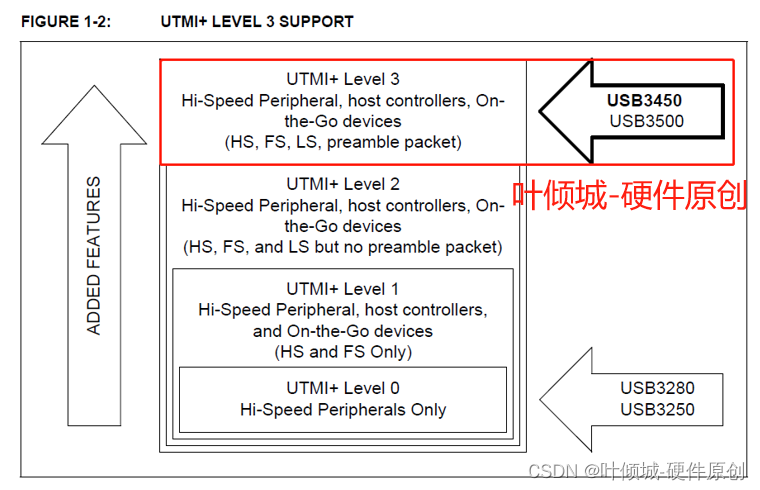

USB3450

3、ULPI接口详解(以USB3320为例)(★)

USB3320C-EZK是一款高度集成的全功能高速USB 2.0 ULPI收发器, 基于Microchip ULPI接口。高速USB 2.0收发器提供一种可配置的物理层 (PHY)解决方案, 可配合多种产品使用。

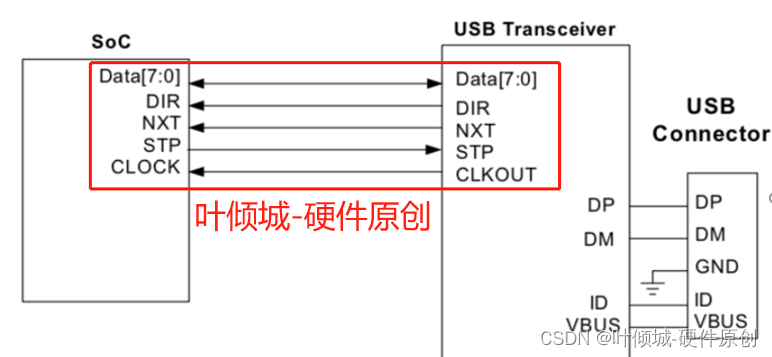

3.1、ULPI信号接口 (★)

3.2、结构及功能框图

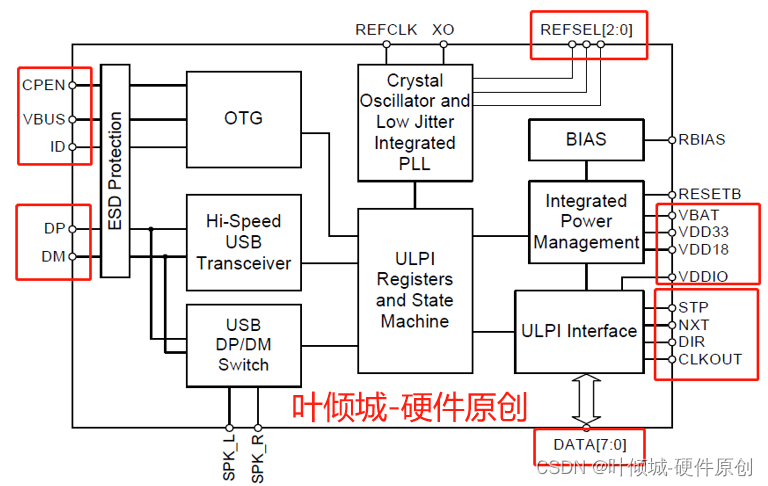

USB3320由下图所示的块组成。图中显示的所有上拉电阻都内部连接到VDD33引脚。

3.3、管脚定义(USB3320)

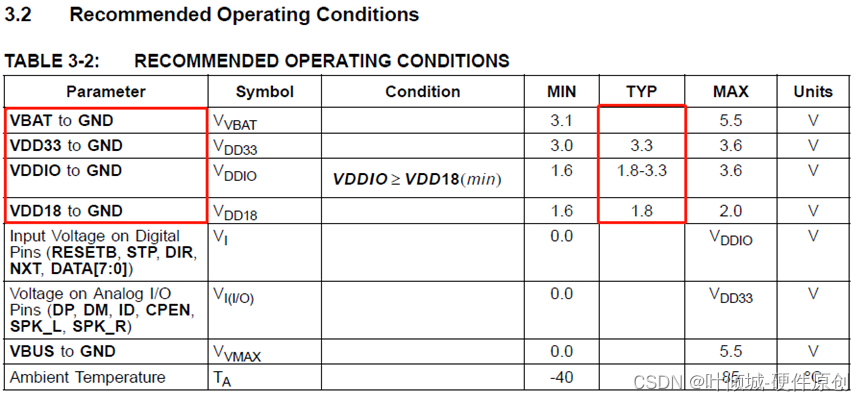

电源管脚

| 管脚符号 | 类型 | 描述 |

| VDD33 | Power | 3.3V Regulator Output. (★)3.3V调节器输出。 |

| VDD18 | Power | External 1.8V Supply input pin. (★) 外部1.8V电源输入引脚。 |

| VBAT | Power | Regulator input. 调节器的输入。 |

| VDDIO | Power | External 1.8V to 3.3V ULPI supply input pin. This voltage sets the value of VOH for the ULPI signals. This pad needs to be bypassed with a 0.1uF capacitor to ground, placed as close as possible to the USB3320. |

| GND | Ground | 地。 |

| 管脚符号 | 类型 | 描述 |

| CPEN | Out | External 5V supply enable. Controls the external VBUS power switch. CPEN is low on POR. |

| VBUS | I/O Analog | This pin connects to an external resistor (RVBUS) connected to the VBUS pin of the USB cable. This pin is used for the VBUS comparator inputs and for VBUS pulsing during session request protocol.(★) |

| ID | Input | ID pin of the USB cable. For applications not using ID this pin can be connected to VDD33. For an A-Device ID is grounded. For a B-Device ID is floated. |

| DP | I/O Analog | D+ pin of the USB cable. |

| DM | I/O Analog | D- pin of the USB cable. |

| SPK_L | I/O Analog | USB switch in/out for DM signals |

| SPK_R | I/O Analog | USB switch in/out for DP signals |

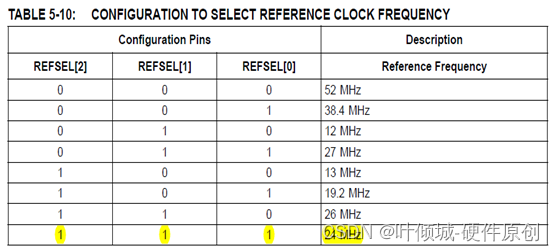

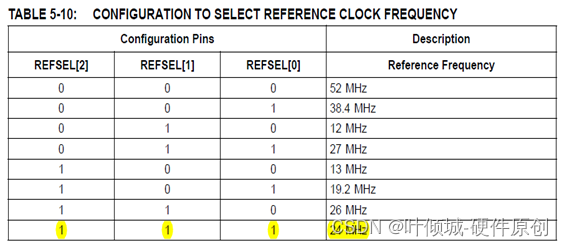

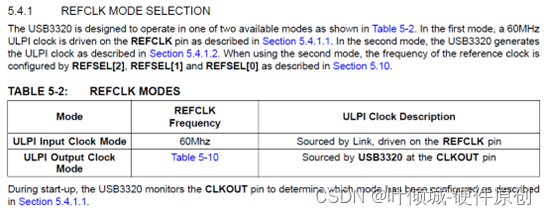

| REFCLK | Input | 1、ULPI Output Clock Mode: Reference frequency as defined in Table 5-10.

2、ULPI Input Clock Mode:60MHz ULPI clock input. |

| XO | Out | External resonator pin. When using an external clock on REFCLK, this pin should be floated. 外部谐振器管脚。当在REFCLK上使用外部时钟时,这个引脚应该被浮动(悬空)。 |

| REFSEL [0-2] | Input | Configuration to select reference clock frequency (选择参考时钟频率的配置)

|

| DATA[7:0] | I/O | ULPI bi-directional data bus. 双向数据总线 |

| STP | Input | The Link asserts STP for one clock cycle to stop the data stream currently on the bus. If the Link is sending data to the transceiver, STP indicates the last byte of data was on the bus in the previous cycle. |

| NXT | OUT /high | The transceiver asserts NXT to throttle the data. |

| DIR | OUT | Controls the direction of the data bus. |

| CLKOUT | OUT | 1、ULPI Output Clock Mode 2、ULPI Input Clock Mode:This pin is connected to VDDIO to configure 60MHz ULPI Input Clock mode as described in Section 5.4.1.

|

| RESETB | Input /LOW | Reset 复位,低有效 |

| RBIAS | Analog | Bias Resistor pin. This pin requires an 8.06kΩ (±1%) resistor to ground, placed as close as possible to the USB3320. Nominal voltage during ULPI operation is 0.8V. 偏置电阻。该引脚需要8.06kΩ(±1%)电阻接地,放置尽可能接近USB3320。 ULPI运行时的标称电压为0.8V。 |

上电流程

3.4、USB3320时序

3.5、USB3320应用框图

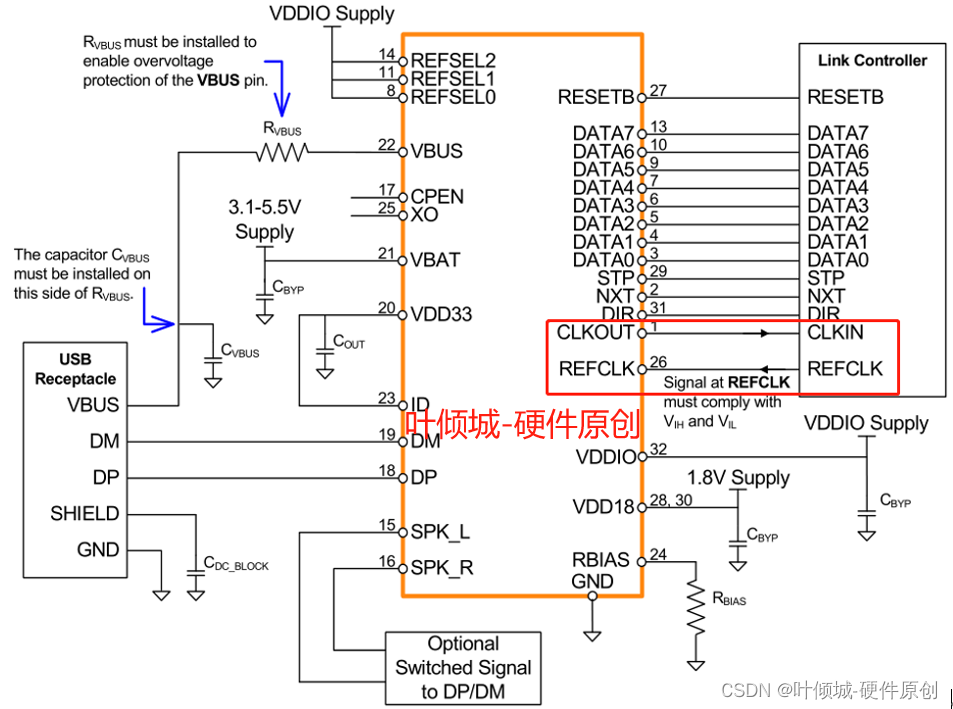

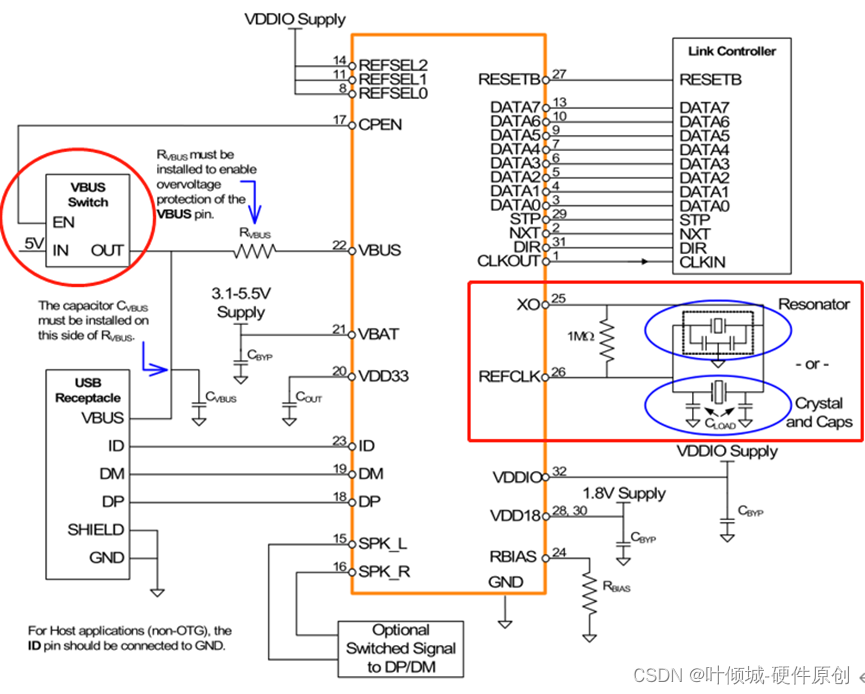

下图非常非常重要!!!

3.5.1、DEVICE, ULPI OUTPUT CLOCK MODE, 24MHZ

3.5.2、DEVICE, ULPI INPUT CLOCK MODE, 60MHZ

3.5.3、HOST OR OTG , ULPI OUTPUT CLOCK MODE, 24MHZ(★)

3.6、USB3320设计注意事项

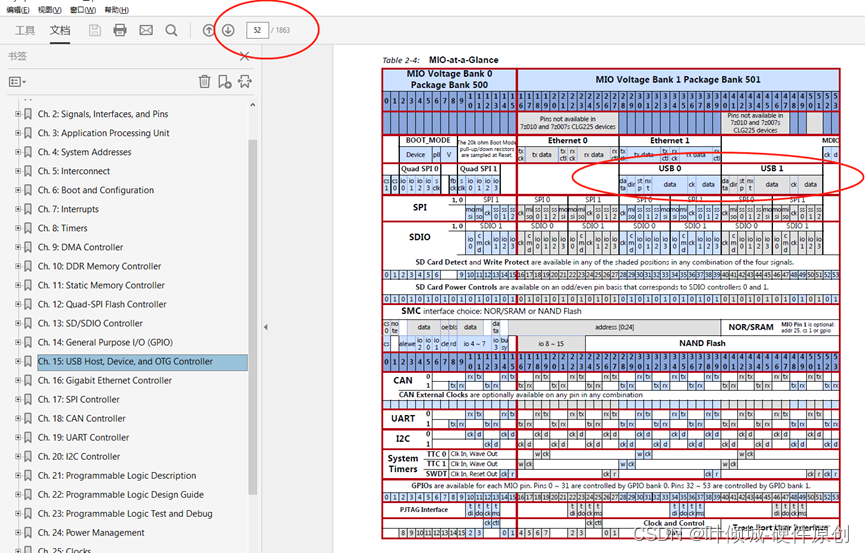

1、对于ZYNQ70XX来说。参考《ug585-Zynq-7000-TRM------全》 P52

USB3320放置在PS端的bank 501端时,注意严格按照下图参考!!!

3.7、USB3320硬件实战(★)

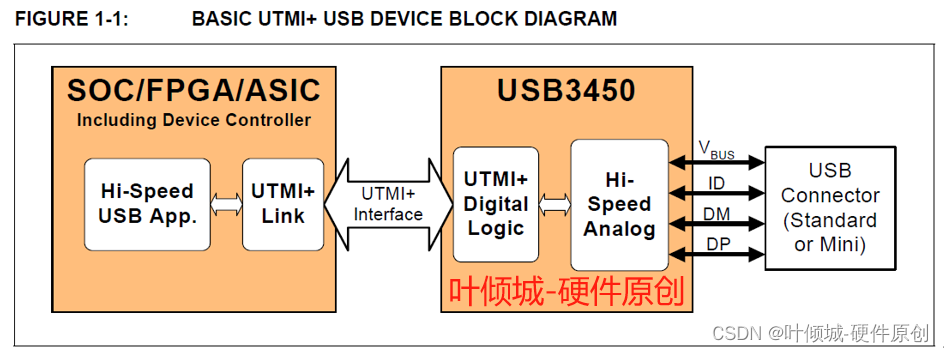

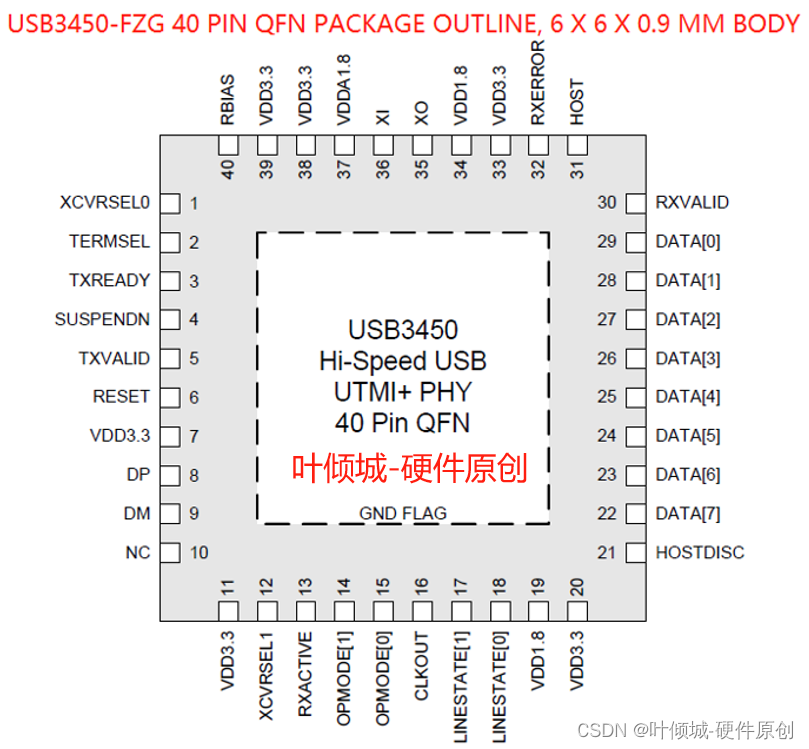

4、UTMI+接口详解(以USB3450为例)

USB3450是一个独立的高速USB物理层收发器(PHY)。USB3450使用UTMI+接口连接FPGA或者SOC。

4.1、UTMI信号接口

UTMI接口信号

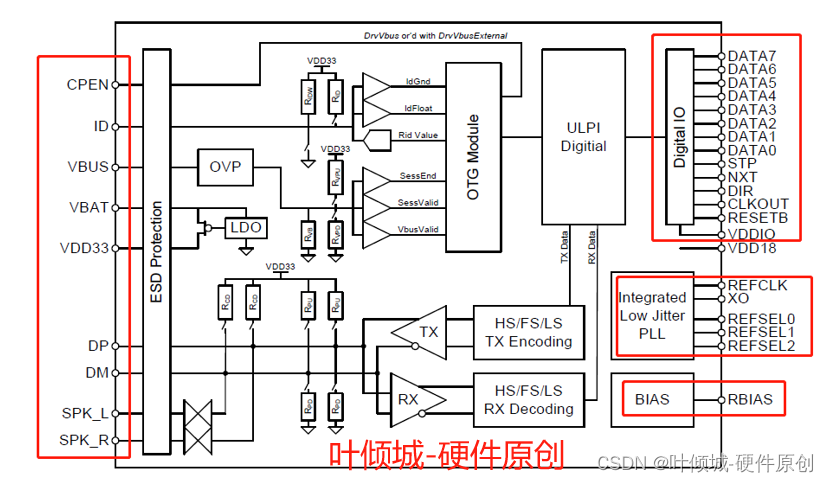

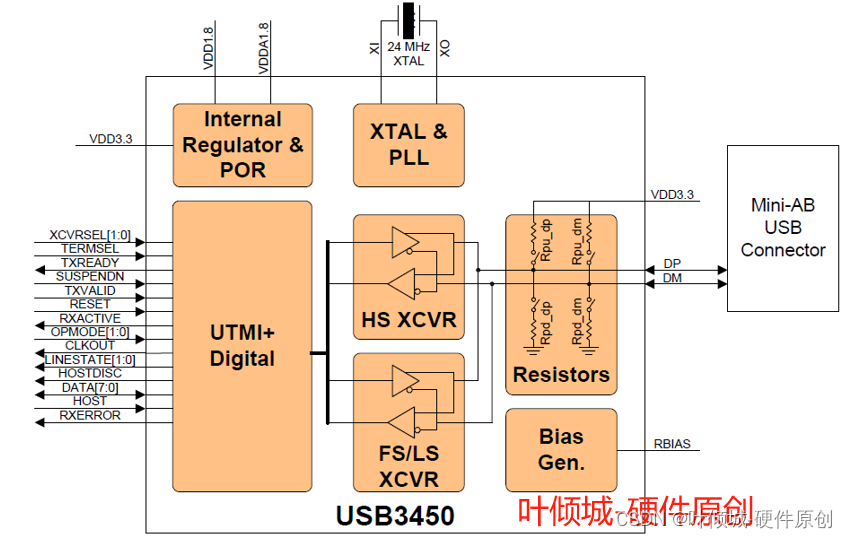

4.2、结构及功能框图

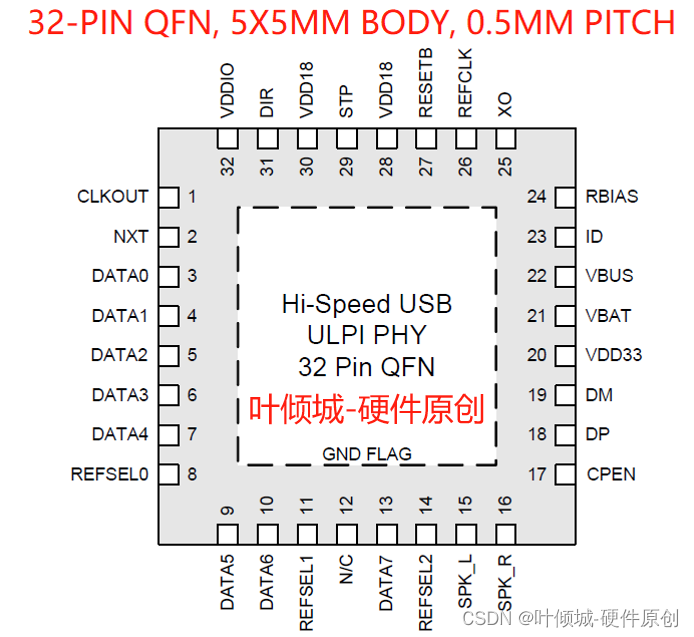

4.3、管脚定义(USB3450)

对于电源电压。

| 管脚符号 | 类型 | 描述 |

| VDD3.3 | Power | 3.3V PHY Supply. 3.3V PHY Supply. Provides power for Hi-Speed Transceiver, UTMI+ Digital, Digital I/O, and Regulators. 3.3V PHY供应。提供电源高速收发器,UTMI+数字,数字I/O,和调节器。 |

| VDD1.8 | Power | 1.8V regulator output for digital circuitry on chip. 芯片上数字电路1.8V稳压器输出。 |

| VDDA1.8 | Power | 1.8V regulator output for analog circuitry on chip. 芯片上模拟电路的1.8V稳压器输出。 |

| GND | Ground | 地 |

| GND FLAG | Ground | Ground. The flag must be connected to the ground plane. |

| 管脚符号 | 类型 | 描述 |

| DP | I/O Analog | D+ pin of the USB cable. |

| DM | I/O Analog | D- pin of the USB cable. |

| DATA[7:0] | I/O | 8-bit bi-directional data bus. |

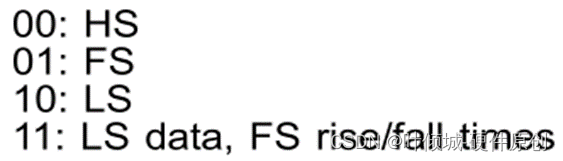

| XCVRSEL[1:0] | Input | Transceiver Select.

|

| TERMSEL | Input | Termination Select. |

| TXREADY | Output /High | Transmit Data Ready. |

| SUSPENDN | Input /Low | Suspend. |

| TXVALID | Input /High | Transmit Valid. Indicates that the DATA bus is valid for transmit. 传输有效。表示数据总线对传输是有效的。 |

| RXACTIVE | Output /High | Receive Active. |

| OPMODE[1:0] | Input | Operational Mode. |

| CLKOUT | OUT | 60MHz reference clock output. |

| LINESTATE [1:0] | Output | Line State. |

| HOSTDISC | Output / High | Host Disconnect. |

| RXVALID | Output /High | Receive Data Valid. |

| HOST | Input | Host Pull-down Select. |

| RXERROR | Output /High | Receive Error. |

| XO | Output Analog | Crystal pin. If using an external clock on XI this pin should be floated. |

| XI | Input Analog | Crystal pin. |

| RBIAS | Analog CMOS | External 1% bias resistor. Requires a 12KΩ resistor to ground. |

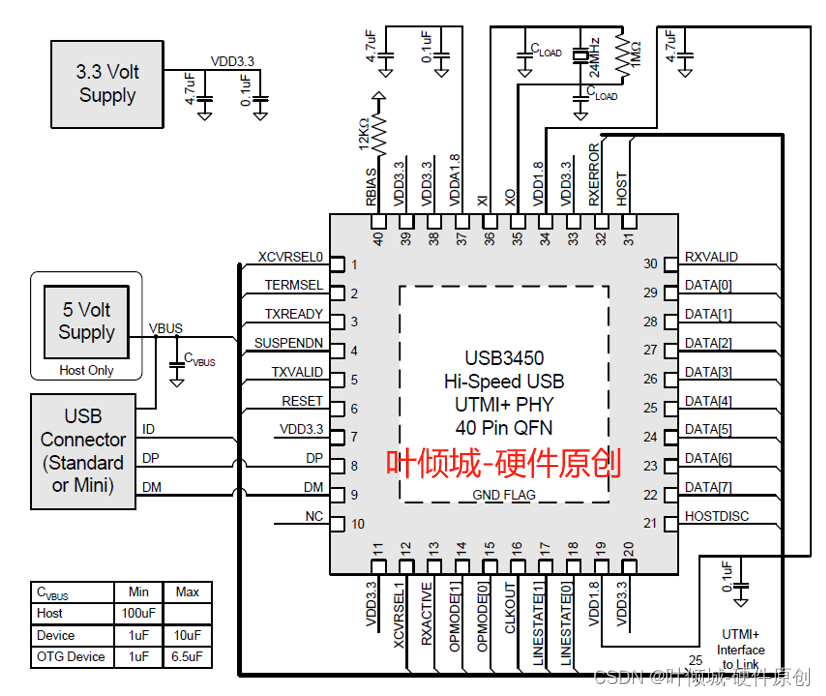

4.4、USB3450应用框图

4.5、USB3450设计注意事项

4.6、USB3450硬件实战

5、HSIC (USB 2.0 High Speed Inter Chip)

HSIC(高速芯片间)是USB芯片间互连的行业标准,具有2信号(选通,数据)源同步串行接口,使用240 MHz DDR信令仅提供高速率。

HSIC (USB 2.0 High Speed Inter Chip)。是USB 2.0的芯片到芯片变体,它消除了普通USB中的传统模拟收发器。速度可达480M,是IIC的理想替代。

6、USB layout设计要求

6.1、布局要求

1、USB接口靠近板边放置,避开其他高速信号

2、ESD保护器件和Common mode choke(共模电感、共模扼流圈)应该尽可能的靠近USB接口放置。

3、USB转换芯片与USB连接器应该尽可能的靠近,以减少走线的长度。其晶振不可放置过远,2个防漂移电容放晶振旁边。

4、用于去耦和消除高频噪声干扰的磁珠和去耦电容应该尽可能的靠近USB连接器放置。

5、USB电压稳压器尽可能靠近连接器放置。

6.1、布线要求

1、USB差分阻抗控制:USB2.0/USB3.0——90Ω(±10%),对内等长误差2mil。

2、USB差分信号尽量以完整的地平面为参考平面;

3、USB差分信号与其他时钟、高速信号保持至少5W以上间距。

4、USB电源线尽量粗,最好采用铺铜处理,USB2.0为0.5A,USB3.0为1A。并且机壳地与板内地的短接电感两端采用铺铜处理。

5、USB的转换芯片上的DATA[0-7],CLKOUT,DIR,NXT,STP控制同层等长,等长误差5mil。

964

964

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?