目 录

1.1 导入dxf结构图(画outline、设置routkeepin) 6

3.1 高速PCB设计之allegro如何导出库和应用物理库 7

第九章 layout走线(信号线 & 电源线)(★).. 11

9.5 orcad管脚交换---swap pin设置及注意事项 12

11.4 高速PCB设计之dangling lines and dangling vias删除了没? 13

15.1 allegro 17.2转16.6一键降版本 14

★模块化篇 ---模块化layout设计(第4章布局 & 第9章布线) 15

★通用篇 PCB设计前基础工作

1、高速PCB设计集合片头及layout流程

链接:高速PCB设计集合片头及layout流程_哔哩哔哩_bilibili

2、allegro如何导出库和应用物理库

链接:高速PCB设计之allegro如何导出库和应用物理库_哔哩哔哩_bilibili

3、env快捷键设置

链接:高速PCB设计之env快捷键设置_哔哩哔哩_bilibili

4、高速PCB设计之手势快捷键设置

链接:高速PCB设计之手势快捷键设置_哔哩哔哩_bilibili

5、Allegro-skill浅谈

链接:Allegro-skill浅谈_哔哩哔哩_bilibili

第一章 导入dxf结构图

1.1 导入dxf结构图(画outline、设置routkeepin)

《高速PCB设计之根据尺寸结构建板框》

链接:高速PCB设计之根据尺寸结构建板框_哔哩哔哩_bilibili

《高速PCB设计之坐标原点设置》

链接:

第二章 导入网表

《高速PCB设计之原理图和PCB交互》

链接:高速PCB设计之原理图和PCB交互_哔哩哔哩_bilibili

高速PCB设计之---pdf原理图和PCB交互

链接:高速PCB设计之---pdf原理图和PCB交互_哔哩哔哩_bilibili

第三章 放入元器件

3.1 高速PCB设计之allegro如何导出库和应用物理库

《高速PCB设计之allegro如何导出库和应用物理库》

链接:高速PCB设计之allegro如何导出库和应用物理库_哔哩哔哩_bilibili

第四章 根据原理图模块布局(★)

《高速PCB设计之相同模块布局》

链接:高速PCB设计之相同模块布局_哔哩哔哩_bilibili

《高速PCB设计之元器件定位及移动》

链接:高速PCB设计之元器件定位及移动_哔哩哔哩_bilibili

4.3.1 布局基本原则

4.3.2 元器件的设计间距要求

第五章 根据飞线、电源等布局元器件布局调整

第六章 提交阻抗表(工厂计算反馈)

在与客户确认好板中重要信号阻抗要求以后,根据层数、等级、板厚、基材、阻抗要求等提交阻抗需求。针对高速电路板,在阻抗计算时,可以根据板中实际情况提出一些附加需求,便于设计以及提高信号完整性。

6.1.1 层数预估

6.1.2 板厚

6.1.3 基材

第七章 设置走线规则、叠层等(★)

7.1.1 单线规则设置

7.1.2 差分规则设置

7.1.3 电源规则设置

7.1.4 BGA规则设置(走线的时候再设置)

第八章 扇孔

8.1.1 一般扇孔

8.1.2 BGA扇孔

第九章 layout走线(信号线 & 电源线)(★)

9.2.1 PCB布线的基本原则

9.2.2 布线的基本顺序

9.2.3 圆弧走线

Allegro隐藏电源飞线

链接:https://www.bilibili.com/video/BV1dC4y1S7iS

《高速PCB设计之走线COPY》

链接:高速PCB设计之走线COPY_哔哩哔哩_bilibili

9.5 orcad管脚交换---swap pin设置及注意事项

《orcad管脚交换---swap pin设置及注意事项01》

链接:https://www.bilibili.com/video/BV1ST41137c1

《orcad管脚交换---pin swap report 02》

链接:orcad管脚交换---pin swap report 02_哔哩哔哩_bilibili

高速PCB设计之多人协同设计

链接:高速PCB设计之多人协同设计_哔哩哔哩_bilibili

第十章 内电层分割(★)

10.1.1 地层

10.1.2 电源层

10.1.3 内缩20H

高速PCB设计之20H做了没?

链接:高速PCB设计之20H做了没?_哔哩哔哩_bilibili

第十一章 DRC设置及检查(★)

《高速PCB设计之差分对对内耦合性检查》

链接:高速PCB设计之差分对对内耦合性检查_哔哩哔哩_bilibili

《高速PCB设计之阻焊层和助焊层检查》

链接:高速PCB设计之阻焊层和助焊层检查_哔哩哔哩_bilibili

11.4 高速PCB设计之dangling lines and dangling vias删除了没?

高速PCB设计之dangling lines and dangling vias删除了没?

链接:高速PCB设计之dangling lines and dangling vias删除了没?_哔哩哔哩_bilibili

高速PCB设计之单点检查

第十二章 调丝印

12.1.1 元器件丝印

12.1.2 图标、静电标识放置

高速PCB设计之看谁丝印调的快?

链接:高速PCB设计之看谁丝印调的快?_哔哩哔哩_bilibili

高速PCB设计之一键导入汉字

链接:高速PCB设计之一键导入汉字_哔哩哔哩_bilibili

高速PCB设计之一键导入图片及缩放

链接:高速PCB设计之一键导入图片及缩放_哔哩哔哩_bilibili

第十三章 最终检

13.1.1 是否满足PCB设计要求

13.1.2 是否满足电源设计要求

13.1.3 是否满足信号设计要求

第十四章 出投产数据

高速PCB设计之添加光绘及出geber文件

链接:高速PCB设计之添加光绘及出geber文件_哔哩哔哩_bilibili

第十五章 其他

allegro 17.2转16.6一键降版本

链接:allegro 17.2转16.6一键降版本_哔哩哔哩_bilibili

Allegro导出dxf别忘记加载一数据

链接:Allegro导出dxf别忘记加载一数据_哔哩哔哩_bilibili

★模块化篇 ---模块化layout设计(第4章布局 & 第9章布线)

电路功能模块布线

1 千兆以太网(RGMII)

千兆以太网(RGMII)Layout设计01_哔哩哔哩_bilibili

2 千兆以太网(SGMII)

千兆以太网(SGMII)layout设计01_哔哩哔哩_bilibili

3 万兆以太网

4 RS232 (DB9 & Console)

RS232 (DB9 & Console)layout设计01_哔哩哔哩_bilibili

5 RS485

RS232 (DB9 & Console)layout设计01_哔哩哔哩_bilibili

6 CAN

7 HDMI

8 DP

9 时钟

10 SPI Flash

SPI flash layout设计01_哔哩哔哩_bilibili

11 MICRO SD & eMMC

Micro SD & eMMC layout设计01_哔哩哔哩_bilibili

12 DDR3 & DDR4

DDR3 & DDR4 layout设计01_哔哩哔哩_bilibili

13 DDR3 & DDR4 SODIMM

DDR3 & DDR4 SODIMM layout设计01_哔哩哔哩_bilibili

14 SDRAM

15 NOR FLASH & NAND FLASH

16 USB 2.0 & 3.0

17 SATA & mSATA

18 M.2

19 PCIE

20 …

电源布局布线

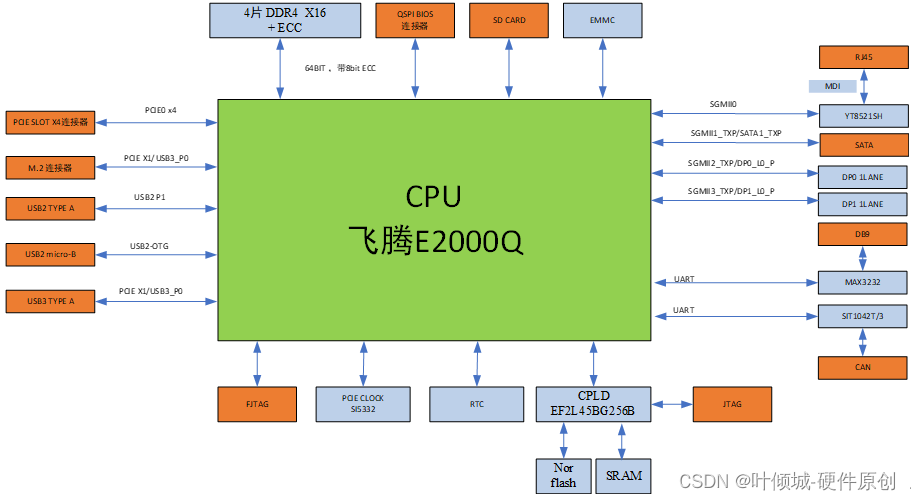

★实战篇 ---基于飞腾E2000Q的一站式PCB Layout设计

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?