实验要求:使用50M的系统时钟分别产生一路12位的10KHZ的正弦波和余弦波

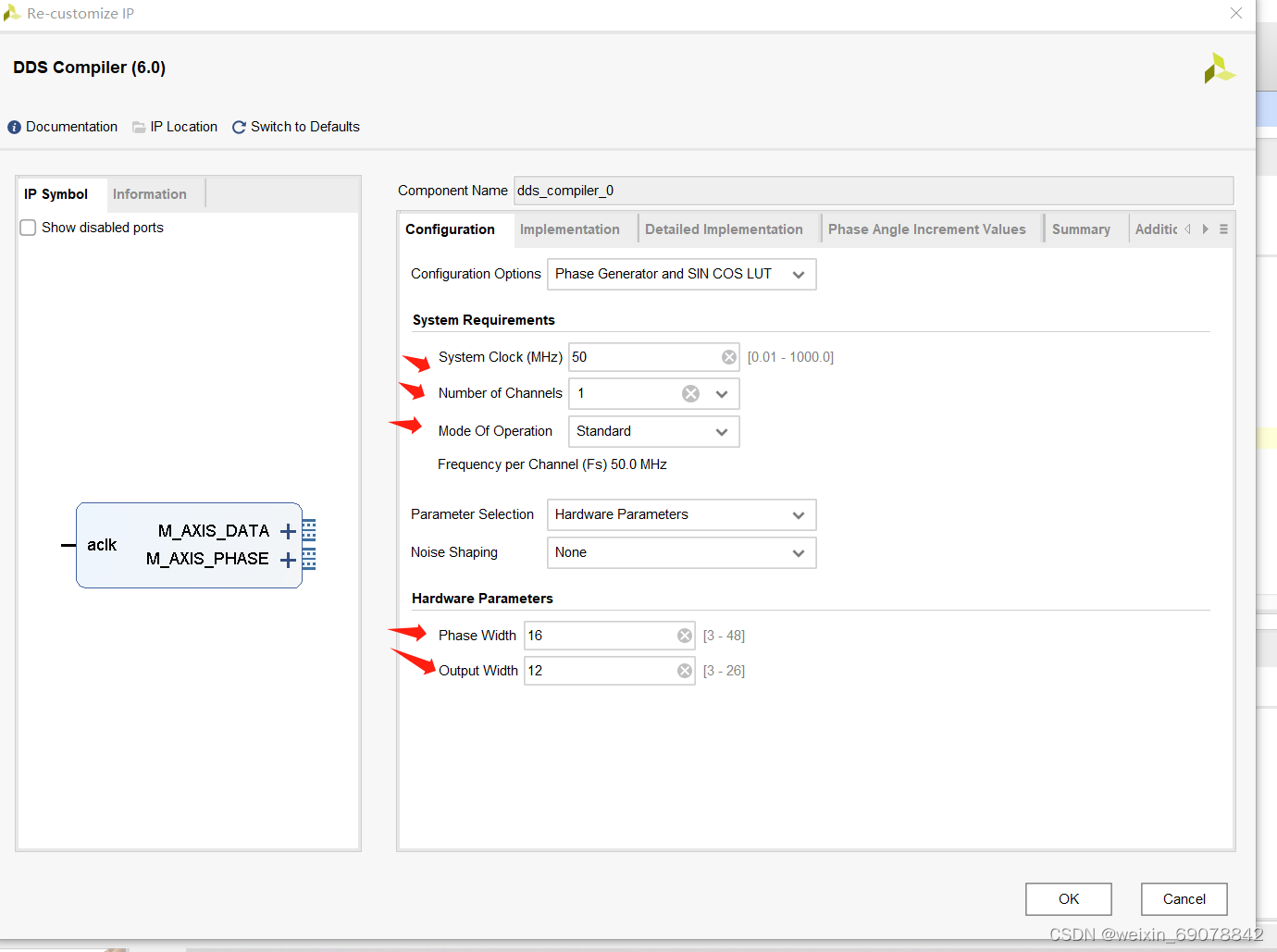

第一步:打开DDS ip核

Configuration Options: 选择有Sin和Cos模式

System Clk:选择50MHz

Mode Of Operation:这里可以有两种选择Standard模式和Rasterized模式

在Standard模式下:填写Phase width(相位位宽): 默认16位不变,填写Output width为实验要求的12位;

利用公式 计算:10K=50M*ΔΦ(频率控制字又名相位增量)/2^16(Phase width)即10K=50M*ΔΦ/2^16 计算得到ΔΦ。

计算:10K=50M*ΔΦ(频率控制字又名相位增量)/2^16(Phase width)即10K=50M*ΔΦ/2^16 计算得到ΔΦ。

Phase Increament Programmability 这里选择fix(固定值)。

填入四舍五入后的ΔΦ的值(转化为二进制)。

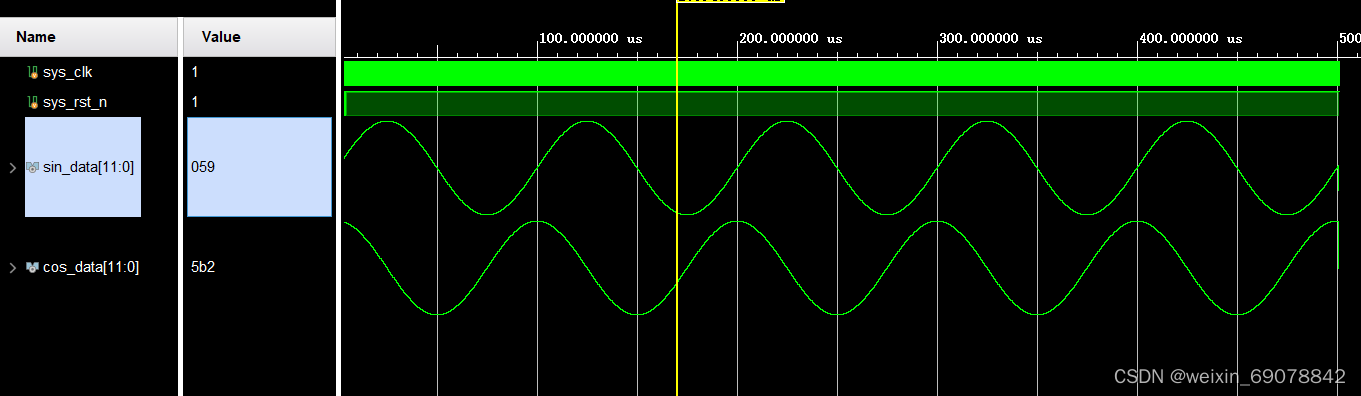

后续通过仿真查看波形。

存在的问题:因为是四舍五入后的ΔΦ,所以产生的波形只是大致10K但是不准确,采取第二种模式。

选择Rasterized模式,这里发现Phase Width已经固定了,需要我们填入Modulus 的值

利用公式:

![]()

这里发现这个公式利用M的值代替了前面2^16(Phase width)的值,所以这里我们只需要自己定义ΔΦ/M的值就可以输出fout。 这里定义了10K=50M*ΔΦ/M。令M=10000,那么ΔΦ=2。

在这里填入10。

没有提到的地方都用默认。

测试代码:

module dds(

input sys_clk,

input sys_rst_n,

output [11:0]sin_data,

output [11:0]cos_data

);

wire [31:0]data;

wire [15:0]phase_data;

wire phase_valid;

wire data_valid;

assign cos_data={~data[11],data[10:0]};

assign sin_data={~data[27],data[26:16]};

dds_compiler_0 your_instance_name (

.aclk(sys_clk), // input wire aclk

.m_axis_data_tvalid(data_valid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(data), // output wire [31 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(phase_valid), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(phase_data), // output wire [15 : 0] m_axis_phase_tdata

.event_pinc_invalid( ) // output wire event_pinc_invalid

);

endmodule

Note:最高位要取反才能得到连续的正余弦波。

仿真代码:

`timescale 1ns/1ns

module tb_dds(

);

reg sys_clk;

reg sys_rst_n;

initial begin

sys_clk<=1'b0;

sys_rst_n<=1'b0;

#20

sys_rst_n<=1'b1;

end

always #10 sys_clk=~sys_clk;

wire [11:0]sin_data;

wire [11:0]cos_data;

dds u_dds(

.sys_clk (sys_clk) ,

.sys_rst_n (sys_rst_n ),

.sin_data (sin_data),

.cos_data (cos_data)

);

endmodule

使用第二种模式能够得到周期更精确的正余弦波。

欢迎评论指正,交流学习!

6968

6968

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?