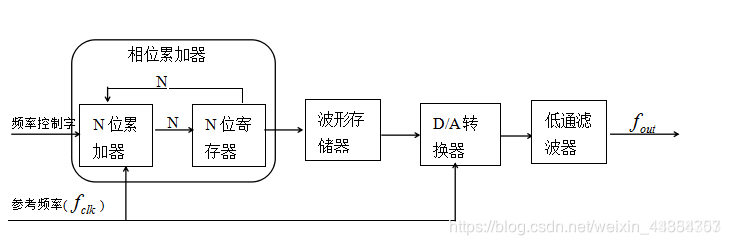

DDS三大组成部分:频率控制字、相位累加器、rom查找表

1.新建工程

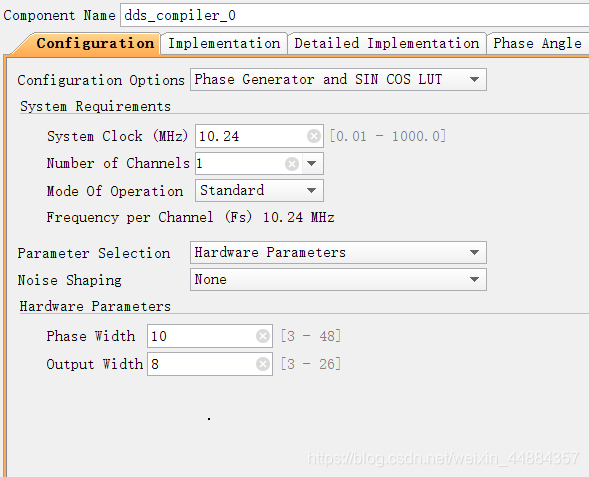

2.选择IP catalog(目录),选择dds compiler(编译),系统时钟选择板子时钟,例如10.24M。

3.parameter selection 选择 有两种,如果选择hardware parameters,phase width选择10位,输出8位。

这里,如果输出为sin &cos的话,那么设置的输出8位指的是一个sin为8位,所以一共16位,输出的高8位为cos,低8位为sin.

如果选择 system parameters:通过控制无杂散动态范围(Spurious Free Dynamic Range,SFDR)的数值,可以调整正弦和余弦输出数据的数据位宽,这里设置为47,则正余弦输出为8位。,这个可以这样来估计,若正余弦位数要求为n位,则这里的值应是(6n-6,6n】中的任意一个数。(n20log10(2)=6.0206*n dB

频率分辨率,频率分辨率范围可以由设计的相位累加字位宽n得到。为【fsys/2^ n ,fsys/2^(n-1))。设置为10000,可以看出当频率分辨率设置好后,DATA的数据位宽变为10位。

configuration options 如果设置为 phase generator and sin cos lut,则模块例化输入的量是:

.s_axis_config_tvalid(fre_word_en), // input wire s_axis_config_tvalid

.s_axis_config_tdata(fw_z), // input wire [15 : 0] s_axis_config_tdata

这里输入量是频率控制字。

如果设置为sin cos lut only,输入量是:

.s_axis_phase_tvalid(1'd1),

.s_axis_phase_tdata(fword_sum_acc[31:24]),

这里的输入量是相位累加器中的值。

4.相位增量值可编程,相位初值none.has phase pout 点掉

这里:相位增量是否支持可编程配置

Fixed是固定相位增量,DDS运行过程中不可更改,即对应不可变频率;

Programmable可编程,选中后出现配置接口,可在DDS运行过程中随时写入频率控制字改变输出波形的频率,用于偶尔改变频率;

Streaming应用于频繁改变频率,,比如锁相环本地nco经常改变

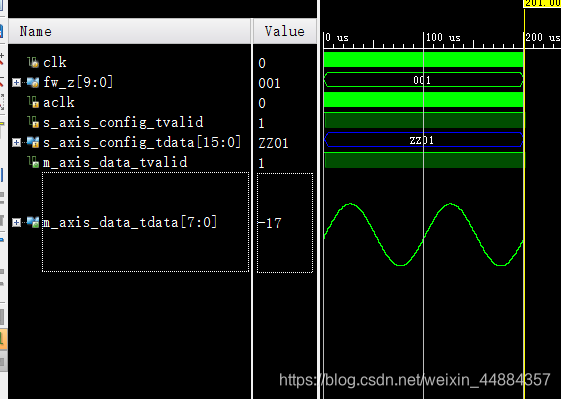

接下来就是例化IP核,首先是时钟分频模块,双击dds的.v文件),将接口程序复制到主程序中去

`timescale 1ns / 1ps

//

// Company:

// Engineer: llllll

//

// Create Date: 2020/03/21 18:48:43

// Design Name:

// Module Name: aa

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module aa ( input sysclk,

input [9:0] fw_z

);

wire [9:0] fw_z;

wire fre_word_en;

assign fre_word_en = 1'b1;

wire [7:0] dds_out;

dds_compiler_0 hhh(

.aclk(sysclk), // input wire aclk

.s_axis_config_tvalid(fre_word_en), // input wire s_axis_config_tvalid

.s_axis_config_tdata(fw_z), // input wire [15 : 0] s_axis_config_tdata

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(dds_out) // output wire [7 : 0] m_axis_data_tdata

);

endmodule

tb文件

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/03/21 19:01:00

// Design Name:

// Module Name: tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tb(

);

reg clk;

// wire [7:0] data;

reg [9:0] fw_z;

aa dut1(

.sysclk(clk),

.fw_z(fw_z)

// .led(data)

);

// 初始化

initial

begin

clk = 0;

fw_z = 10'b0000000001;

end

//产生10.24MHz时钟信号

always

begin

#49 clk = ~clk;

end

endmodule

execute 处理执行

synthesis 综合

implementation

9163

9163

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?