目录

1、IP介绍

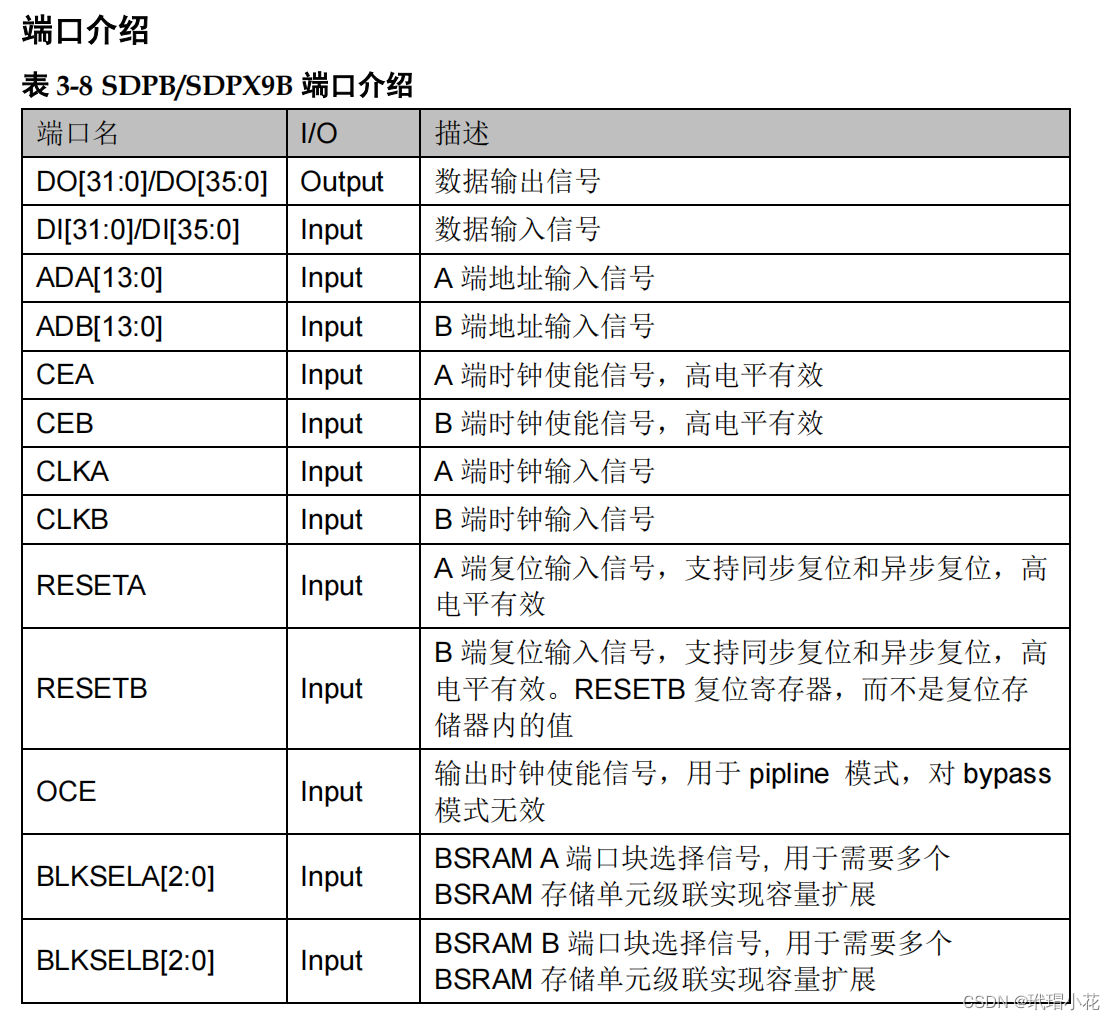

SDPB/SDPX9B 存储空间分别为 16K bit/18K bit,其工作模式为伪双端 口模式,端口 A 进行写操作,端口 B 进行读操作,可支持 2 种读模式 (bypass 模式和 pipeline 模式)和 1 种写模式(normal 模式)。

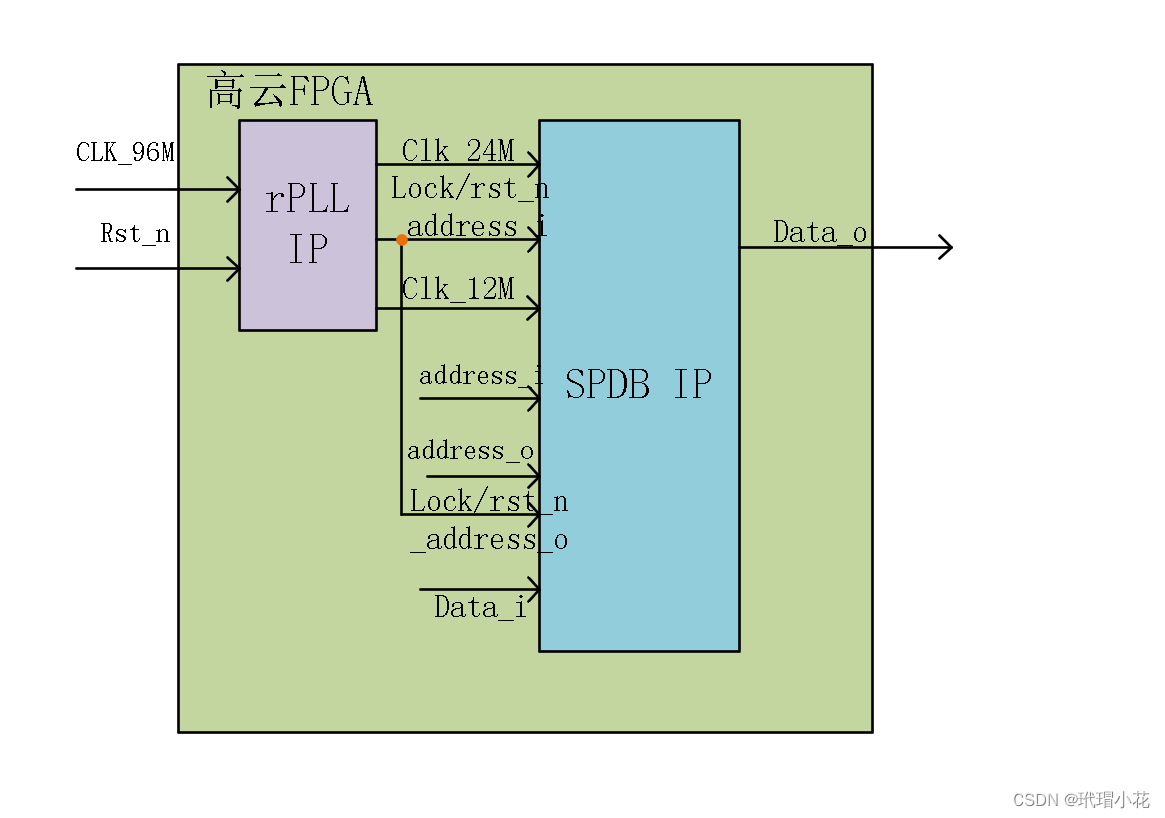

2、设计思路

调了一个rPLL(高云在调用PLL界面会提示rPLL性能更好,所以就调用的rPLL)和SDPB。整个设计输入只有复位和时钟,输出读的SDPB数据。我同事教我的一个小思路,把复位给到rPLL而全局的复位信号用rPLL输出的lock信号来控制,这样只要时钟出现不稳定就会复位。写地址、写数据、读地址都由顶层文件产生。

Clk_24m:SPDB写数据时钟;

Clk_12m:SPDB读数据时钟;

Lock/rst_n_address_i:写数据复位,这是rPLL 的lock信号;

Lock/rst_n_address_o:读数据复位,这是rPLL 的lock信号;

address_i:写数据地址;

address_o:读数据地址;

Data_i:写数据;

CE和OCE信号直接给1,就没有写出来。

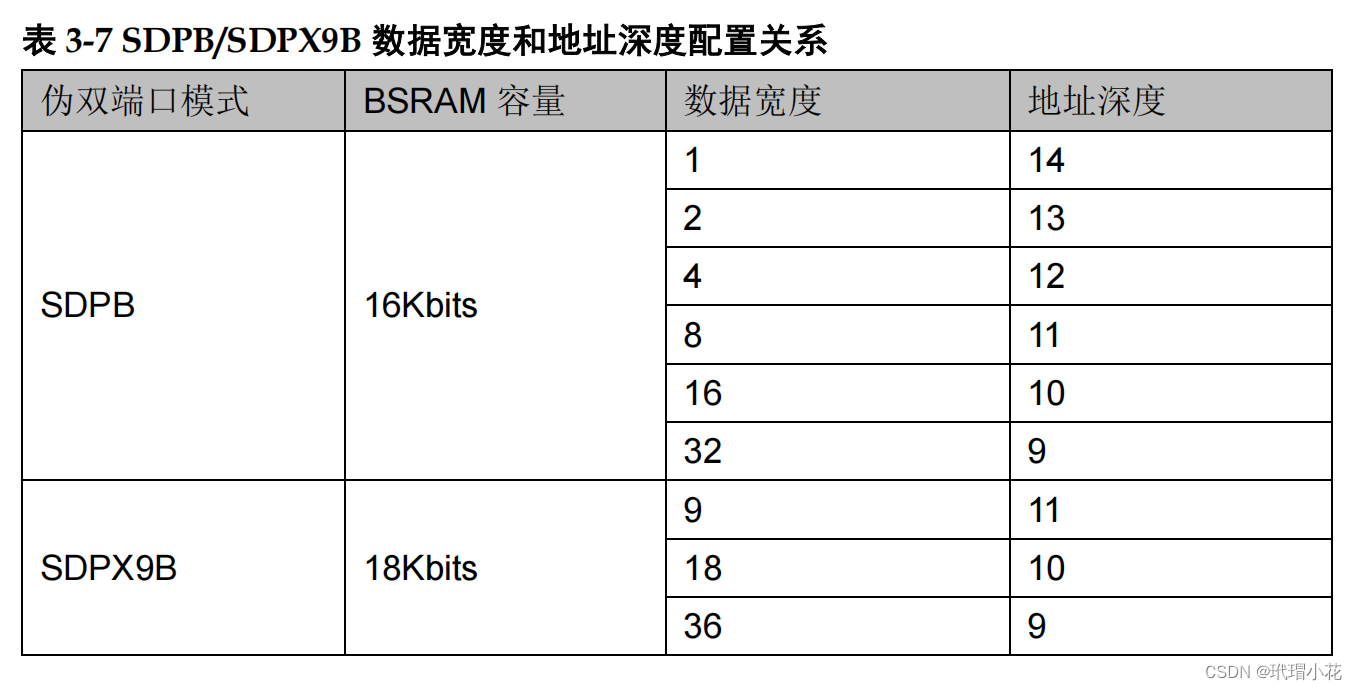

3、数据深度与宽度配置关系

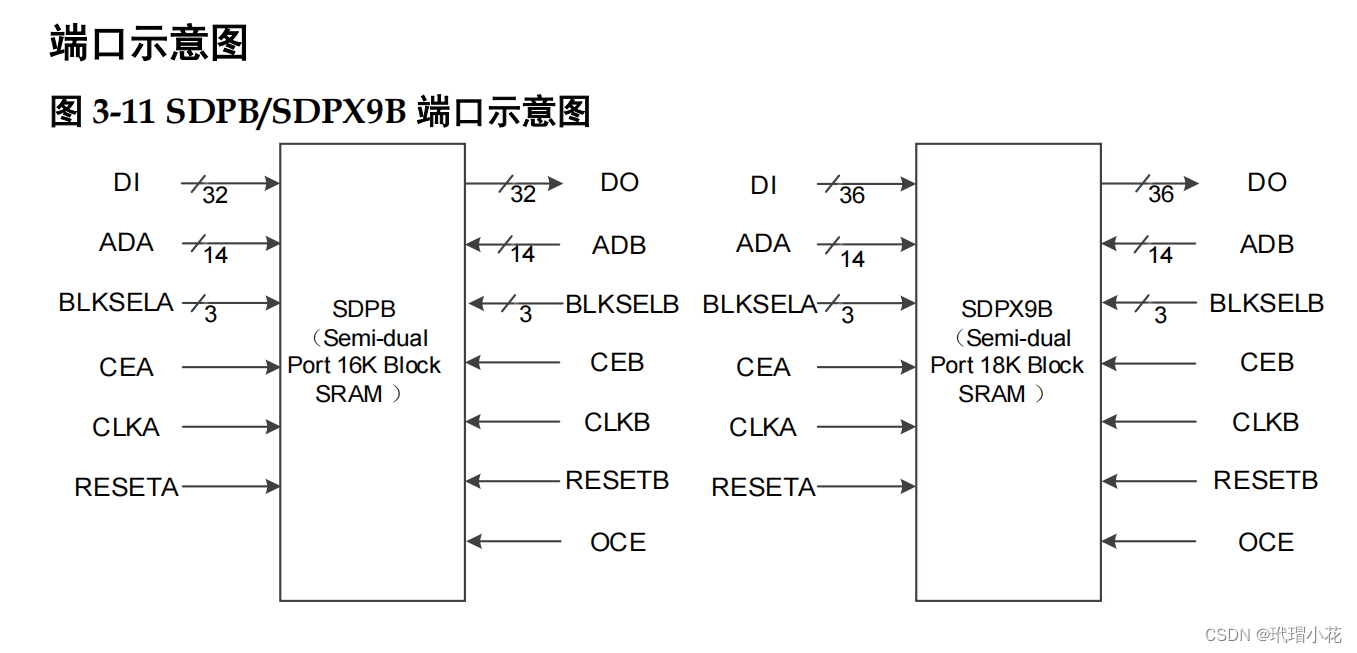

4、端口示意图

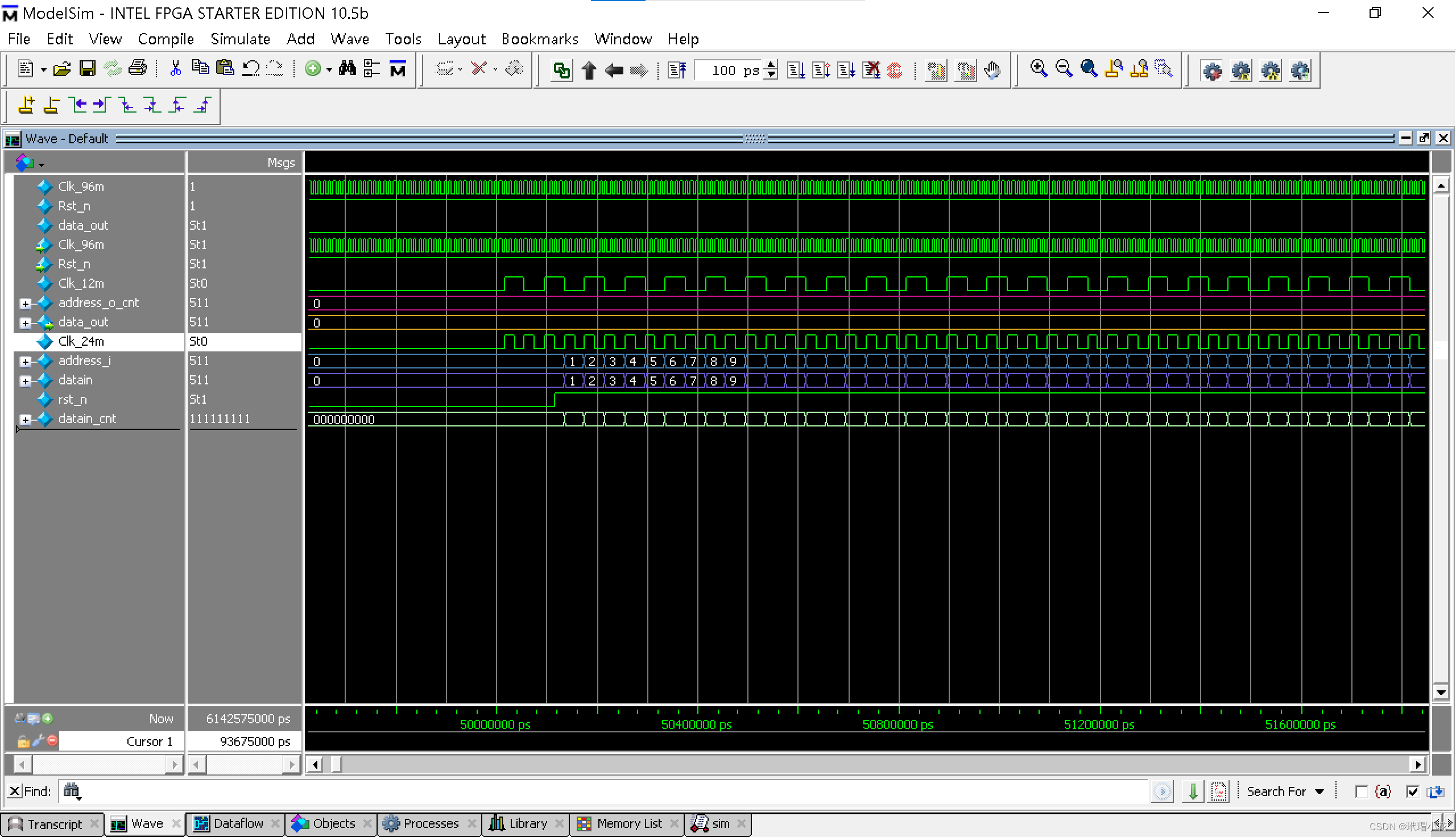

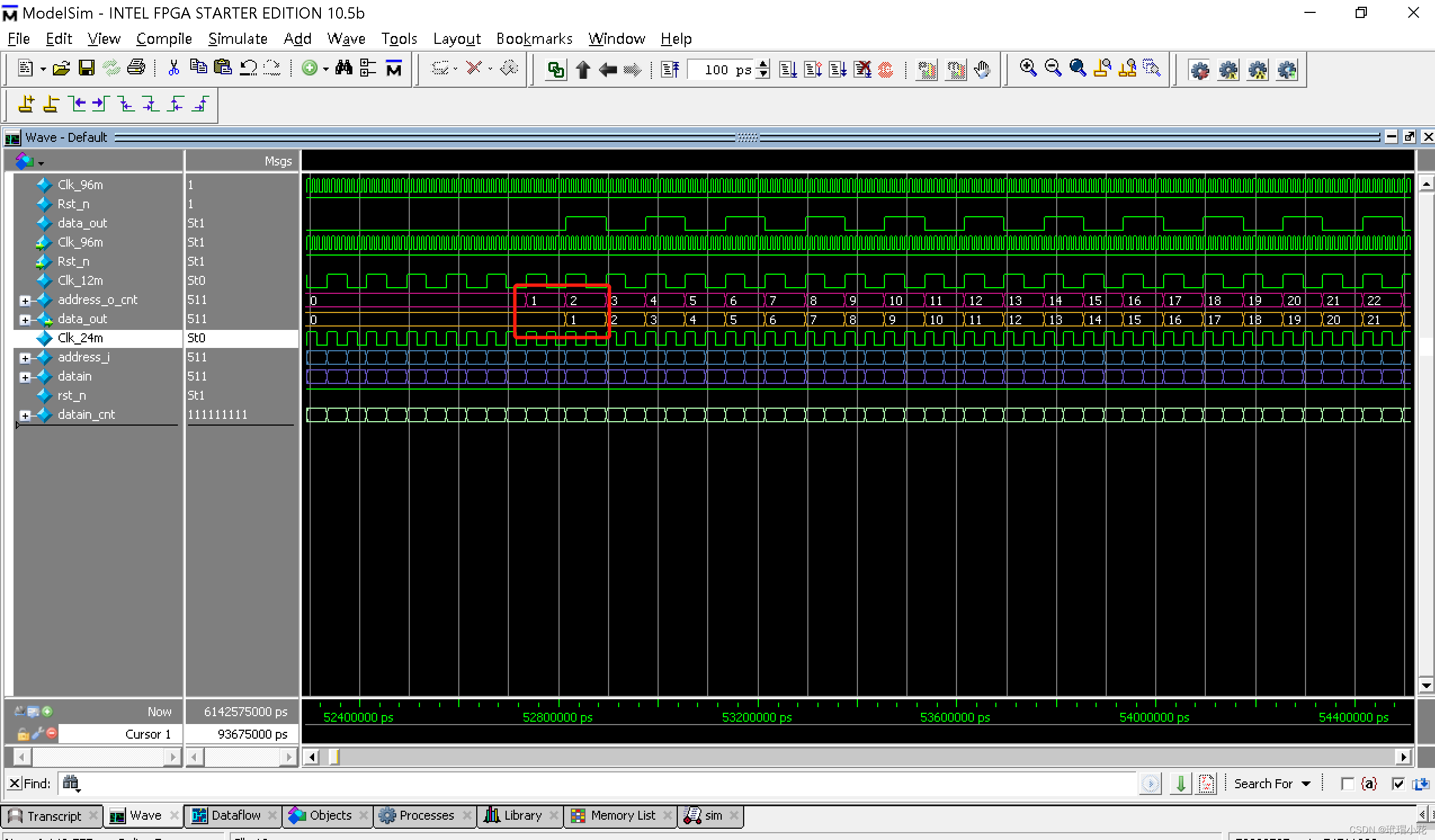

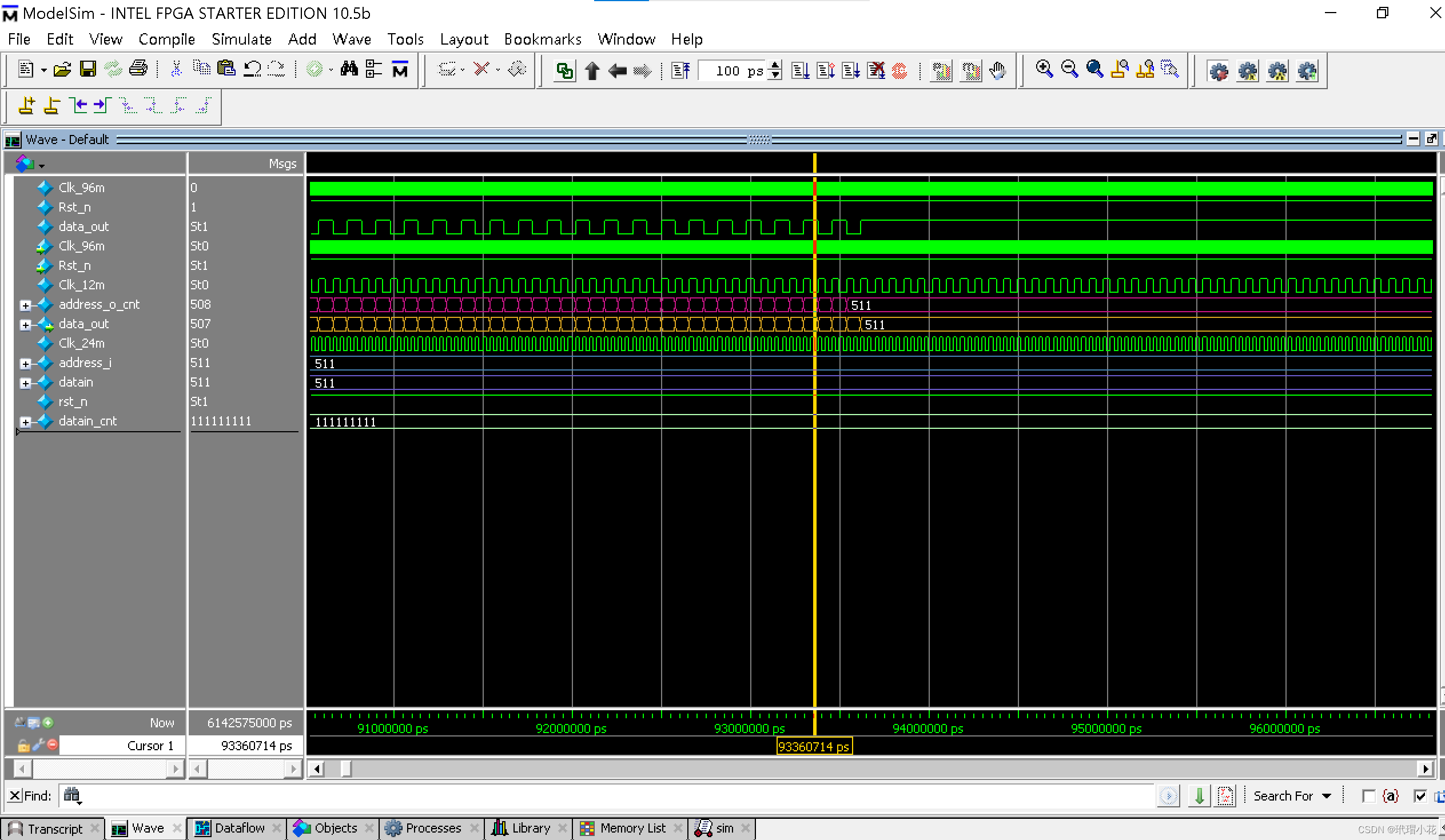

5、仿真

读数据会晚读地址一个时钟

6、代码

/* ================================================ *\

Filename ﹕

Author ﹕ jie

Description ﹕

Called by ﹕

Revision History ﹕ 2023/6/7

Revision 1.0

Email﹕ 1323299504@qq.com

Company﹕ AWCloud

\* ================================================ */

module test_sdpb(

input Clk_96m , //system clock 96MHz

input Rst_n , //reset, low valid

output [31:0] data_out //

);

//Internal wire/reg declarations

reg [8:0] datain_cnt;

wire [31:00] datain;

wire [8:0] address_i;

reg [8:0] address_o_cnt;

wire rst_n;

//Module instantiations , self-build module

Gowin_rPLL U_rPLL(

.reset(~Rst_n), //input reset

.clkin(Clk_96m), //input clkin

.clkout(Clk_24m), //output clkout 24m

.clkoutd(Clk_12m), //output clkoutd 12m

.lock(rst_n) //output lock

);

//Logic Description

always @(posedge Clk_24m or negedge rst_n)begin

if(~rst_n)

datain_cnt <= 9'd0;

else if(datain_cnt >= 9'd511)

datain_cnt <= datain_cnt;

else

datain_cnt <= datain_cnt + 1'd1;

end

assign datain = { {23{1'b0}}, datain_cnt };

assign address_i = datain_cnt;

always @(posedge Clk_12m or negedge rst_n)begin

if(~rst_n)

address_o_cnt <= 9'd0;

else if(address_o_cnt == 'd511)

address_o_cnt <= address_o_cnt;

else if(datain_cnt>=9'h040)

address_o_cnt <= address_o_cnt + 1'd1;

end

Gowin_SDPB U_SDPB(

.reseta(!rst_n), //input reseta

.resetb(!rst_n), //input resetb

.oce(1'd1), //input oce

//**************************************//

.clka(Clk_24m), //input clka

.cea(1'd1), //input cea

.ada(address_i), //input [8:0] ada

.din(datain), //input [31:0] din

//**************************************//

.clkb(Clk_12m), //input clkb

.ceb(1'd1), //input ceb

.adb(address_o_cnt), //input [8:0] adb

.dout(data_out) //output [31:0] dout

);

endmodule

1795

1795

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?