伪双口RAM从灵活度上来说,刚好介于单口RAM和真双口RAM之间,但是不得不说它是RAM中应用最广的配置类型,其难能可贵地兼顾了真双口RAM的读写灵活性,也兼顾了单口RAM的设计稳定性。因为伪双口RAM只有一个端口可以向地址中写入数据,而另外一个端口只可以从地址中读出数据,所以这既避免了真双口RAM的大概率性读写冲突的窘境,也完善了单口RAM无法同时读写地址的缺陷。

在这个练习中去用伪双口RAM IP来实现异步时钟FIFO的功能,用RAM来实现FIFO,这也是RAM在工程项目当中非常重要的一个应用,看到这里有些同学可能会问明明已经有现成的FIFO IP核了,为何还需要多此一举再用RAM模拟FIFO的功能呢,通过前面的博客学习实践,其实大家也已经逐渐掌握了FIFO和RAM之间的异同点以及适用背景,这里用RAM来实现FIFO的功能在工程应用中可以弥补了FIFO不能重复读出数据、和不能覆盖数据的缺陷,可以理解成升级版的FIFO。

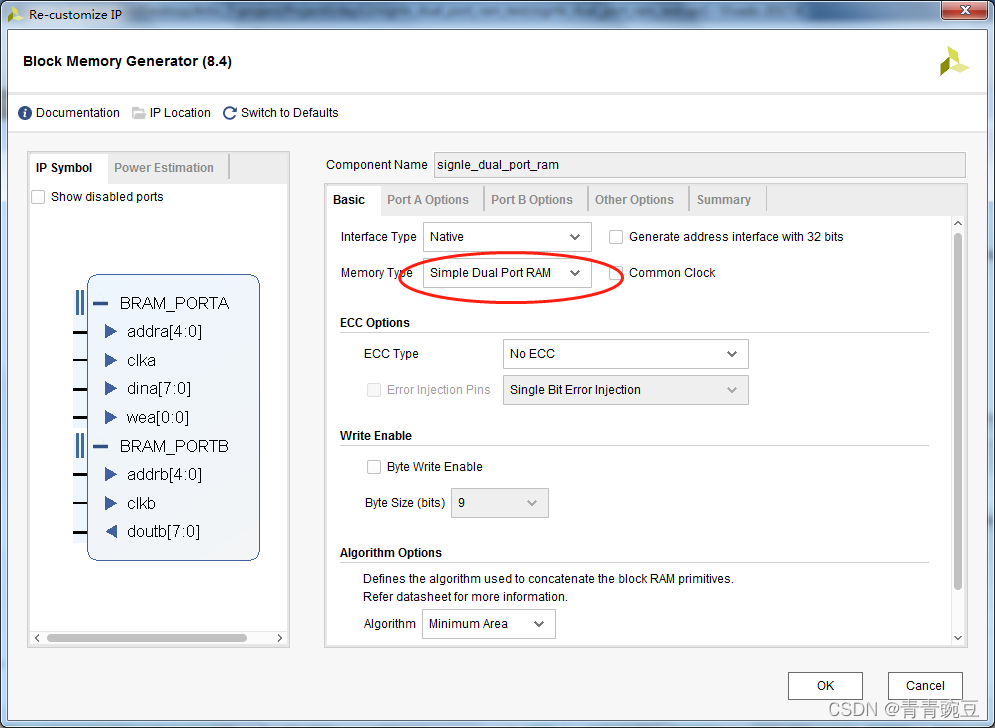

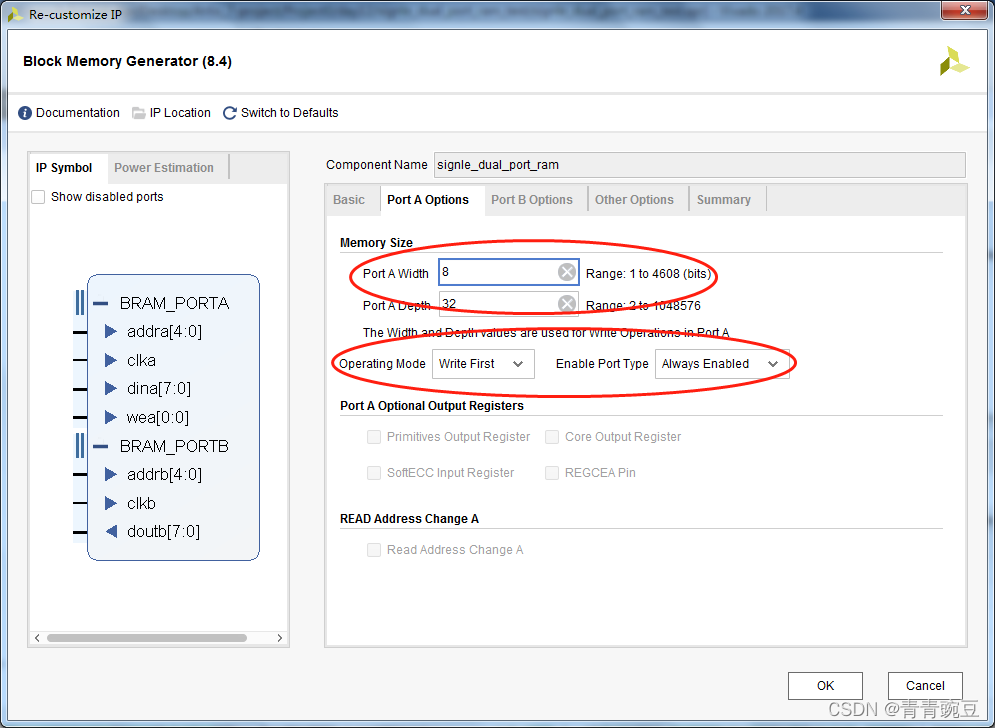

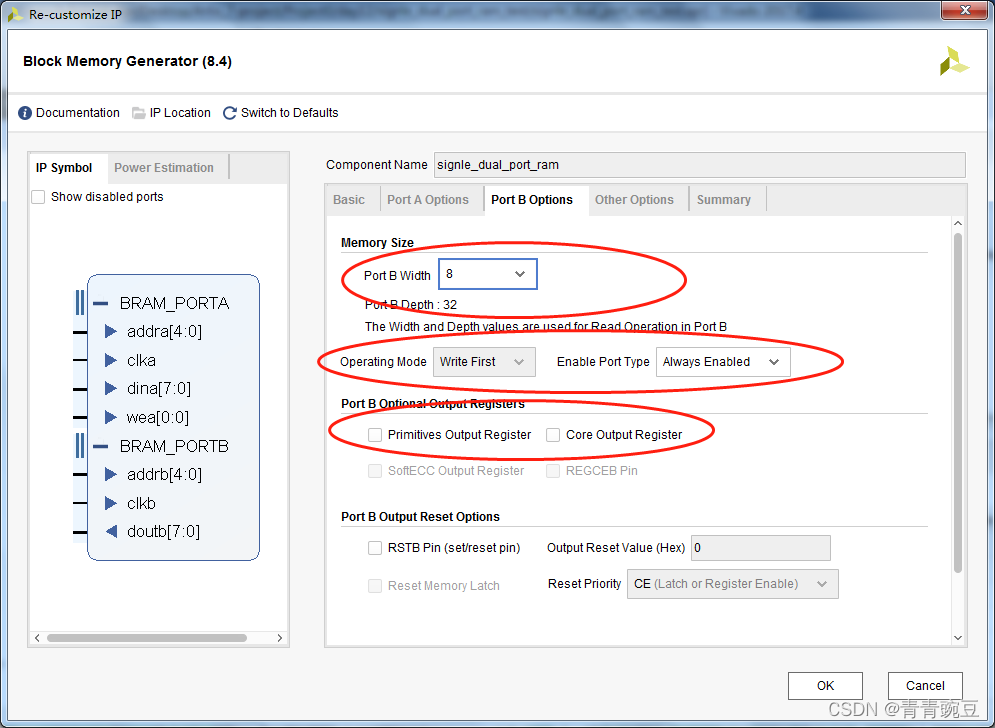

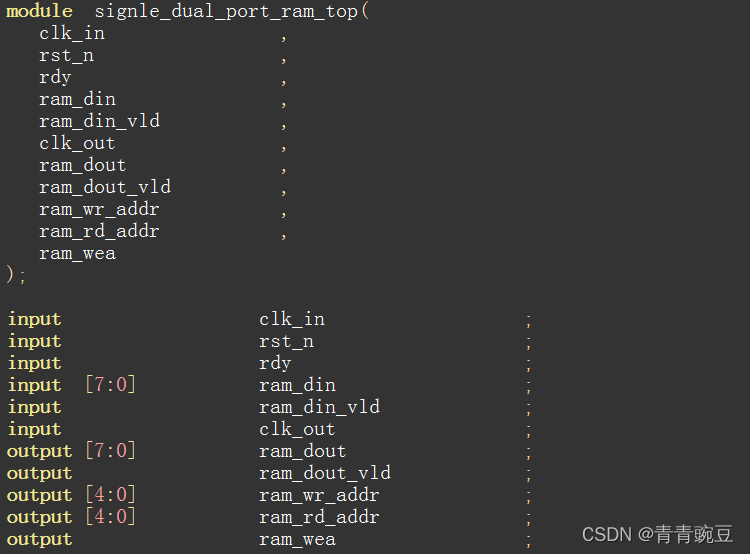

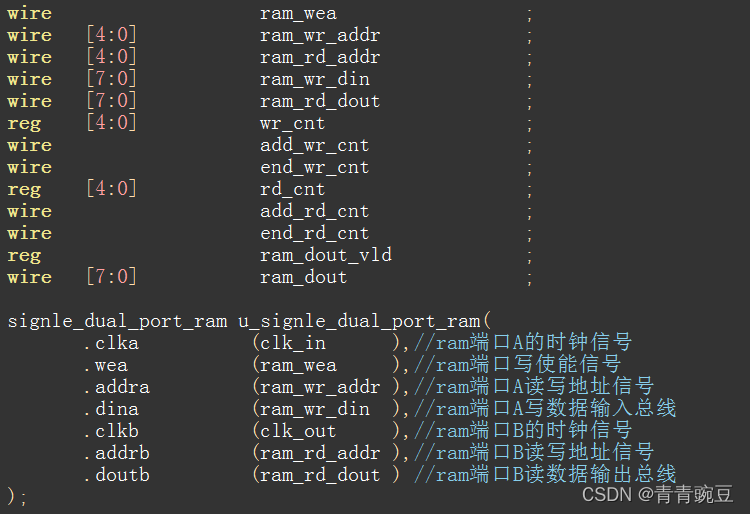

这里来设计一个经典的模块通过伪双口RAM来实现异步时钟FIFO功能,本模块包含读写位宽均为8位,读写深度是32的伪双口RAM,然后类似上一小节的FIFO练习,上游模块最多可以写入30个数据,每次输入写进本模块的数据信号ram_din和其指示信号ram_din同时到来,然后下游模块输入rdy信号时,本模块即向下游模块输出读出数据信号ram_ dout和其指示信号ram_dout_vld,同时为了方便观察,也把ram_wea写使能信号例化出来,如图2到4分别为伪双口RAM IP核的内存类型配置和端口AB的配置,本练习的信号列表如表1所示。

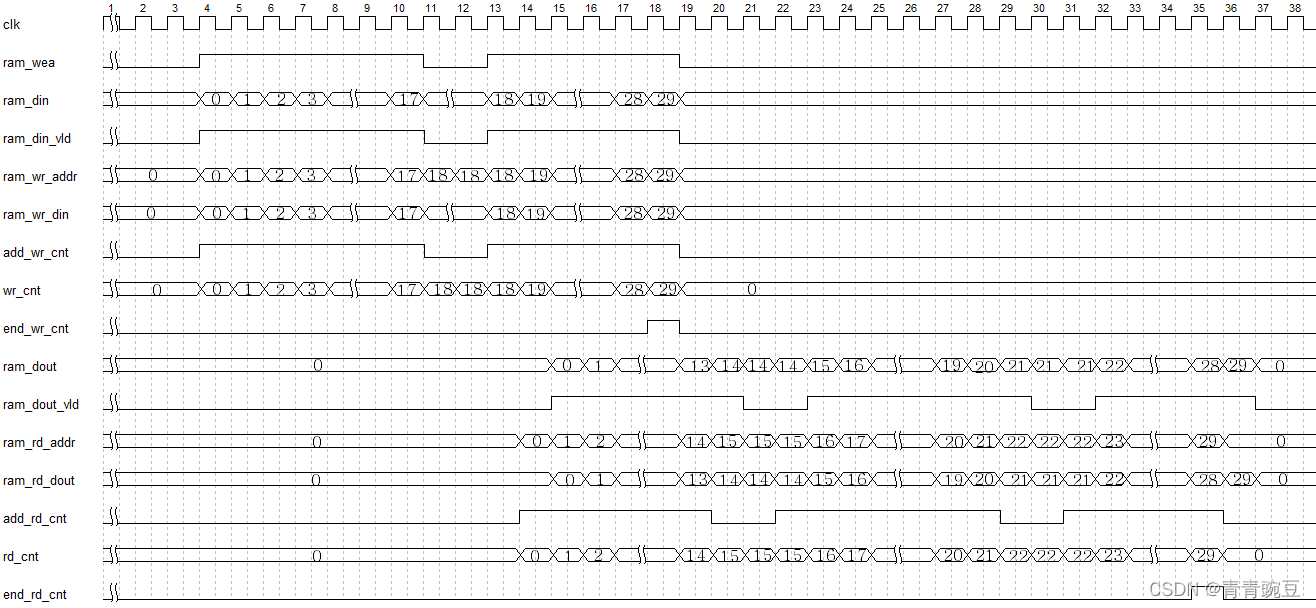

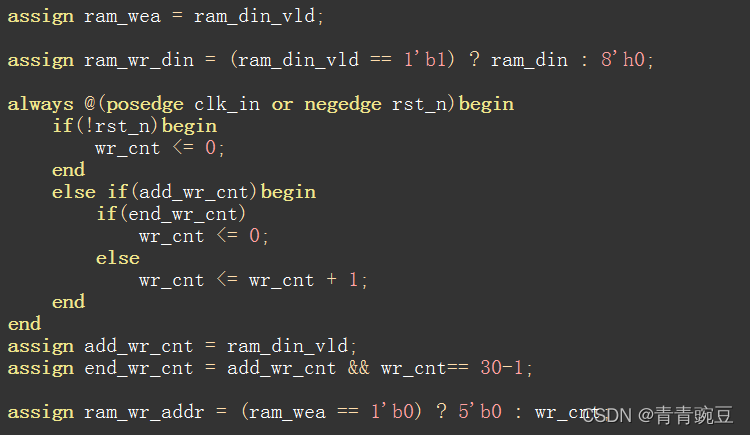

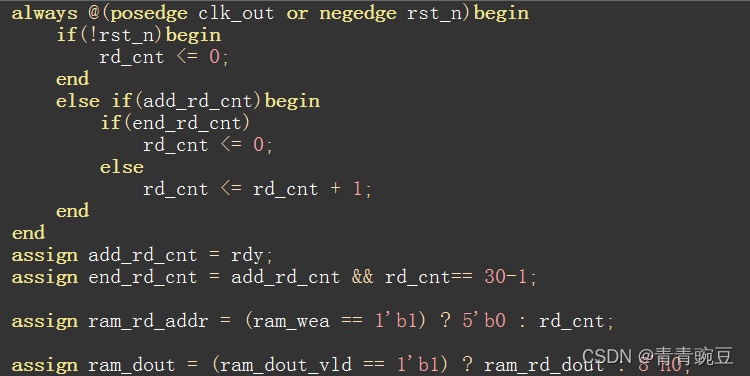

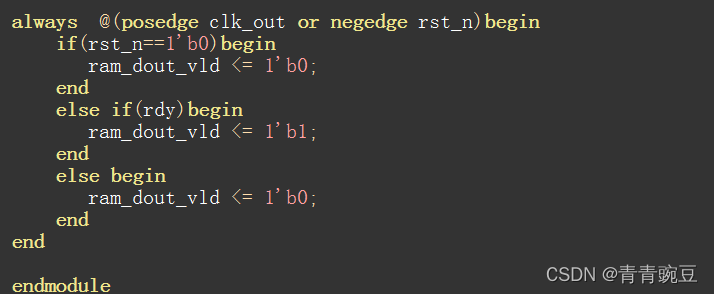

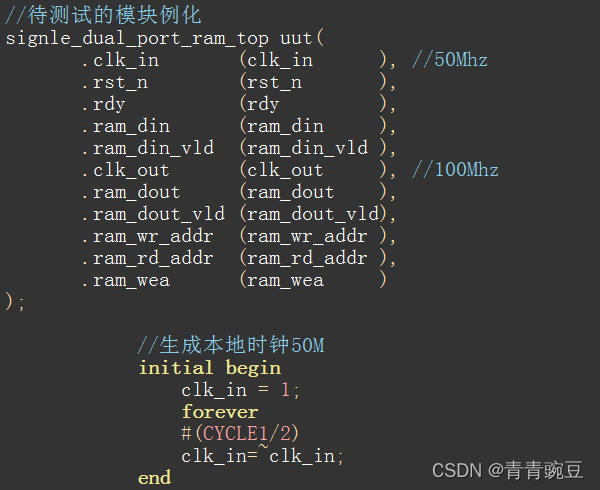

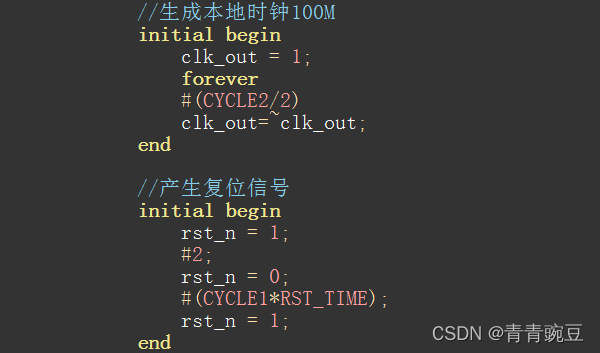

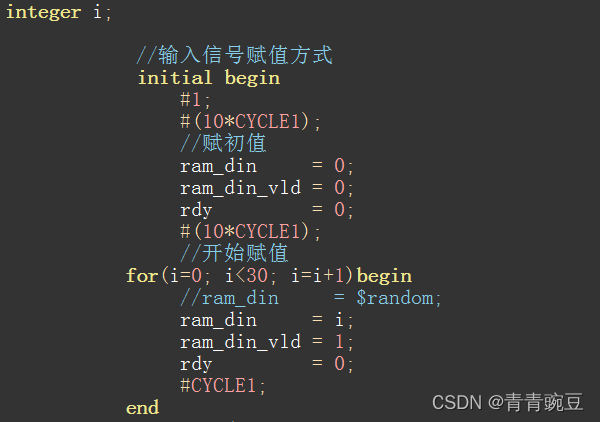

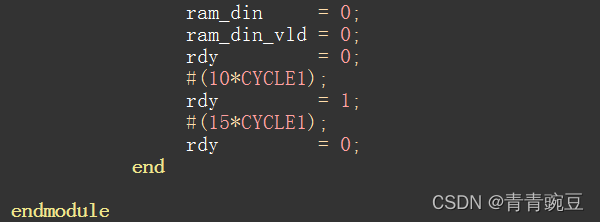

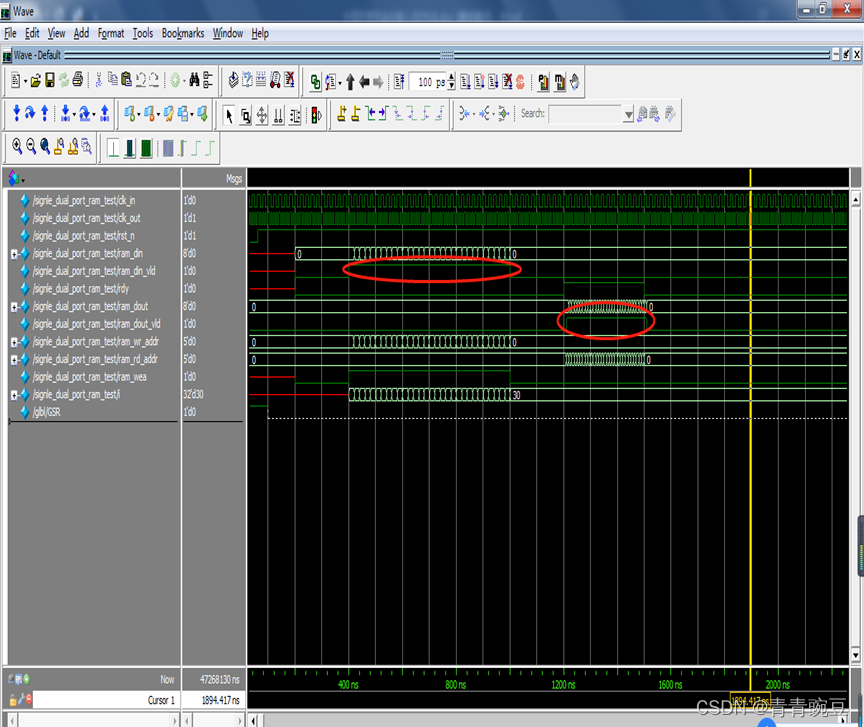

在这个练习中,我们wr_cnt和rd_cnt用以计数写入RAM数量和读出RAM数量,如图1伪双口RAM IP练习中各个信号的波形图,因为本模块相对设计比较复杂些,所以笔者在这里也用TimeGen把整个模块的各个信号量的波形图绘制出来,具体细节请大家参考图5伪双口RAM IP练习的代码设计,因为写入ram数据需要同一时钟下,在给出具体ram_wr_addr的同时ram_wea 为高且ram_wr_din被写入正确的数据,而读出ram数据,需要在给定ram_rd_addr后的一个时钟周期,ram_rd_dout才可以读出其正确的数据,在这里ram_dout_vld用了时序逻辑,来人为弥补ram_rd_dout较ram_rd_addr误差的一个时钟周期。如图6是本模块的输入信号激励设计,大家代入Modelsim后可以观察到如图7的仿真结果,可以观察到在ram_din_vld被拉高的周期内,上游模块输入了ram_din写入数据,而再下游模块输入rdy的信号时,本模块立刻拉高ram_dout_vld信号,并输出对应的ram_dout读出数据,仿真结果完全符合设计预期。

这篇博客也是最后一篇FPGA基础实践,后期FPGA博客更新将主要围绕上篇博客列举的20个经典实战例程展开。

| 信号列表 | ||

| 信号名 | I/O | 位宽 |

| clk_in | I | 1 |

| rst_n | I | 1 |

| rdy | I | 1 |

| ram_din | I | 8 |

| ram_din_vld | I | 1 |

| clk_out | I | 1 |

| ram_dout | O | 8 |

| ram_dout_vld | O | 1 |

| ram_wr_addr | O | 5 |

| ram_rd_addr | O | 5 |

| ram_wea | O | 1 |

表1 伪双口RAM IP练习设计中的信号列表

图1 伪双口RAM IP练习中各个信号的波形图

图2 伪双口RAM IP核的内存类型配置

图3 伪双口RAM IP核的端口A配置

图4 伪双口RAM IP核的端口B配置

图5 伪双口RAM IP练习的代码设计

图6 伪双口RAM IP核练习的输入信号激励设计

图7 伪双口RAM IP核练习的仿真结果

该博客介绍了如何利用伪双口RAMIP来设计一个具有异步时钟的FIFO模块,该模块具备读写位宽8位、深度32的特性。相较于真双口RAM和单口RAM,伪双口RAM在工程应用中提供了更好的读写平衡和设计稳定性。通过详细阐述信号交互和代码设计,展示了如何避免读写冲突并实现数据的重复读取和覆盖。此外,还提供了信号列表、波形图和仿真结果,以帮助读者理解和实现这一功能。

该博客介绍了如何利用伪双口RAMIP来设计一个具有异步时钟的FIFO模块,该模块具备读写位宽8位、深度32的特性。相较于真双口RAM和单口RAM,伪双口RAM在工程应用中提供了更好的读写平衡和设计稳定性。通过详细阐述信号交互和代码设计,展示了如何避免读写冲突并实现数据的重复读取和覆盖。此外,还提供了信号列表、波形图和仿真结果,以帮助读者理解和实现这一功能。

3819

3819

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?