一、半加器与全加器的前生今世

数字电路中加法器是经常用到的一种基本器件,主要用于两个数或者多个数的加和,加法器又分为半加器(half adder)和全加器(full adder)。半加器电路是指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。是实现两个一位二进制数的加法运算电路。而全加器是在半加器的基础上的升级版,除了加数和被加数加和外还要加上上一级传进来的进位信号。

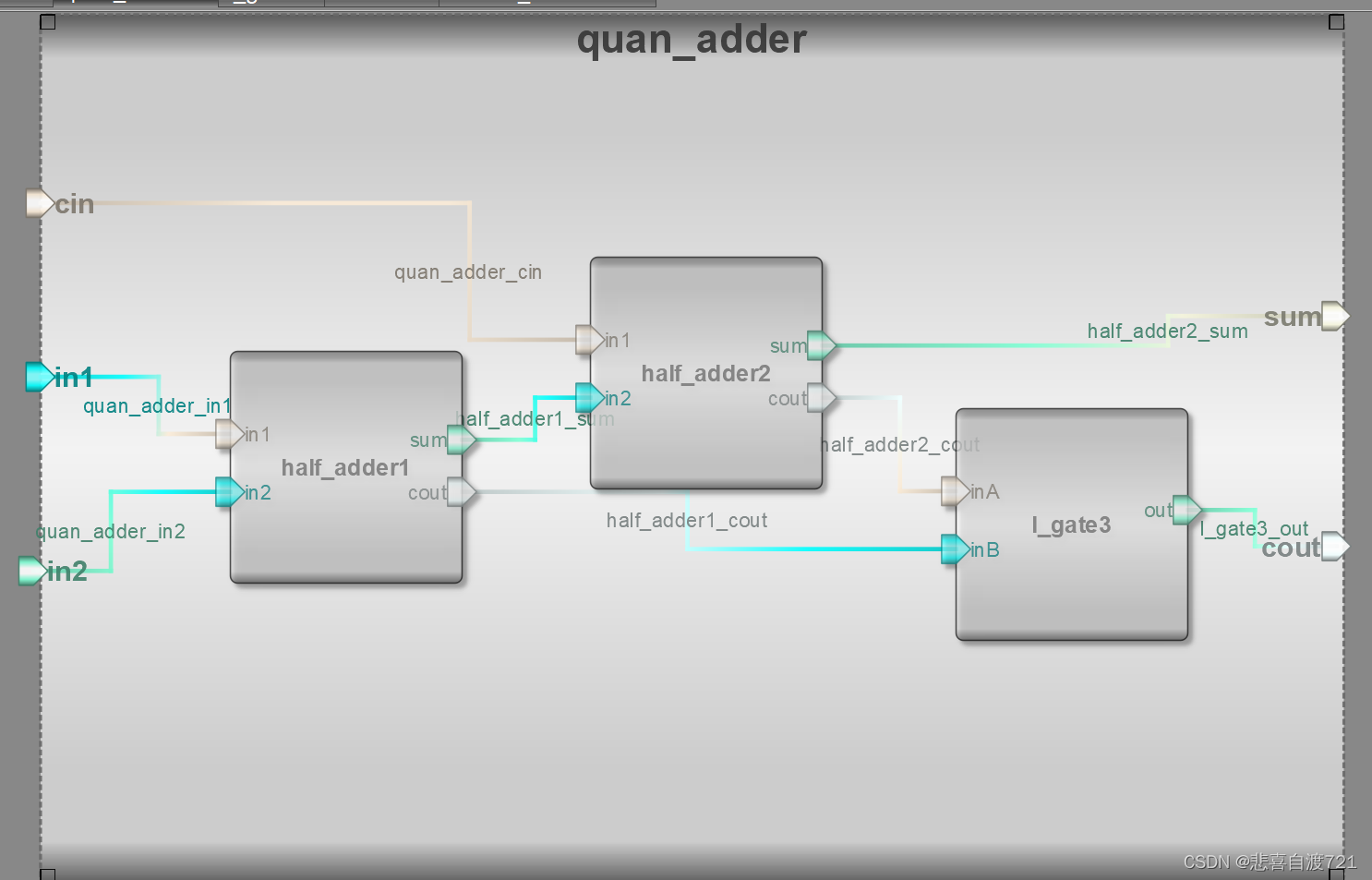

二、模块框图

half_adder的真值表(我们在数电中往往通过真值表把组合逻辑化简成由与非门构成的最简电路形式,然后再根据表达式用Verilog语言实现。)

| input(in1) | inpur(in2) | output(sum) | output(cout) |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

在这个真值表里我们发现sum的结果是经过一个异或门,cout的结果是经过一个与门

三、功能实现

half_adder.v

第一种实现方法简单组合逻辑

assign {cout,sum}=in1+in2;

第二种方法时序逻辑

always @(posedge clk or negedge reset)

if(reset == 0) begin

sum <= 0;

cout <= 0;

end

else if(in1 == 0 && in2== 1)begin

sum <= 1;

cout <= 0;

end

else if(in1 == 1 && in2 == 0)begin

sum <= 1;

cout <= 0;

end

else if(in1 == 1 && in2 == 1)begin

sum <= 0;

cout <= 1;

end

else begin

sum <= 0;

cout <= 0;

end

管脚约束

上板现象

1+1={1,0}

1+0={0,1}

1+0={0,1}

0+1={0,1} 0+0={0,0}

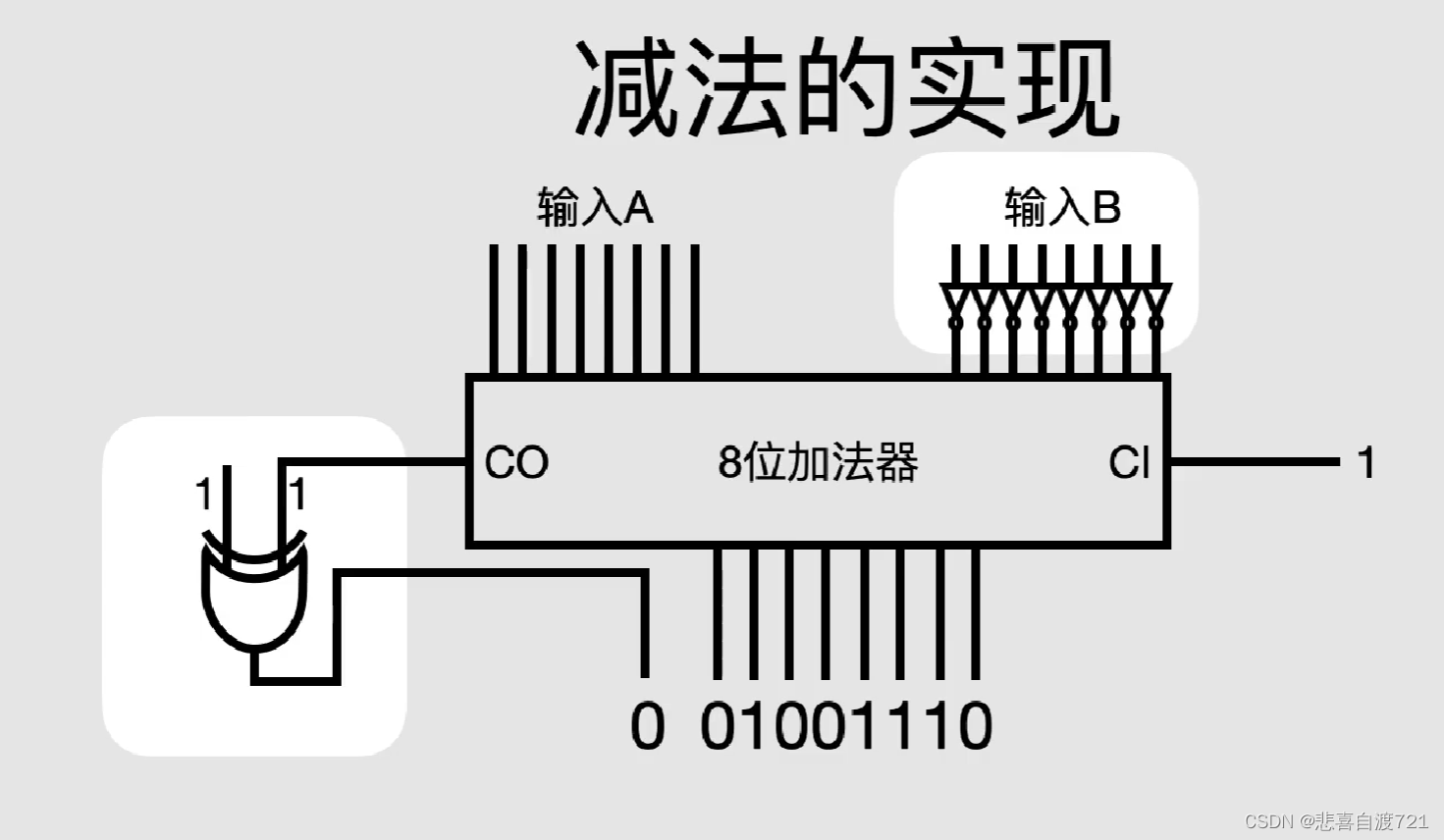

四、全加器的实现

| in1 | in2 | cin | sum | cout |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

两个半加器再加一个或门构成全加器

下面我们直接尝试3位全加器的串联

首先设计全加器

三级全加器串联→3bit全加器

管脚约束.xdc

上板现象

1024

1024

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?