1.【实验要求】:

- 利用“与门”、“或门”、“非门”设计并实现1位半加器电路。

2.【实验目的】

- 掌握组合逻辑电路的设计方法;

- 熟悉Vivado2014集成开发环境和Verilog编程语言,掌握1位半加器电路的设计与实现。

3.

真值表:

| 输入 | 输出 | |||

| X | Y | Z | C | S |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 输入 | 输出 | |||

| X | Y | Z | C | S |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

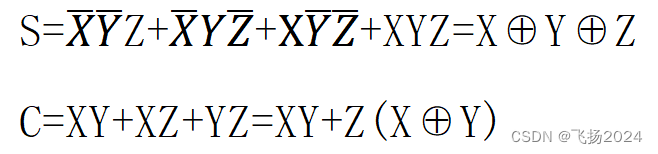

4.逻辑方程:

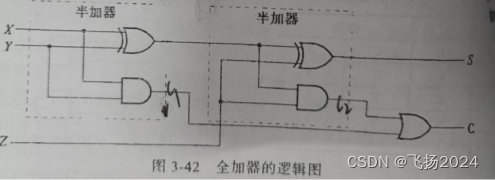

5.电路图

6.

代码实现:

module half_addition(

input x,

input y,

input z;

output c,

output s

);

wire s1,c1,c2;

xor xor1(s1,x,y);

xor xor2(s,s1,z);

and and1(c1,x,y);

and and2(c2,s1,z);

or or1(c,c1,c2);

endmodule

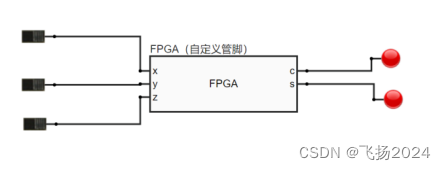

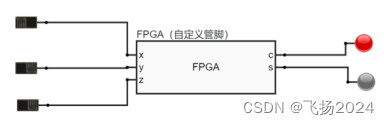

7.实验结果

武汉理工大学计算机专业

5820

5820

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?