1.1 uart 模块验证流程

1、理解dut

2、制定验证策略方法

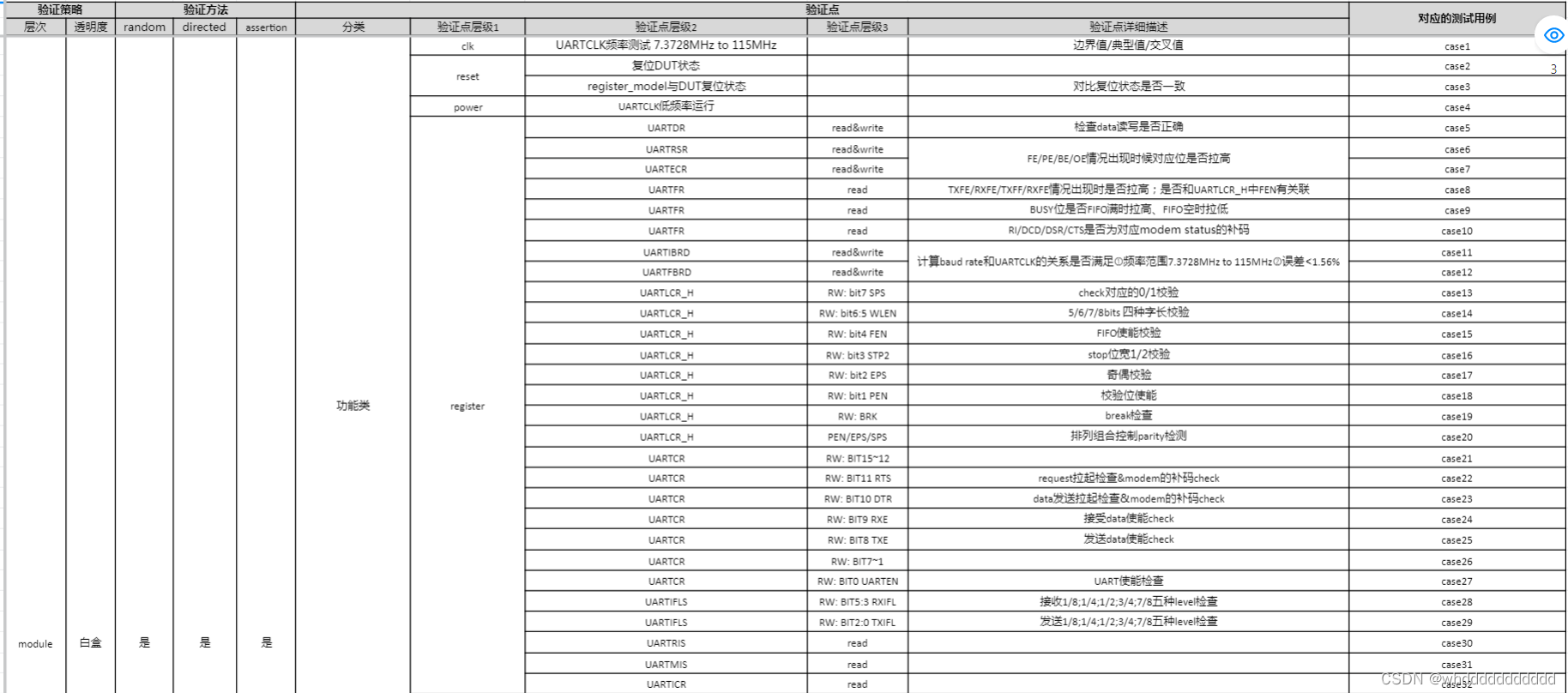

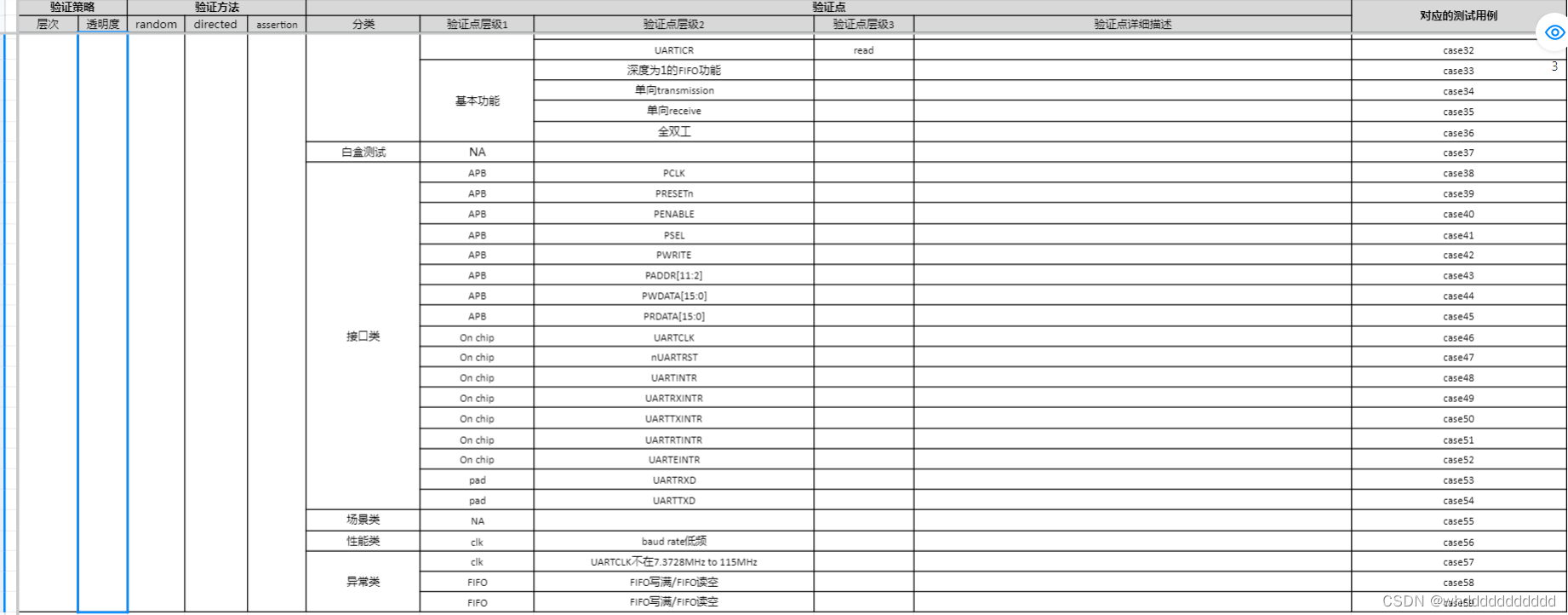

3、提取验证点(feature list)-》testcase list

4、搭建验证平台(1、验证框架图2、验证环境代码);sanity case

5、执行验证

写testcase跑仿真+regression(1、大批量仿真(rtl_freeze前)收集覆盖率(前提是仿真pass)、分析覆盖率+补充case 2、后仿netlist(rtl_freeze后))

1.2 uart 模块及验证策略和验证方法

验证策略:白盒测试(已知内部代码和结构)

验证方法:随机测试(分析覆盖率)+定向测试

code coverage:line/condition/fsm/assertion/toggle

function converage:covergroup/coverpoint/bins/cross/sample

1.3 提取验证功能点

小知识点:interrupt 三组寄存器:status mask clear

698

698

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?