IP核及综合系统设计

一、实验目的

1. 了解IP模块的定义,分类及其应用,掌握模块化设计方法。

2. 掌握电路性能分析的实际操作方法和实际硬件芯片的内部资源情况。

二、实验设备

1、 计算机

2、 实验板

三、实验要求:

1、在PC机上完成仿真,对结果进行分析;

2、完成下载,在实验板上进行验证。

四、实验内容

1、设计原理

通过该次实验之前所设计的三选一数据选择器与多用分频器,将该两个实验封装成两个IP核,因为想要实现多用途使用,应而借用parameter来创建超参数。封装核后,当有工程需要该功能时,直接调用该IP核来简化代码,或者借用他人的设计来辅助完成自己的任务。

2、给出设计源文件

module main(

input clk,

input clr,

input [1:0]x,

output clkout,

output [2:0]LED);

wire clk20hz,clk10hz,clk5hz;

IP_clk_div_0 u1(clk,clk20hz);

IP_clk_div_1 u2(clk,clk10hz);

IP_clk_div_2 u3(clk,clk5hz);

assign LED = {clk20hz,clk10hz,clk5hz};

wire PWM1,PWM2,PWM3;

IP_PWM_0 u4(clk20hz,clr,PWM1);

IP_PWM_1 u5(clk10hz,clr,PWM2);

IP_PWM_2 u6(clk5hz,clr,PWM3);

IP_selector_0 u7(x,PWM1,PWM2,PWM3,clkout);

Endmodule

module IP_selector( x,clk_20hz,clk_10hz,clk_5hz,y);

input[1:0] x;

input clk_20hz;

input clk_10hz;

input clk_5hz;

output reg y;

always@(*)

case(x)

2'b00:y<=clk_20hz;

2'b01:y<=clk_10hz;

2'b10:y<=clk_5hz;

endcase

Endmodule

`timescale 1ns / 1ps

module IPI_PWM(

input wire clk,

input wire clr,

output reg pwm

);

reg[4:0] count;

parameter count1 =19;

parameter count2 =10;

always @(posedge clk or posedge clr)

if(clr == 1)

count <= 0;

else if(count == count1)

count <= 0;

else

count <= count + 1;

always @(*)

if(count < count2)

pwm <= 1;

else

pwm <= 0;

Endmodule

`timescale 1ns / 1ps

module IPI_clk_div(

input clk,

output reg clk_Hz

);

integer clk_cnt;

parameter[31:0] div=32'd10000000;

always @(posedge clk)

begin

if(clk_cnt>=div)/

begin

clk_cnt <= 1'b0;

clk_Hz <= ~clk_Hz;end

else

clk_cnt <= clk_cnt + 1'b1;

end

endmodule

3、仿真测试文件

分频器仿真

`timescale 1ns / 1ps

module test();

reg clk100M;

reg rst;

wire clkout;

clk_div u0(clk100M,rst,clkout);

initial

begin

clk100M=0;rst=1'b0; #100; rst=1'b1;end

always #10 clk100M=~clk100M;

endmodule

module test();

reg clk100M;

reg rst;

wire clkout;

reg [1:0] x;

reg clk20hz;

reg clk10hz;

reg clk5hz;

initial

begin

clk100M=0;rst=1'b0;x = 0;clk20hz=0;clk10hz=0;clk5hz = 0;

#100; rst=1'b1;end

IPI_data_selecter t1( x,clk20hz,clk10hz,clk5hz,clkout);

always

#10 clk100M=~clk100M; always

#20 clk20hz = ~clk20hz;

always

#40 clk10hz = ~clk10hz;

always

#80 clk5hz = ~clk5hz;

always #100 x = x+1;

endmodule

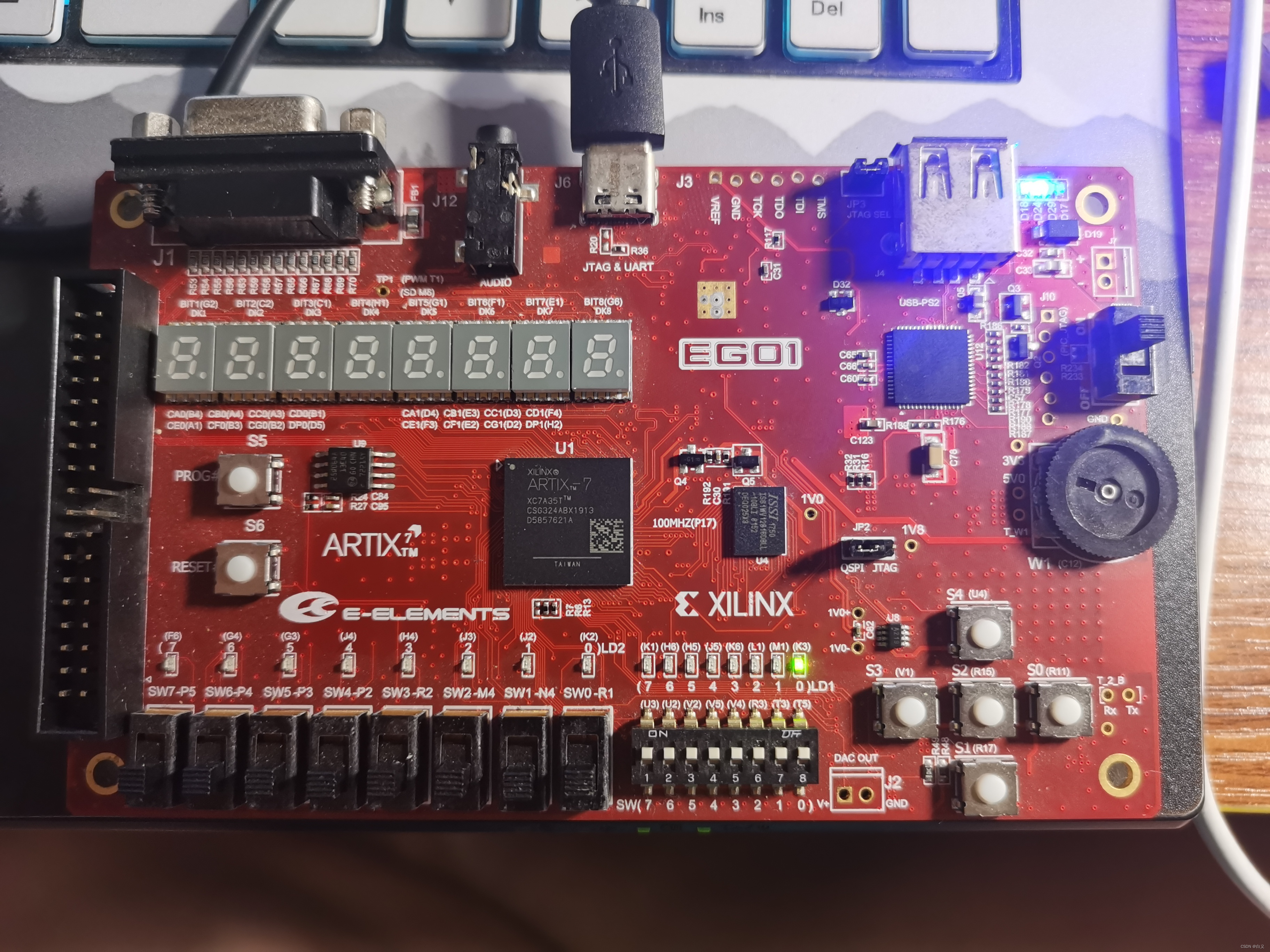

实验板为

1392

1392

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?