一. 在线Verilog编程网站学习:

从门电路、组合电路、时序电路中各选3个以上的例题进行实践练习,并记录结果。

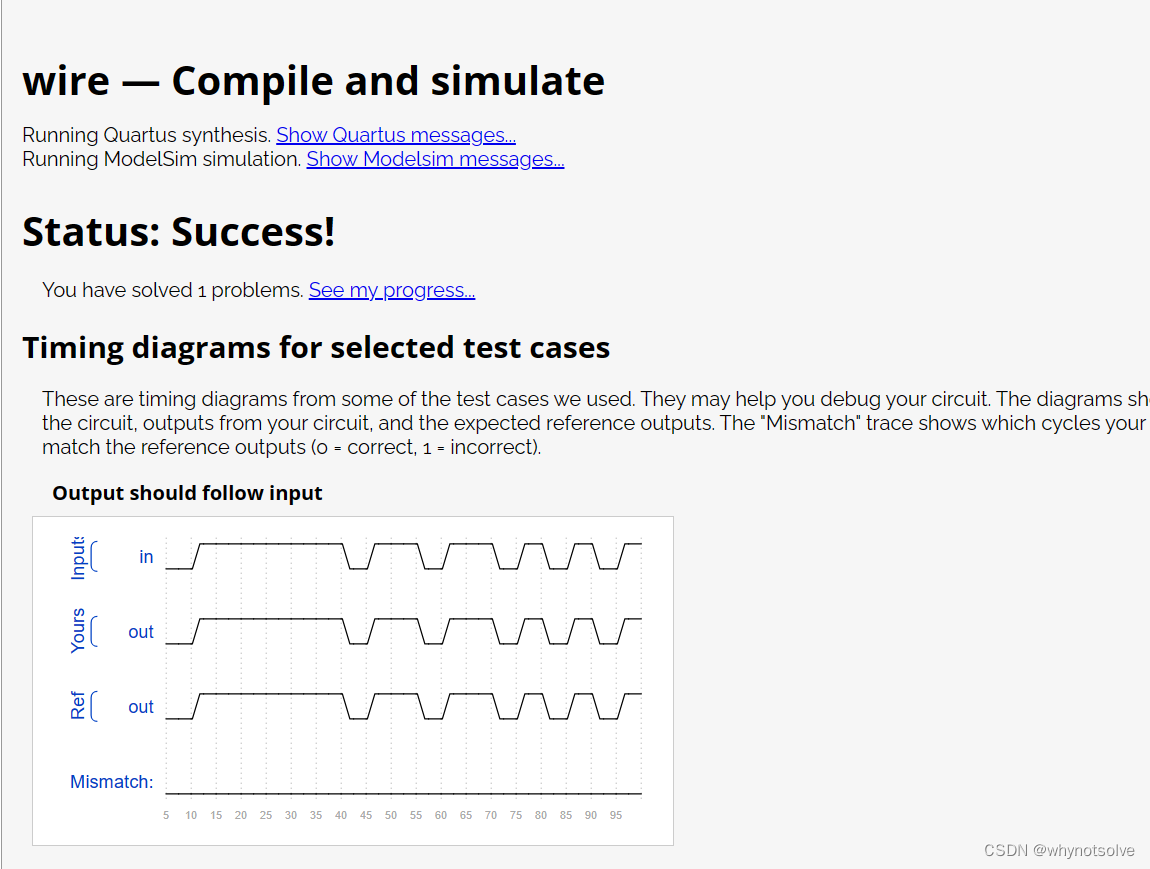

认识Wire:

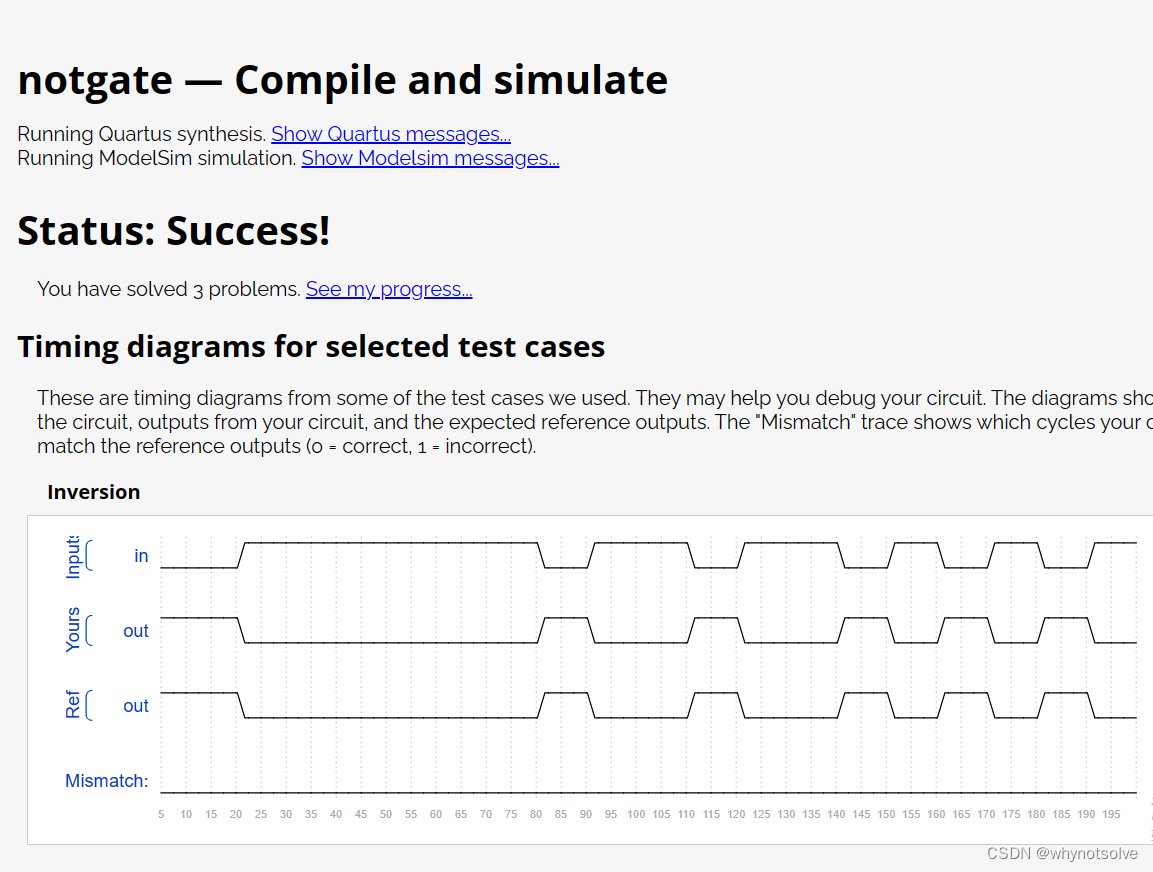

非门:

module top_module( input in, output out );

assign out=~in;

endmodule

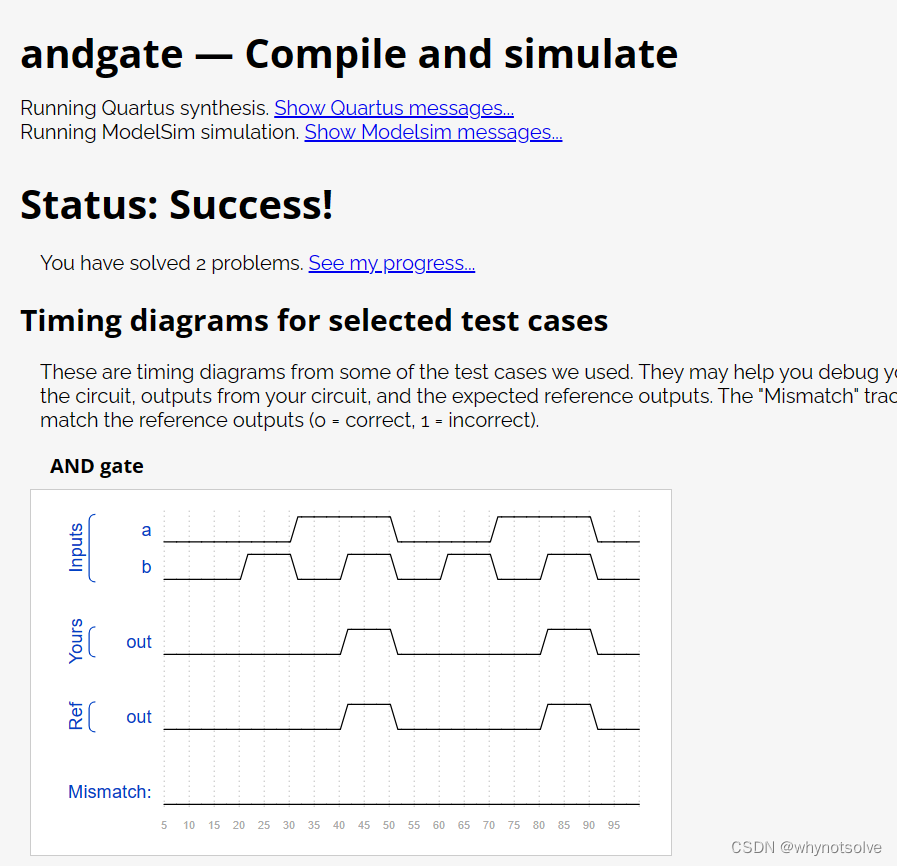

与门:

module top_module(

input a,

input b,

output out );

assign out=a&b;

endmodule

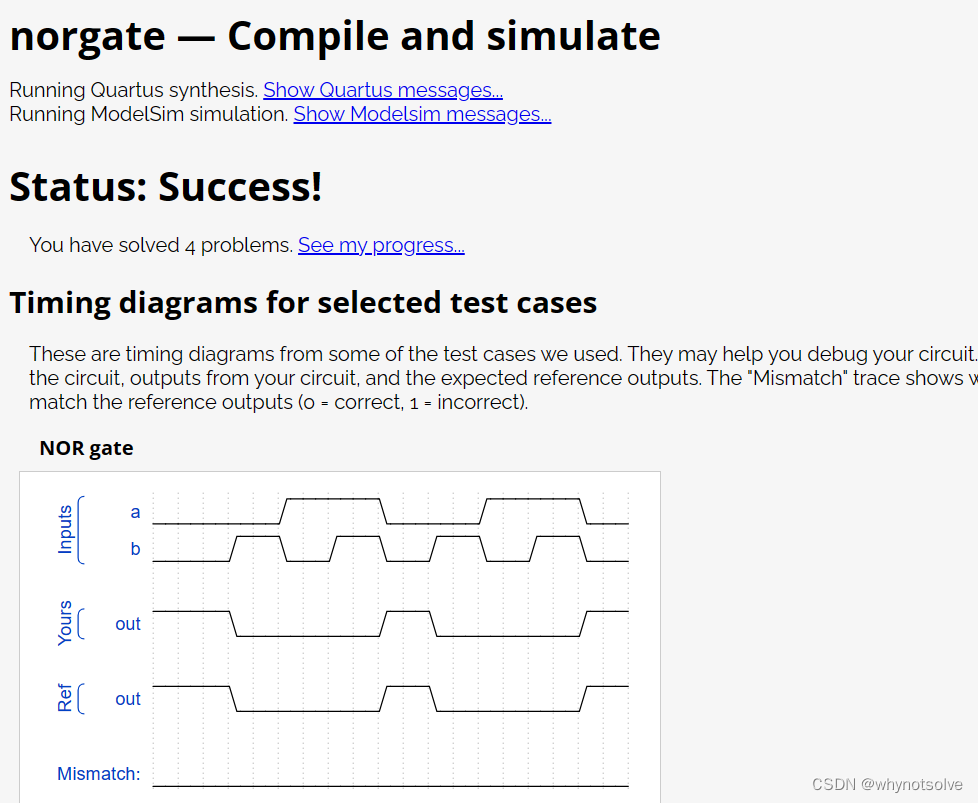

或非门:

module top_module(

input a,

input b,

output out );

assign out=~(a|b);

endmodule

二、

1)首先安装Logisim软件,新建一个项目,采用门电路组合电路方式完成一个1位全加器的设计,并在Logisim中进行测试。然后封装这个1位全加器为自定义的一个子电路模块(比如名称为OneAdder),然后新建一个项目,用1位全加器串行级联方式完成一个4位全加器的设计,并进行功能测试。

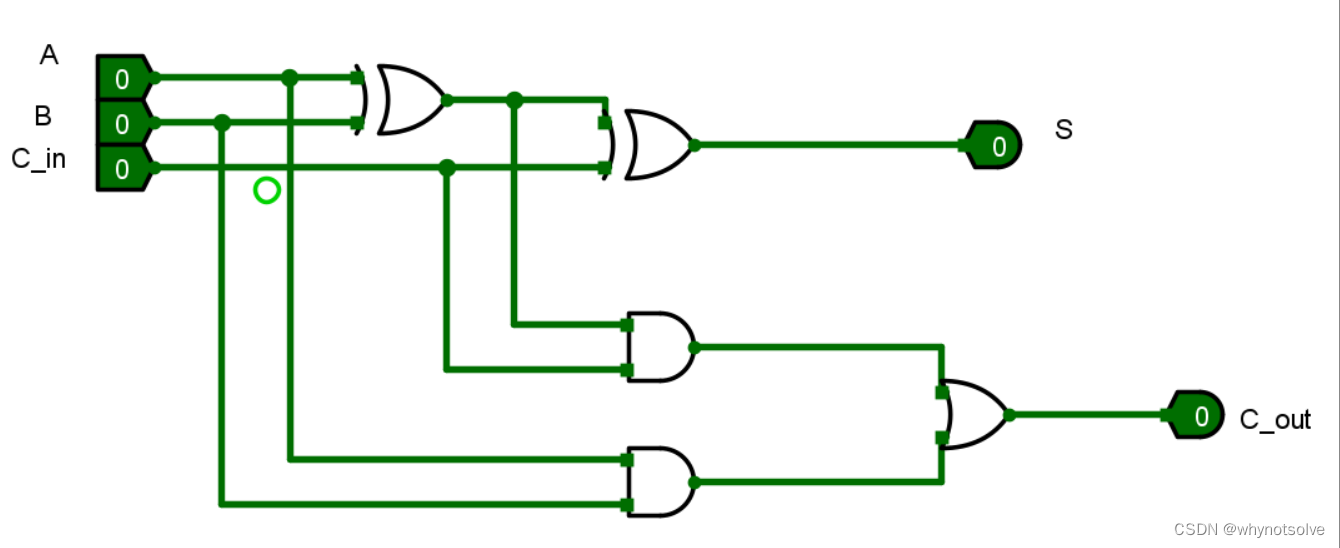

1位全加器logisim电路

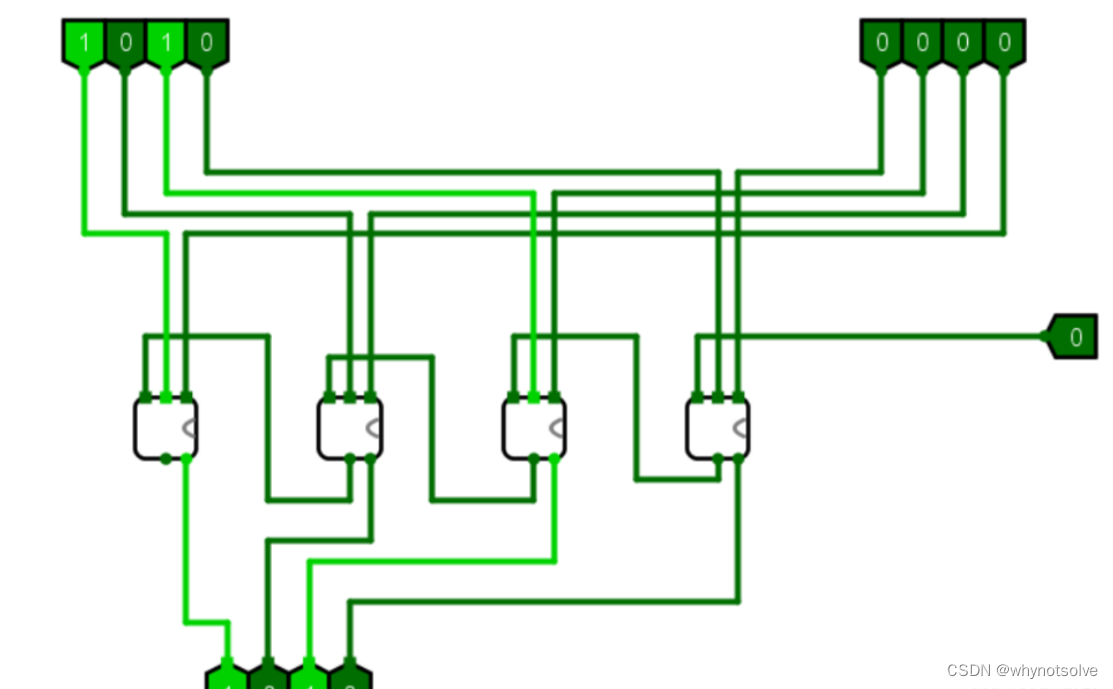

4位全加器设计

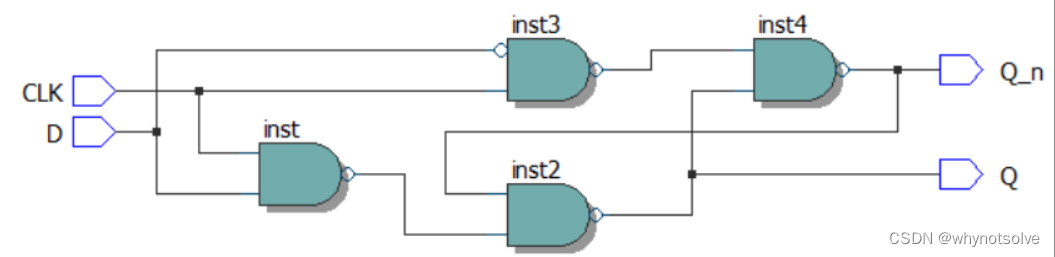

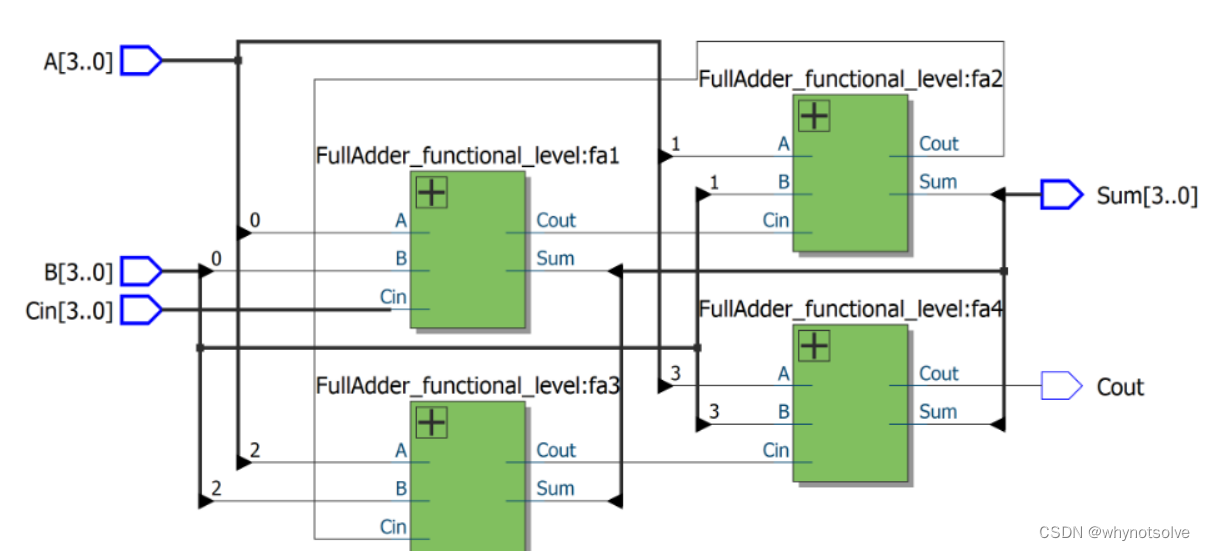

2)首先基于Quartus 软件完成一个1位全加器的设计。分别采用原理图输入以及 Verilog编程 这两种设计方法。然后通过4个1位全加器的串行级联,完成一个4位全加器的 原理图设计;再改用 Verilog编程(3种模式:门电路、数据流和行为级描述),完成这个4位全加器设计,并观察Verilog代码编译综合后生成的 RTL电路,与之前电路图设计的4位全加器电路进行对比 。

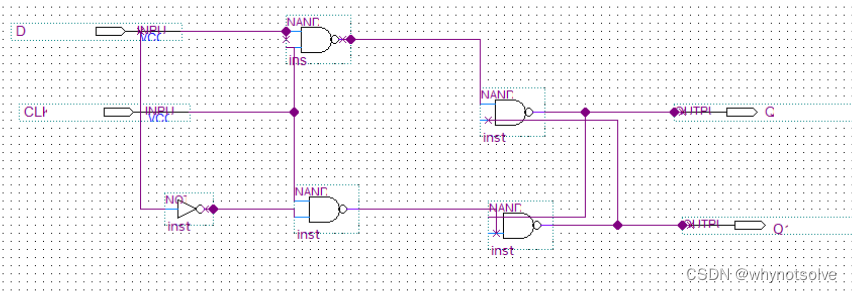

1位全加器原理图输入

首先创建方框文件:

硬件电路图:

代码:

module FullAdder_functional_level (

input A, B, Cin,

output Sum, Cout

);

// Full Adder logic

assign {Cout, Sum} = A + B + Cin;

endmodule

一个4位全加器Verilog编程

module FullAdder_functional_level (

input A, B, Cin,

output Sum, Cout

);

// Full Adder logic

assign {Cout, Sum} = A + B + Cin;

endmodule

module FourBitAdder_functional_level (

input [3:0] A, B, Cin,

output [3:0] Sum,

output Cout

);

wire c1, c2, c3;

FullAdder_functional_level fa1(A[0], B[0], Cin, Sum[0], c1);

FullAdder_functional_level fa2(A[1], B[1], c1, Sum[1], c2);

FullAdder_functional_level fa3(A[2], B[2], c2, Sum[2], c3);

FullAdder_functional_level fa4(A[3], B[3], c3, Sum[3], Cout);

endmodule

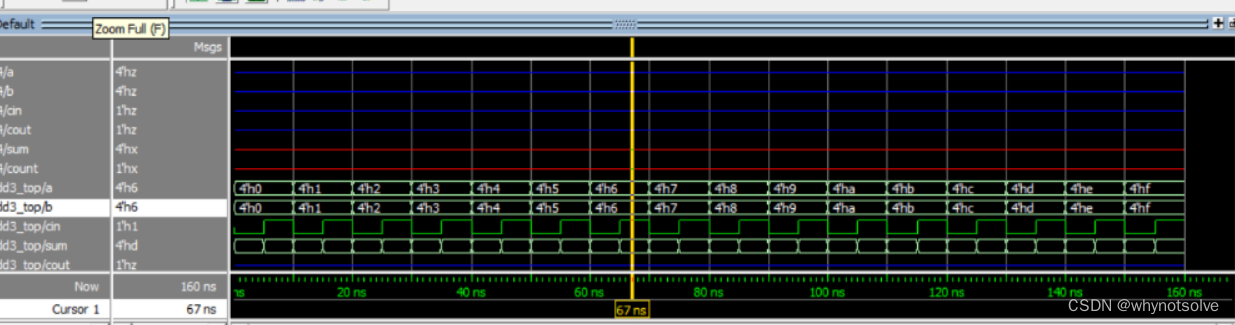

3)编写 测试激励Verilog模块,用Modelsim 对4位全加器 Verilog模块进行仿真测试,观察仿真波形图。如果仿真波形的逻辑功能正确,就连接的实验室 DE2-115开发板硬件上,完成引脚绑定,烧录,再拨动按钮开关,进行加法器 正确性的验证。

4位全加器

module a4(sum,cout,a,b,cin);

input [3:0] a,b;

input cin;

output cout;

output [3:0] sum;

assign {count,sum} = a+b+cin;

endmodule

`timescale 1ns/1ns

`include "MyFirstVerilog.v"

module add3_top; 测试模块的名字

reg[3:0] a,b;//测试输入信号定义为 reg 型

reg cin;

wire[3:0] sum;//测试输出信号定义为 wire 型

wire cout; integer i,j;

a4 adder(sum,cout,a,b,cin); //调用测试对象

always #5 cin=~cin;//设定 cin 的取值

initial

begin a=0;b=0;cin=0;

for(i=1;i<16;i=i+1)

#10 a=i; //设定 a 的取值

end

initial

begin

for(j=1;j<16;j=j+1)

#10 b=j;//设定 b 的取值

end

initial

//定义结果显示格式

begin

$monitor($time,,,"%d + %d + %b={%b,%d}",a,b,cin,cout,sum);

#160

$finish;

end

endmodule

//设定 b 的取值

end

initial

//定义结果显示格式

begin

$monitor($time,,,"%d + %d + %b={%b,%d}",a,b,cin,cout,sum);

#160

$finish;

end

endmodule

545

545

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?