转自:【基础】RS触发器_两个或非门构成rs触发器-CSDN博客

RS触发器为什么能 “保持上一状态”

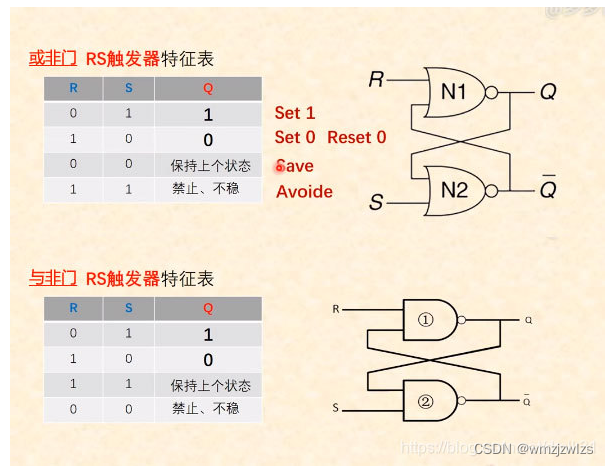

触发器就是在常规的门电路的基础上加入了反馈,这样触发器就实现了存储数据的功能。这也是上面章节 “RS触发器实验” 的 RS触发器特征表 中第3条 “保持上一个状态” 的原因。

这点非常非常重要,同时也比较难理解;所谓存储数据,并不是像大家所想的直接把数据位刻在哪里,而是利用反馈的数据,这样 R端 或 S端 某个脚脱离高电平后然后再接入低电平时,输出的Q和`Q结果不会变化。

比如 R=0,S=1 时,Q输出为1;此时我们把 S 端 的脚和高电平断开(此时悬空了),由于 Q 反馈到N2(Q=1),所以 S 端断开后 N2 仍就输出 0,整个RS触发器输出保持不变。

▪ RS触发器为什么有 “禁止、不稳的状态”

在上面章节 “RS触发器实验” 的 RS触发器特征表 中第4条中我们有一个状态:“禁止、不稳的状态” 。这个状态是由当 R=1,S=1 时触发的。

虽然当 R=1,S=1 时 RS触发器 的电路也能达到一个稳定状态,但是在设计 RS触发器 的时候,就已经规定了 Q和`Q 必须是反相的,基于 RS触发器 的其他应用也默认 Q和`Q 是反相进行设计。

所以当 R=1,S=1 就是非法的。我们在编写或设计电路的时候就要规避这个情况。

还有一种情况就是当 R=1、S=1 近乎同时跳变到 R=0、S=0 时。虽然近乎同时,但实际:

有可能 R 先变为 0(那么此时 Q 就输出1,那么N2因为Q反馈的原因,`Q=0)

也有可能 S 先变为 0(那么此时 `Q 就输出1,那么 N1 因为 `Q反馈的原因,Q=1)

由于无法确定R或S哪个先变为0,那么就会出现不稳定因素,这也是 R=1,S=1 非法的原因之一。

▪ RS触发器总结

无论是或非门还是与非门:

当 R=1,S=0 时,表示 Reset 激活了,那么 Q = Reset = 0

当 R=0,S=1 时,表示 Set 激活了,那么 Q = Set = 1

禁止,不稳定的状态:

或非门时 R = S = 1 时禁止,因为Q和`Q输出都是0;为了方便记忆,可以认为非门时,1 强于 0,所有反馈无法改变和 1 的非值,RS触发器也就无法自我调节

与非门时 R = S = 0 时禁止,因为Q和`Q输出都是1;为了方便记忆,可以认为与门时,0 强于 1,所有反馈无法改变和 0 的与值,RS触发器也就无法自我调节

本文详细解释了RS触发器如何通过反馈保持上一状态,以及R=1,S=1导致的禁止和不稳定状态。它还讨论了与非门和或非门在RS触发器中的作用和禁用条件。

本文详细解释了RS触发器如何通过反馈保持上一状态,以及R=1,S=1导致的禁止和不稳定状态。它还讨论了与非门和或非门在RS触发器中的作用和禁用条件。

8万+

8万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?