-3dB到底是什么?集成运放-3dB带宽又是什么?

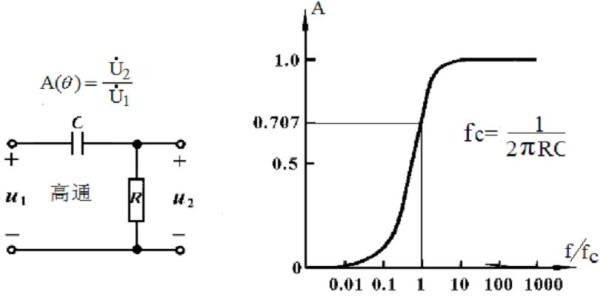

以无源高通电路为例,介绍-3dB的意义。

输出与输入只比:

Au=Uo/Ui=R/(R+1/j*2*PI*f*C)=1/(1+1/j*2*PI*f*R*C)。式中j*j=-1。

令fL=1/2*PI*R*C

Au=1/(1+fL/jf)=jf/(jf+fL)=(jf/fL)/(1+jf/fL)=(1-jf/fL)*(jf/fL)/(1-jf*jf/fL*fL)

Au=(jf/fL)/(1+f*f/fL*fL)+(f*f/fL*fL)/(1+f*f/fL*fL)

幅值:

|Au|=(f/fL)/根号((1+f*f/fL*fL))。

幅频特性采用20lg|Au|表示,单位是分贝(dB)。

当f=fL时,20lg|Au|=-20lg(根号2)=-3dB。(20lg|Au|=20lg(根号2)/2)

f为输入信号的频率,fL称为电路截止频率。

即当f=fL时,|Au|=根号2/2。

在集成运放参数中,有一项为开环带宽和单位增益带宽BWG。

又称-3dB带宽,指在正弦小信号激励下,运放开环电压增益随频率升高,增益下降3dB(输出是输入的根号2/2倍)所对应的信号频率;而增益下降至1,即0dB时的频率定义为单位增益带宽。

单位增益带宽是一个很重要的指标,对于正弦小信号放大时,单位增益带宽等于输入信号频率与该频率下的最大增益的乘积,换句话说,就是当知道要处理的信号频率和信号需要的增益后,可以计算出单位增益带宽,用以选择合适的运放。这用于小信号处理中运放选型。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间

299

299

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?