硬件准备

- CompactRIO9040

- NI9871

- 直流电源(可调)

- 网线

- RJ50转DB9线

- 鸣志STF03-R驱动器和步进电机

软件安装

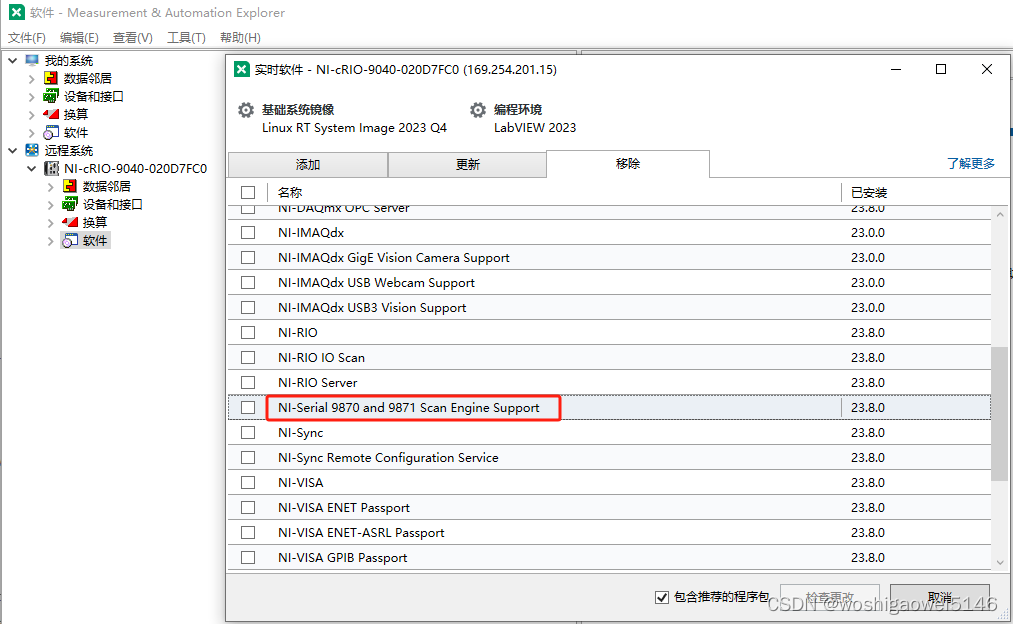

此外,需安装NI-Serial 9870和9871扫描引擎支持

打开NI Measurement&Automation Explorer(MAX)- 远程系统 - cRIO9040 - 添加/删除软件 - 选择NI-Serial 9870和9871扫描引擎支持。

硬件准备

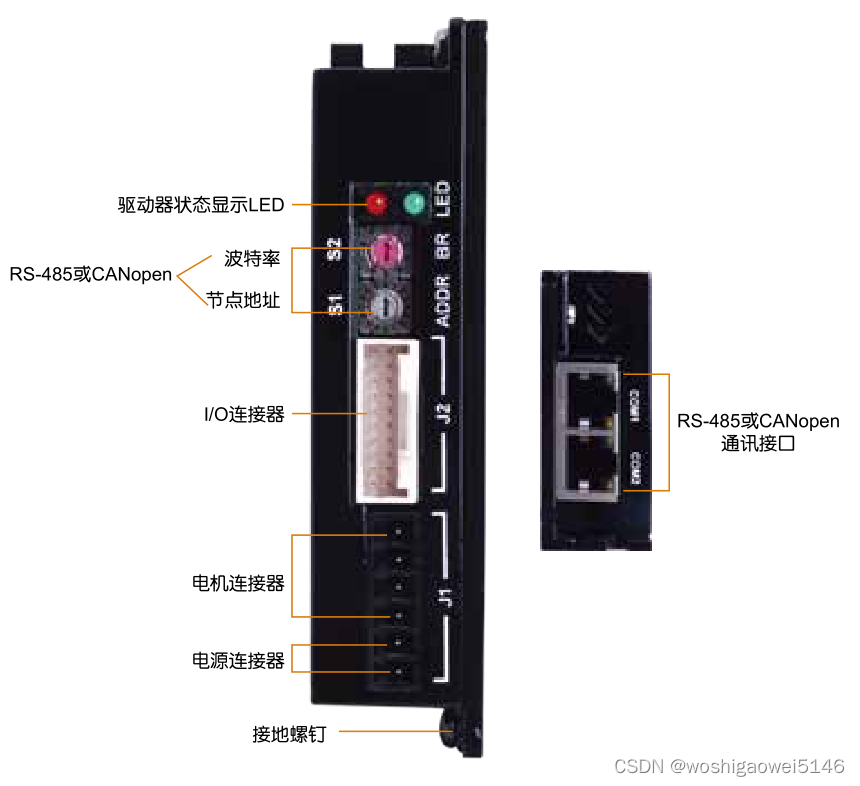

NI-9871介绍

NI‑9871为CompactRIO系统增加了RS485/RS422串行端口。 串行端口可直接通过FPGA访问,从而灵活地与串行设备通进行信。 模块的各个端口上均配有独立缓冲器,可节省FPGA空间,并简化编程。 NI‑9871支持标准启动位、停止位和握手设置。 该接口使用外接电源,在各种串行端口条件下均能提供最高兼容性和可靠性。

将NI9871插入卡槽内,需外接+8 V ~ +28 V的DC电源,将可调直流电源接到NI9871下部电源并调整到+10V。

将RJ50转DB9线接入PORT1-PORT4任意端口(这里注意要用RJ50的网口,和常规的RJ45不一样)

将DB9端口接入一个转换接口接到鸣志STF03-R驱动器的COM1.

采用四线制接线方式,将鸣志STF03-R驱动器的RX+连接至主控制器的TX+,驱动器的RX-连接至主控制器的TX-;驱动器的TX+连接至主控制器的RX+,驱动器的TX-连接至主控制器的RX-;驱动器的GND连接至主控制器的GND。STF03-R

注意:驱动器RS-485通讯口内部已作隔离,从机驱动器通讯口GND必须与主机上位控制器GND共地,与其他从机驱动器通讯口GND共地;

鸣志STF03-R驱动器接线:

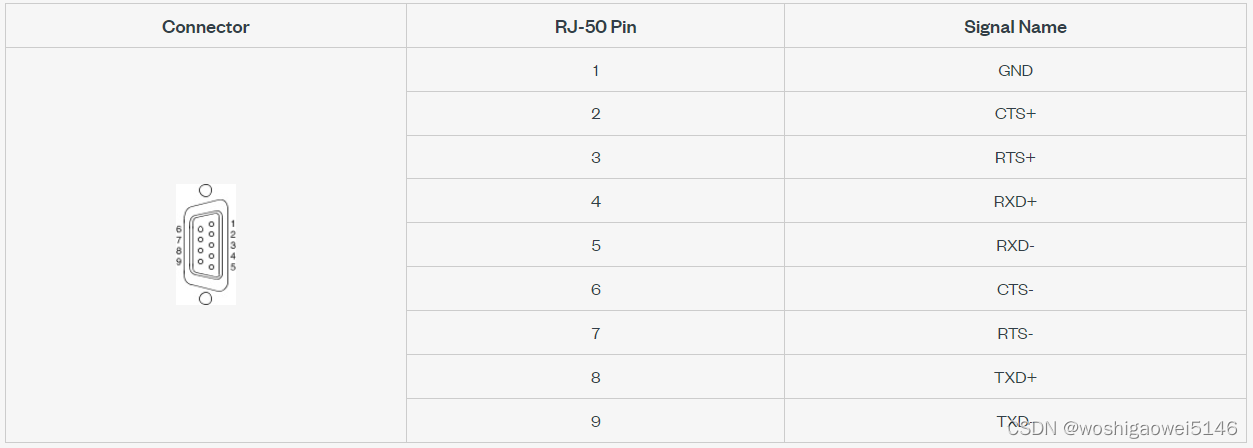

NI-9871 RS485/RS422 DB-9接线:NI-9871 Getting Started

软件测试

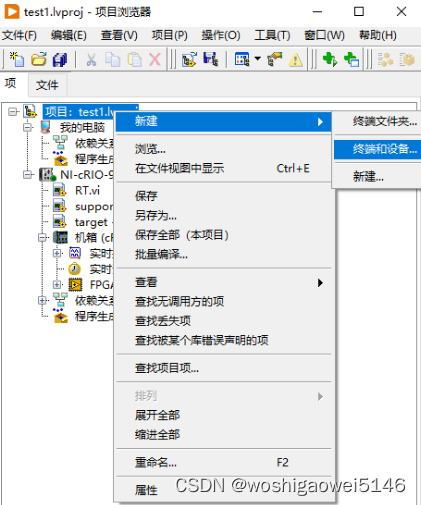

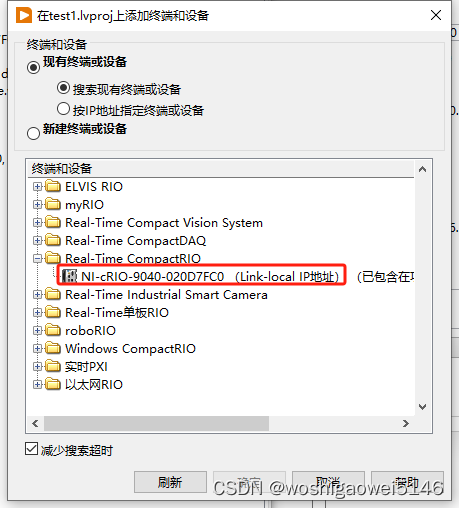

首先新建终端

由于NI9381仅支持扫描模式和FPGA模式,故测试这两种模式。(NI-DAQmx API不用)

C Series Module and CompactDAQ or CompactRIO Hardware Compatibility with LabVIEW

实时扫描模式

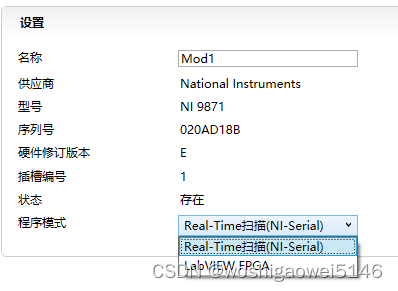

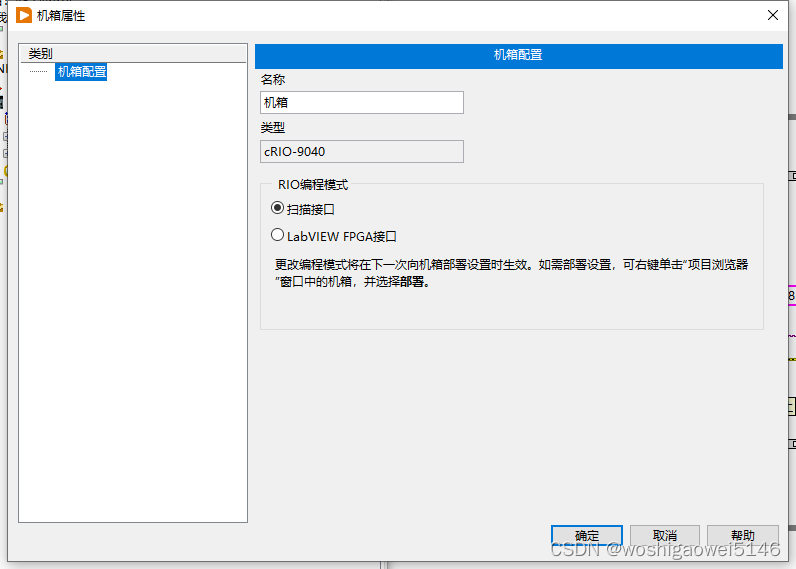

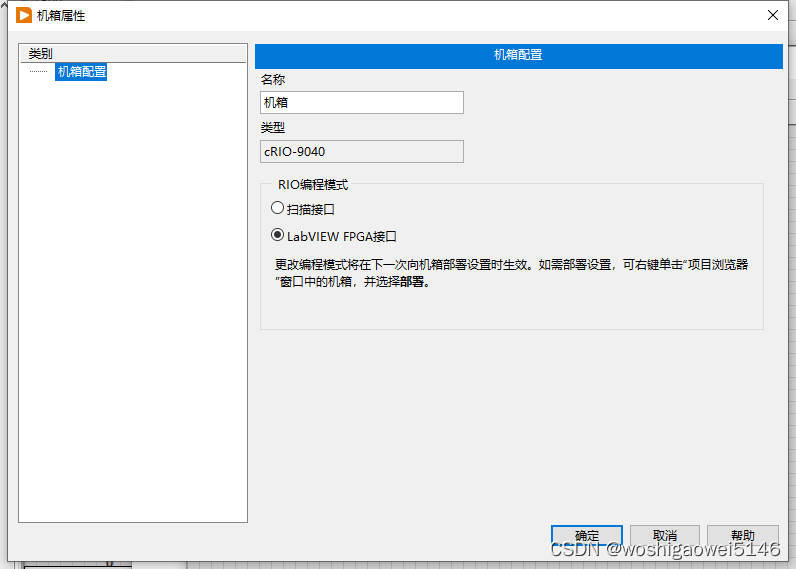

在机箱属性中,选择扫描接口

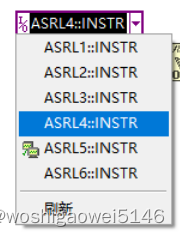

直接在cRIO下新建VI,方法和串口通信一样,选择串口号时,前两个是机箱上的串口,后面4个串口就是NI9871的4个串口。

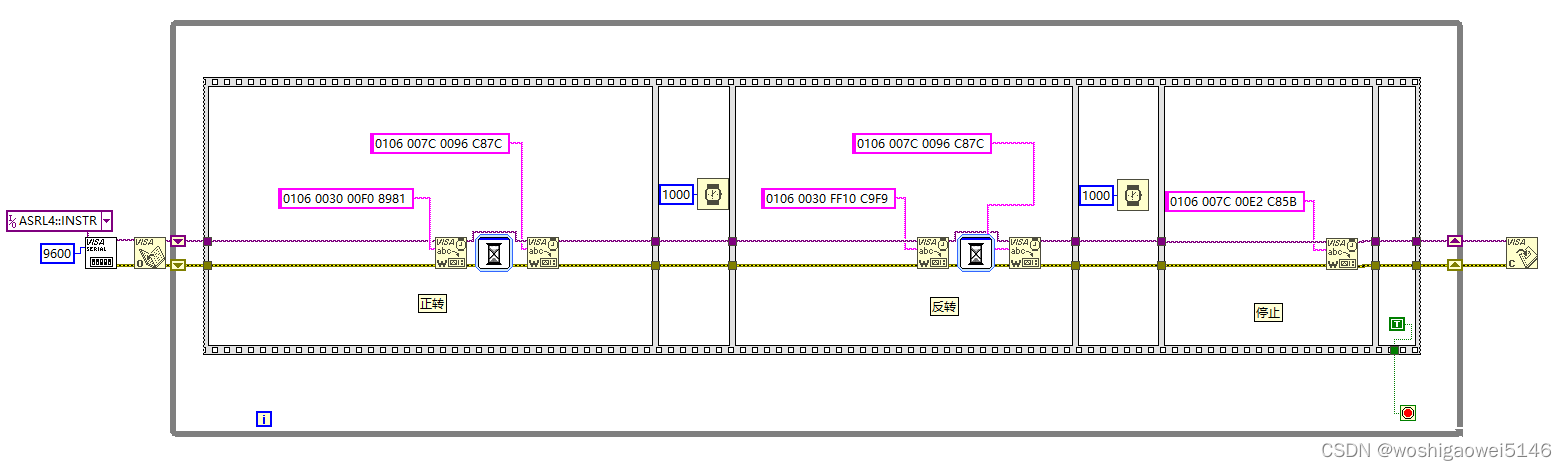

简单测试了正转、反转、停止。

具体指令参考:Modbus_Manual_CN202203.pdf

FPGA模式-中断模式

前期步骤同上,机箱属性编程模式更改为FPGA接口。

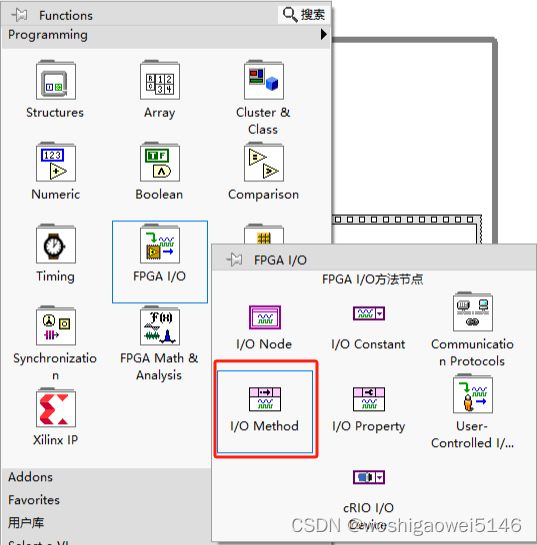

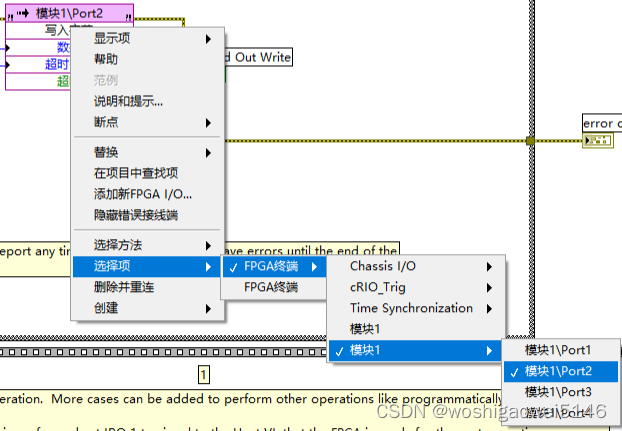

该设备不支持FPGA I/O 节点,所以无法拖入,直接创建method选择写入方法

在C:\Program Files\NI\LVAddons\crio\1\examples\CompactRIO\Module Specific\NI 987x\Serial Loopback中可参考NI-987x Serial Loopback例程。

由于自己利用例程新建项目时出现找不到op control 属性的问题,最后干脆直接在例程基础上修改了。(把例程文件的只读属性取消了,备份一份)

首先把例程中cRIO模块属性的IP修改为自己的设备,并且连接。

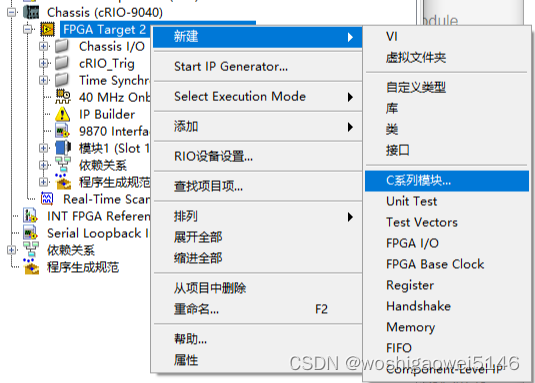

移除原来的9870模块,在FPGA中重新添加自己的9871模块。

打开9870 Interface Interrupt (FPGA).vi修改为9871的对应端口

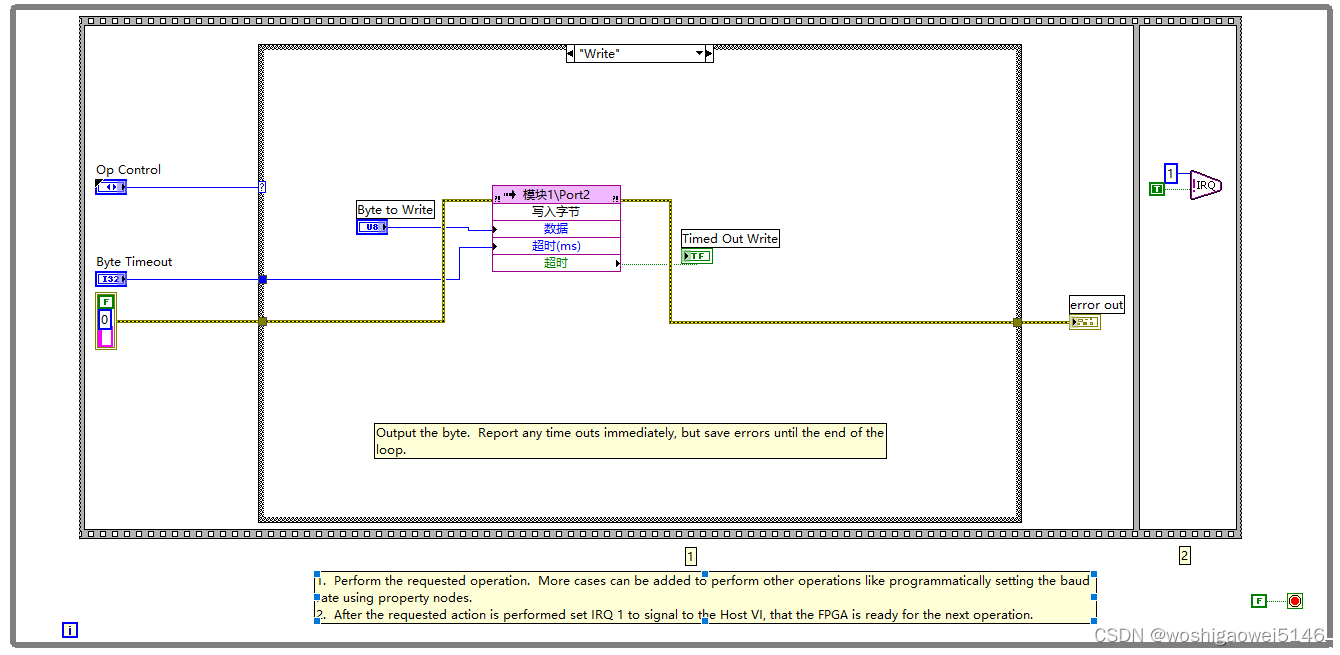

修改好以后编译FPGA程序,这里FPGA程序执行所请求的动作后,将IRQ 1设置为向主机VI发出信号,表明FPGA已准备好进行下一次操作。

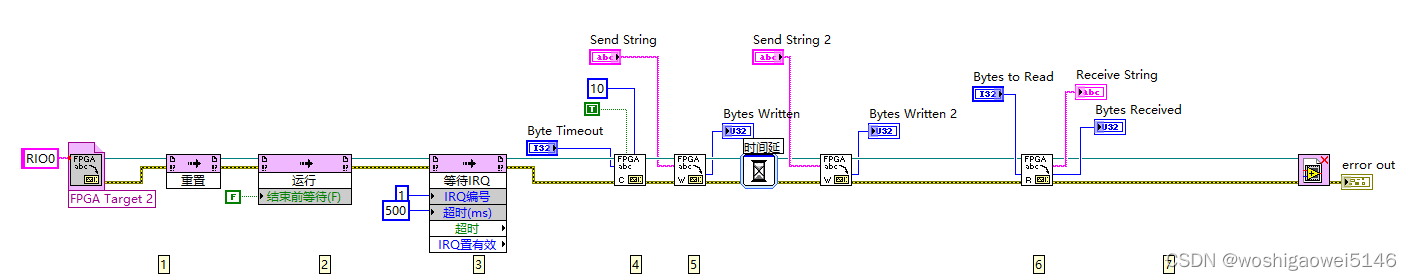

打开Serial Loopback Interrupt (Host).vi进行修改,把两次write中间增加约100ms的延时,将发送格式转为16进制。

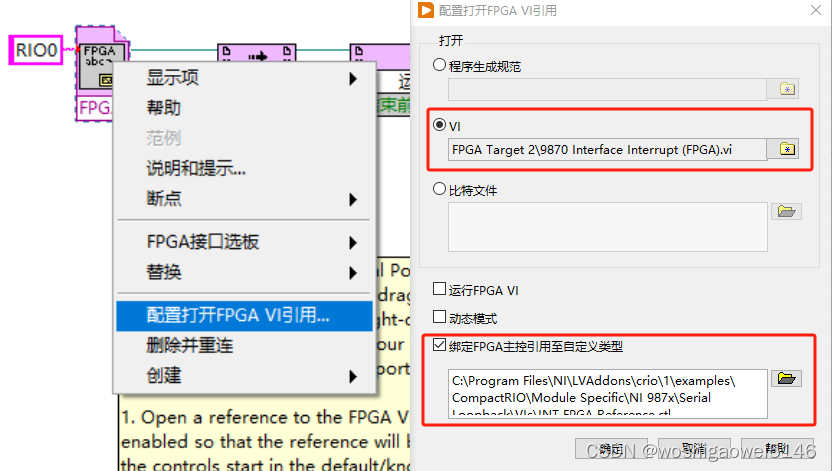

配置FPGA VI引用,选择之前编译好的FPGA程序并绑定引用至自定义类型 用来将FPGA VI引用作为接口。

运行Host程序,电机即可正反转。

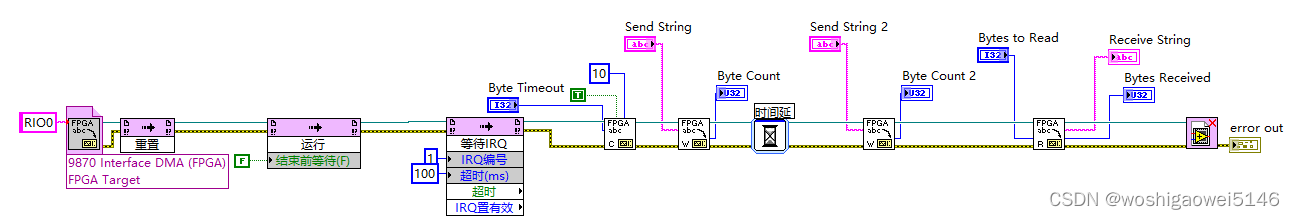

FPGA模式-DMA模式

步骤同前类似,修改9870 Interface DMA (FPGA).vi为9871的对应端口

这里新建两个FIFO ,READ_FIFO用于从Target to Host,WRITE_FIFO用于从 Host to Target 。

写入时,主机将要写入字节先传入WRITE_FIFO然后再给9871的写入字节方法。

读取时,将9871读取的字节传入READ_FIFO,再传给主机。

打开Serial Loopback DMA (Host).vi同样进行修改,把两次write中间增加约100ms的延时,将发送格式转为16进制。

运行Host程序,电机即可正反转。

参考

在扫描模式下发现,配置NI 987x模块并与之通信

NI 9871 (Scan Interface)

NI 9871 (FPGA Interface)

C Series Serial Module Error Codes

99

99

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?