一、有限状态机定义

有限状态机(Finite-State Machine,FSM),又成为有限状态自动机,简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型。笔者常在电机控制、通信协议解析等应用场景下应用FSM。 本文所讲的是基于硬件描述语言Verilog HDL的有限状态机的编写技巧及规范。众所周知FPGA以其并行性和可重构性为世人所知,而在当今的电子世界,基本所有的器件都是串行的,所以作为控制单元或者是可编程单元的FPGA需要进行并行转串行与外界进行通信、控制等,而有限状态机以其简单实用、结构清晰而恰如其分的充当着这个角色。

有限状态机是由寄存器组和组合逻辑构成的硬件时序电路,其状态(即由寄存器组的1和0的组合状态所构成的有限个状态)只可能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态,究竟转向哪一状态还是留在原状态不但取决于各个输入值,还取决于当前所在状态。

二、设计思想:

状态机的本质是对具有逻辑顺序或时序规律事件的一种描述方法。这个论断的最重要的两个词就是“逻辑顺序”和“时序逻辑”,这两点就是状态机所要描述的核心和强项,换言之,所有具有逻辑顺序和时序规律的事情都适合用状态机描述。

状态机的两种应用思路。第一种思路,从状态变量入手。如果一个电路具有时序逻辑或者逻辑顺序,我们就可以自然而然地规划出状态,从这些状态入手,分析每个状态的输入,状态转移和输出,从而完成电路功能;第二种思路,需要首先明确电路的输出关系,这些输出相当于状态的输出,回溯规划每个状态,和状态转移条件与状态输入。两种思路殊途同归,都要通过使用状态机的目的来达到控制某部分电路的目的,完成某种具有逻辑顺序或时序规律的电路设计。

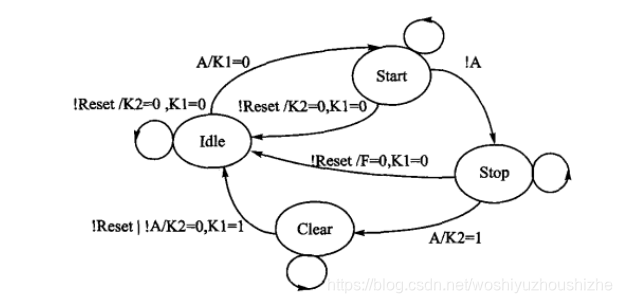

在设计状态机之前首先应该画出问题的状态转移图,状态转移图的例子如下所示:

三、状态机分类:

(1):mealy型和moore型

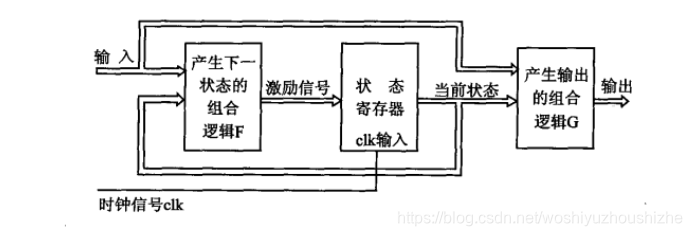

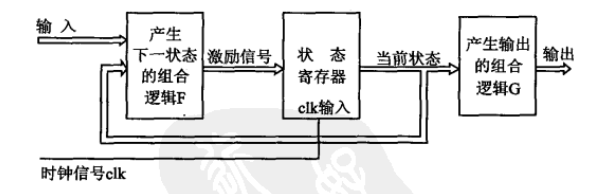

状态机有两大类:Mealy型和Moore型。Moore型状态机的输出只与当前状态有关,而Mealy型状态机的输出不仅取决于当前状态,还受到输入的直接控制,并且可能与状态无关,其状态机结构请看下图:

Mealy型状态机结构图

Moore型状态机结构图

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1062

1062

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?