一、制作3-8译码器

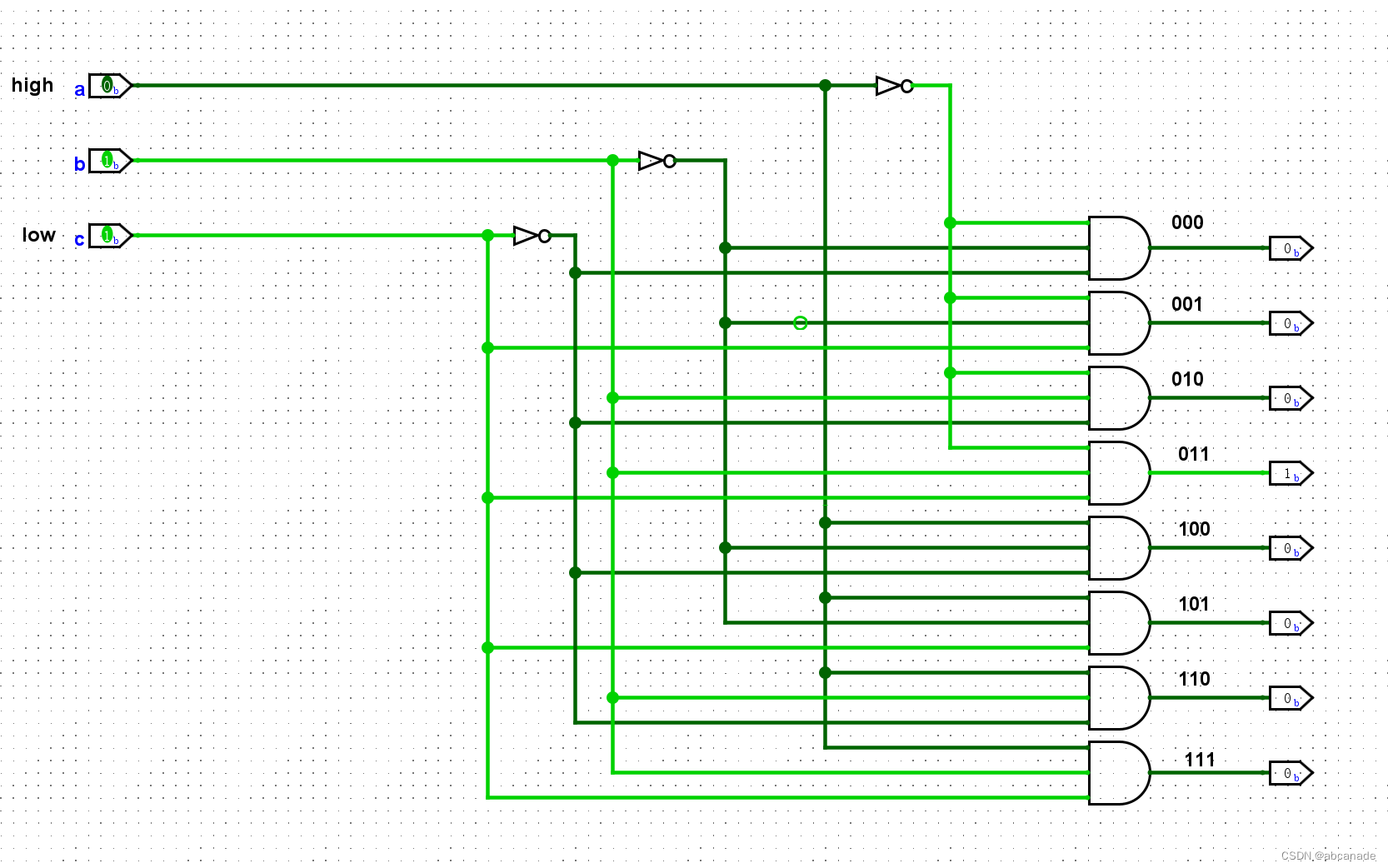

1、使用Logsim绘制一个3-8译码器电路图

2、列出3-8译码器的逻辑真值表。

| 输入 | 输出 | ||

|---|---|---|---|

| a | b | c | out |

| 0 | 0 | 0 | 0000_0001 |

| 0 | 0 | 1 | 0000_0010 |

| 0 | 1 | 0 | 0000_0100 |

| 0 | 1 | 1 | 0000_1000 |

| 1 | 0 | 0 | 0001_0000 |

| 1 | 0 | 1 | 0010_0000 |

| 1 | 1 | 0 | 0100_0000 |

| 1 | 1 | 1 | 1000_0000 |

3、然后采用Verilog编程设计一个3-8译码器

代码如下:

module D3_8(

a,

b,

c,

out

);

input a; //输入端口a

input b; //输入端口b

input c; //输入端口c

output [7:0]out;//输出端口out

reg [7:0]out;

always@(a,b,c)

begin

case({a,b,c})

3'b000:out = 8'b0000_0001;

3'b001:out = 8'b0000_0010;

3'b010:out = 8'b0000_0100;

3'b011:out = 8'b0000_1000;

3'b100:out = 8'b0001_0000;

3'b101:out = 8'b0010_0000;

3'b110:out = 8'b0100_0000;

3'b111:out = 8'b1000_0000;

endcase

end

endmodule

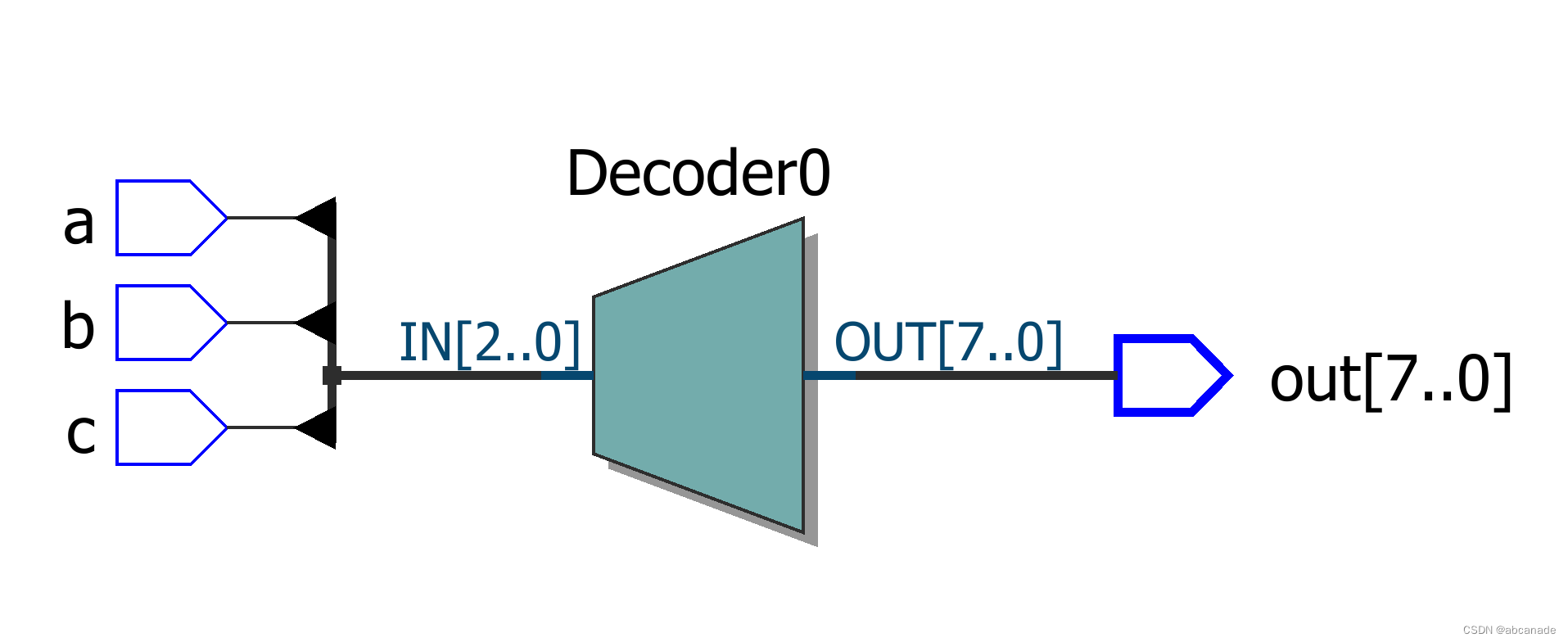

4、生成RTL原理电路图

5、编写一个仿真测试文件

timescale 1ns/1ns

module three_to_eight_tb();

reg a;

reg b;

reg c;

wire [7:0] out;

initial begin

a <= 1'b1;

b <= 1'b0;

c <= 1'b1;

end

//a:产生随机数,模拟 a 的输入情况

always #10 a <= {$random} % 2;

//b:产生随机数,模拟 b 的输入情况

always #10 b <= {$random} % 2;

//c:产生随机数,模拟c 的输入情况

always #10 c <= {$random} % 2;

initial begin

$timeformat(-9, 0, "ns", 6);

$monitor("@time %t:a=%b b=%b c=%b out=%b",$time,a,b,c,out);

end

three_to_eight three_to_eight_ins

(

.a(a),

.b(b),

.c(c),

.out(out)

);

endmodule

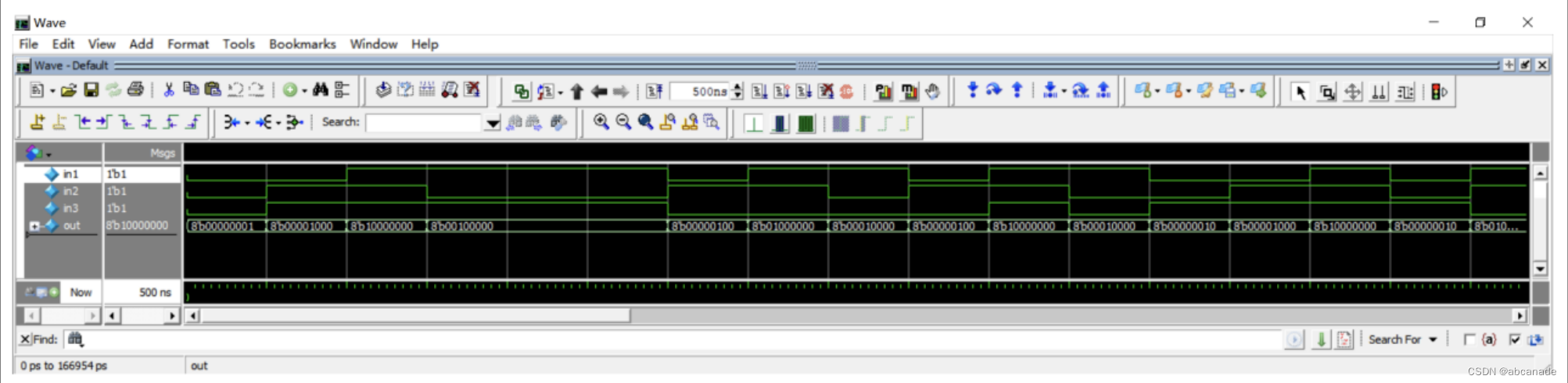

6、仿真波形分析

RTL 代码设计完成后,按照流程编写 Testbench,然后启动 ModelSim 进行仿真测试验证,同样我们也让波形跑了500ns,通过图所示的波形我们可以观察到,3 个输入的 in 均为任意随机数,所以由 in 组成的 3bit 数据也为随机数,而每个随机数都对一个 out 输出的 8bit 值,我们仔细核对输入 in 和输出 out 之间的对应关系,发现波形中 3 个输入 信号 in 与输出信号 out 之间的对应关系和编写的代码中的译码关系是完全一致的,完全符合我们代码中的逻辑设计。

7、问题

1、Verilog 综合生成的3-8译码器电路原理图与原始设计电路存在什么差异? 仿真测试生成的结果是否与真值表一致?

使用不同的技术库或综合设置可能会导致综合工具做出不同的选择,从而产生差异。在Verilog设计中,仿真测试应该与真值表一致。

2、Verilog代码设计的3-8译码器模块的输出信号 为何要定义为 reg类型而不用默认wire(导线)类型?改成wire型是否可以? (即是否可以把 output reg [7:0] out 改为 output [7:0] out) 修改后会出现什么错误?为什么会出错?

在Verilog中,reg类型并不一定表示物理上的寄存器,而是用来表示可以在always块中被赋值的变量。wire类型则用来表示连续赋值的信号,通常与assign语句一起使用,或者用于连接模块的输入输出端口。如果将output reg [7:0] out改为output [7:0] out,并且在代码中使用了always块来赋值,那么在编译时会出现错误,因为只有、reg类型的变量才能在always块中被赋值。

端口。如果将output reg [7:0] out改为output [7:0] out,并且在代码中使用了always块来赋值,那么在编译时会出现错误,因为只有、reg类型的变量才能在always块中被赋值。

1070

1070

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?