建立差分对约束:

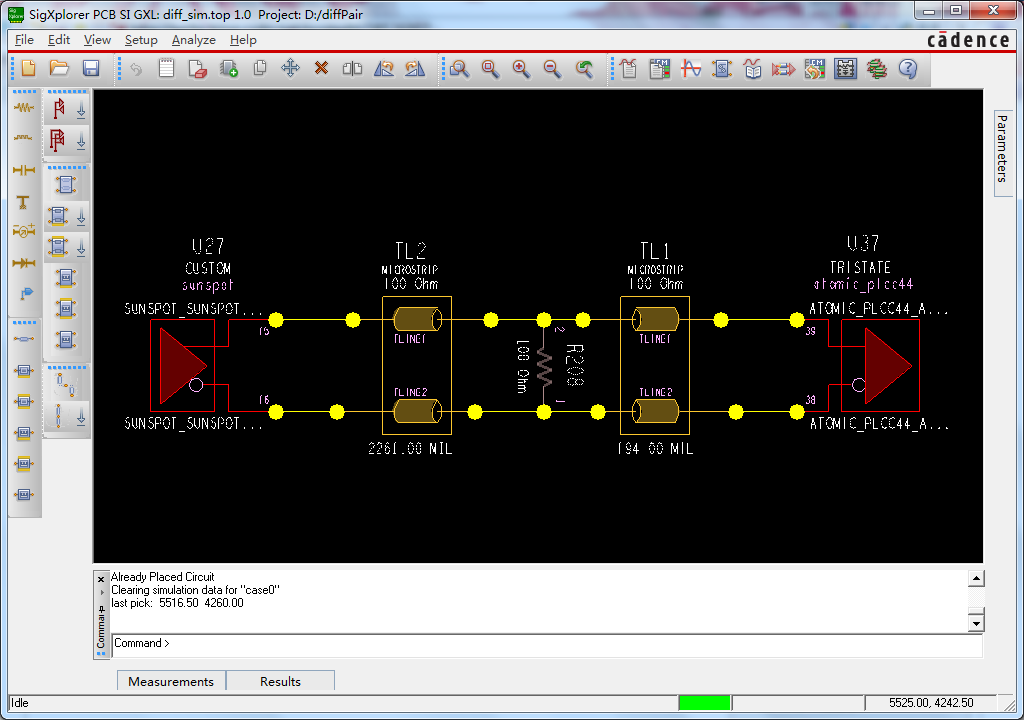

(1)设置差分对约束,从SigXplorer PCB SI GXL打开diff_sim.top拓扑。

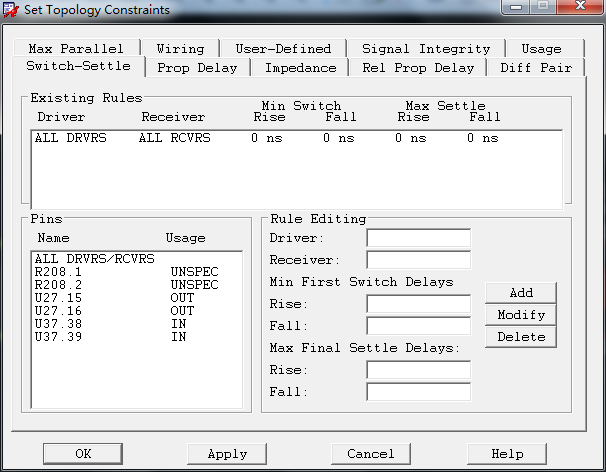

(2)执行Setup-Constraints,弹出Set Topology Constraints对话框

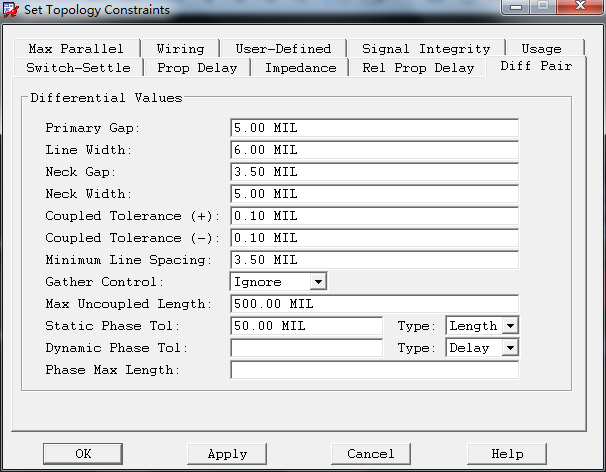

(3)选择Diff Pair标签页,设置如图:

(4)单击OK,关闭对话框,File->Save,保存拓扑,File->Exit。

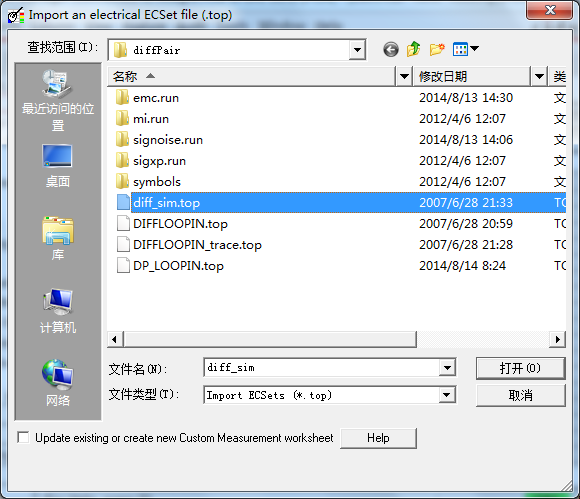

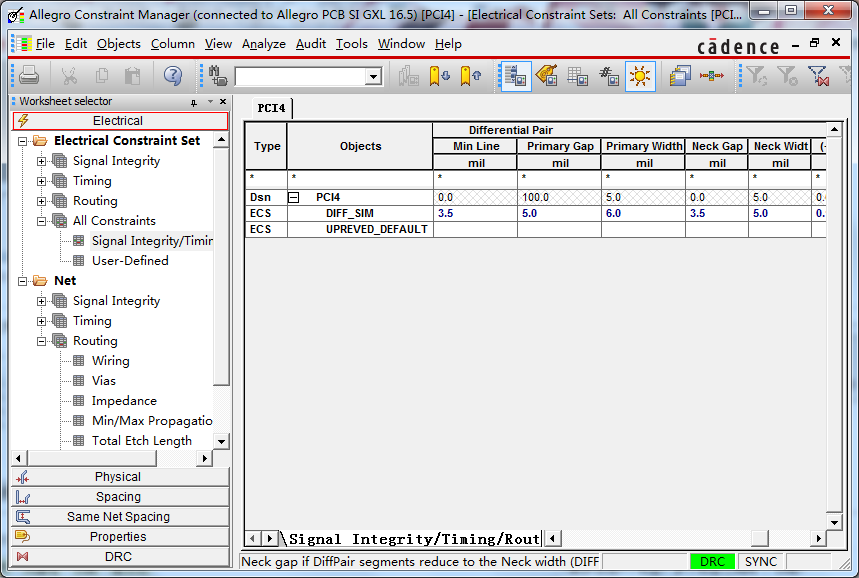

(5)应用差分对拓扑,打开Allegro Constraint Manager窗口,执行File-Import-Electrical CSets,弹出对话框,双击diff_sim.top。

(6)在Allegro Constraint Manager窗口双击Electrical Constraint Set-All Constraints的表格符号,可以查看所有约束。

本文详细介绍了在信号完整性中建立差分对约束的步骤,包括使用SigXplorer打开拓扑、设置差分对约束、在Allegro Constraint Manager中导入并应用约束,确保差分对的正确路由和配置。

本文详细介绍了在信号完整性中建立差分对约束的步骤,包括使用SigXplorer打开拓扑、设置差分对约束、在Allegro Constraint Manager中导入并应用约束,确保差分对的正确路由和配置。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8175

8175

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?