一、实验目的

1. 掌握数字加法器的工作原理和逻辑功能。

2. 熟悉VIVADO集成开发环境。

3. 熟悉VIVADO中进行开发设计的流程。

二、实验环境

1. 装有ModelSim和VIVADO的计算机。

2. Sword实验系统。

三、实验任务

1. 用VerilogHDL语言设计实现4位串行数字加法器和4位并行加法器,在ModelSim上仿真实现。

2. 生成FPGA设计文件,下载到Sword实验系统上验证电路功能。

四、实验原理与实验步骤

1. 实验原理

数字加法器是一种较为常用的逻辑运算器件,被广泛用于计算机、通信和多媒体数字集成电路中。广义的加法器包括加法器和减法器,在实际系统中加法器输入通常采用补码形式。此次实验仅考虑加法运算,分别完成4位的串行进位加法器设计和4位的并行进位加法器设计。

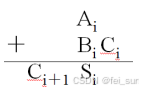

(1) 1 bit全加器

最简单的一位全加器的结构,设定两个二进制数字Ai,Bi和一个进位输入Ci 相加,产生一个和输出Si ,以及一个进位输出Ci+1。

Si = Ai⊕Bi⊕Ci

Ci+1= AiBi+BiCi+CiAi

= AiBi+﹙Ai⊕Bi﹚Ci

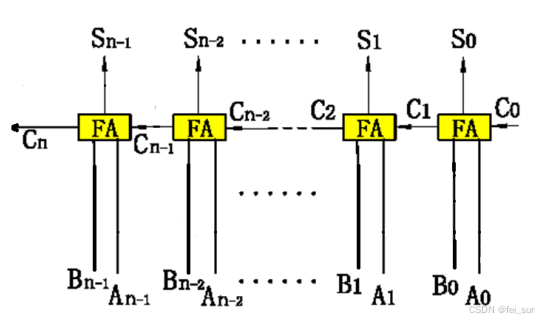

(2) 4位串行进位加法器

n位串行进位全加器原理示意图

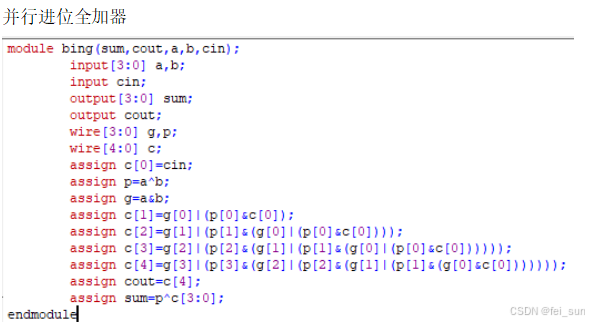

(3) 4位并行进位加法器

超前进位加法器是一种高速加法器,每级进位由附加的组合电路产生,高位的运算不需等待低位运算完成,因此可以提高运算速度。

各级进位信号表达式的推导过程

Ci+1 = AiBi+(Ai⊕Bi)Ci

设: Gi = AiBi Pi = Ai ⊕Bi

则有: Si = Pi ⊕Ci

Ci+1 = Gi+PiCi

4位并行进位的逻辑表达式为:

C0

C1= G0+P0C0

C2= G1+P1C1 = G1 + P1(G0+P0C0)

= G1+ G0P1+P0P1C0

C3= G2+P2C2 = G2 + P2(G1+G0P1+P0P1C0)

= G2+ G1P2+G0P1P2+P0P1P2C0

C4= G3+P3C3 = G3 + P3(G2+…+P0P1P2C0)

= G3+G2P3+G1P2P3+G0P1P2P3+P0P1P2P3C0

2. 实验步骤

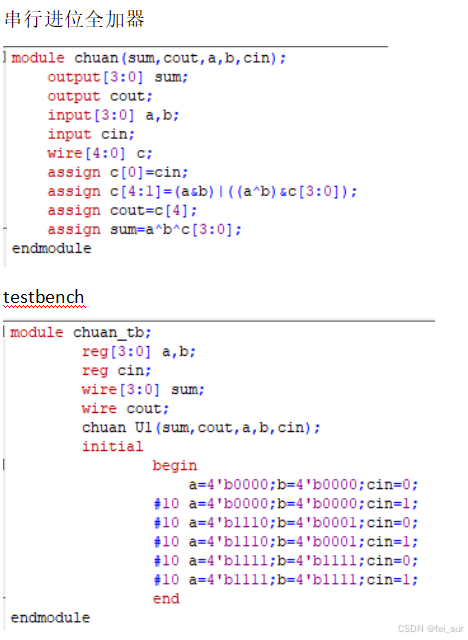

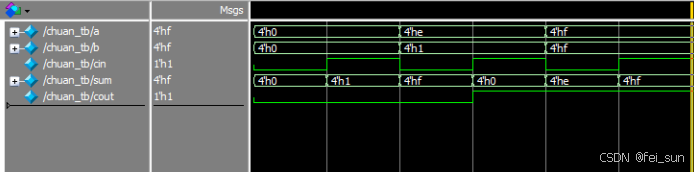

(1)用连续赋值语句实现4位串行进位的全加器,并完成modelsim下的功能仿真。

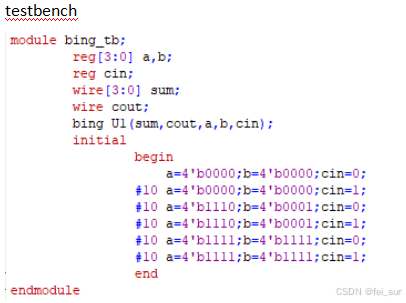

(2)用连续赋值语句实现4位并行进位的全加器,并完成modelsim下的功能仿真。

用相同的激励向量的话,仿真结果相同

(3)设计完成I/O引脚分配,选择sw0-sw3给出第一个加数,sw4-sw7给出第二个加数,sw[15]为Ci的输入,运算结果在LED以及数码管上显示。

xc7k160tffg676-1

top.v

`timescale 1ns / 1ps

module TOP(input wire clk_100mhz,

input wire[15:0]SW,

output wire seg_clk,

output wire seg_clrn,

output wire seg_sout,

output wire SEG_PEN ,

output wire led_clk,

output wire led_clrn,

output wire led_sout,

output wire LED_PEN

);

wire[31:0]Div;

wire[15:0]LED_DATA;

wire CK;

clk_div U8(clk_100mhz,1'b0,SW[2],Div,CK);

LED_P2S #(.DATA_BITS(16),.DATA_COUNT_BITS(4))

PLED (clk_100mhz,

1'b0,

Div[20],

LED_DATA,

led_clk,

led_clrn,

led_sout,

LED_PEN

);

P2S #(.DATA_BITS(64),.DATA_COUNT_BITS(6))

P7SEG (clk_100mhz,

1'b0,

Div[20],

disp_data,

seg_clk,

seg_clrn,

seg_sout,

SEG_PEN

);

wire[3:0] out;

wire[7:0] out1;

wire cout;

wire[3:0] cout1;

wire[7:0] cout2;

chuan U9(out,cout,SW[3:0],SW[7:4],SW[15]);

//bing U10(out,cout,SW[3:0],SW[7:4],SW[15]);

shumaguan U11_1(.out(out1),.in(out));

wire[7:0] Seg0=out1;

wire[3:0] cout1={3'b000,cout};

shumaguan U11_2(.out(cout2),.in(cout1));

wire[7:0] Seg1=cout2;

wire[63:0] disp_data = {Seg0,Seg1,48'hffffffffffff};

assign LED_DATA = ~{out[0],out[1],out[2],out[3],cout,1'b0,1'b0,1'b0,1'b0,1'b0,1'b0,1'b0,1'b0,1'b0,1'b0,1'b0};

endmodule

chuan.v

module chuan(sum,cout,a,b,cin);

output[3:0] sum;

output cout;

input[3:0] a,b;

input cin;

wire[4:0] c;

assign c[0]=cin;

assign c[4:1]=(a&b)|((a^b)&c[3:0]);

assign cout=c[4];

assign sum=a^b^c[3:0];

endmoduleshumaguan.v

module shumaguan(in,out);

output[7:0] out;

input[3:0] in;

reg[7:0] out;

always@(in)

begin

case(in)

4'b0000: out=8'b00000011;

4'b0001: out=8'b10011111;

4'b0010: out=8'b00100101;

4'b0011: out=8'b00001101;

4'b0100: out=8'b10011001;

4'b0101: out=8'b01001001;

4'b0110: out=8'b01000001;

4'b0111: out=8'b00011111;

4'b1000: out=8'b00000001;

4'b1001: out=8'b00001001;

4'b1010: out=8'b00010001;

4'b1011: out=8'b11000001;

4'b1100: out=8'b01100011;

4'b1101: out=8'b10000101;

4'b1110: out=8'b01100001;

4'b1111: out=8'b01110001;

default: out=8'b0;

endcase

end

endmodule

1097

1097

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?