HDMI 显示实现的方案同 LVDS 一样,只是 HDMI 采用自带的 DVI TX IP 实现并行 RGB 转

TMDS 协议,点亮 HDMI 接口的显示器,需要注意的是 HDMI 的并行时钟和串行时钟除以 5

实现的,此部分可以阅读代码和官方的 DVI TX IP 文档,文档有详细介绍。

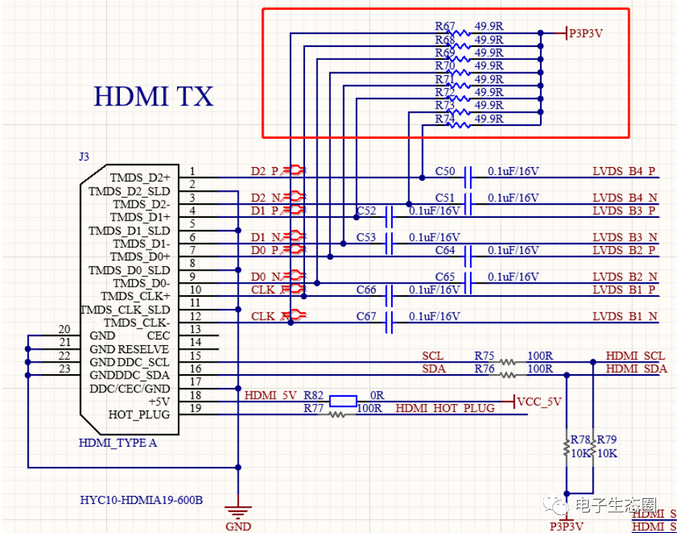

硬件设计上需要注意 HDMI TX 的应用,框起来的部分需要上拉到 3.3V,LVDS 的 Bank

电压也需要是 3.3V 才行。

使用Verilog实现测试图的生成,使用dvi ip实现RGB转HDMI的输出

dvi_tx DVI_TX_Top_inst

(

.I_rst_n (hdmi4_rst_n ), //asynchronous reset, low active

.I_serial_clk (serial_clk ),

.I_rgb_clk (pix_clk ), //pixel clock

.I_rgb_vs (tp0_vs_in ),

.I_rgb_hs (tp0_hs_in ),

.I_rgb_de (tp0_de_in ),

.I_rgb_r (tp0_data_r ),

.I_rgb_g (tp0_data_g ),

.I_rgb_b (tp0_data_b ),

本文介绍了如何使用HDMI接口进行显示,涉及DVITXIP协议的转换以及Verilog在生成测试图中的应用,重点讲解了RGB信号如何转换为TMDS以驱动显示器。同时,提到了同步/异步reset和像素时钟在硬件设计中的注意事项。

本文介绍了如何使用HDMI接口进行显示,涉及DVITXIP协议的转换以及Verilog在生成测试图中的应用,重点讲解了RGB信号如何转换为TMDS以驱动显示器。同时,提到了同步/异步reset和像素时钟在硬件设计中的注意事项。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5376

5376

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?