正弦信号产生实验

实验目标

1.首先设计一个DDS, 50MHz的时钟速率,输出波形频率自行设定

2.DDS的输出数据格式为2补码,相位累加器32比特ROM波表尺寸和波形量化比特数自己决定

3.首先在Signaltap里,观察波形的正确性,然后把Signaltap的数据导入到Matlab,分析频域结果

基础知识

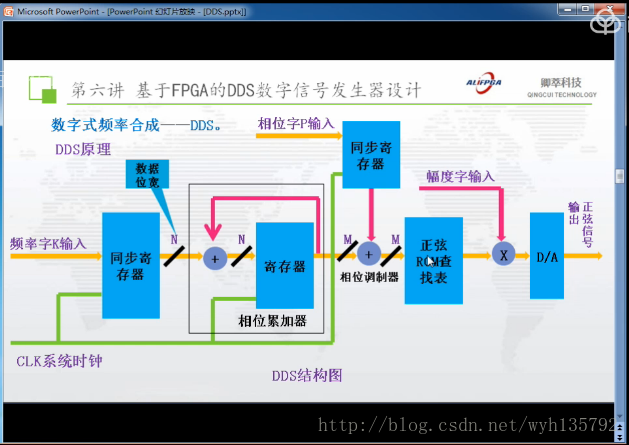

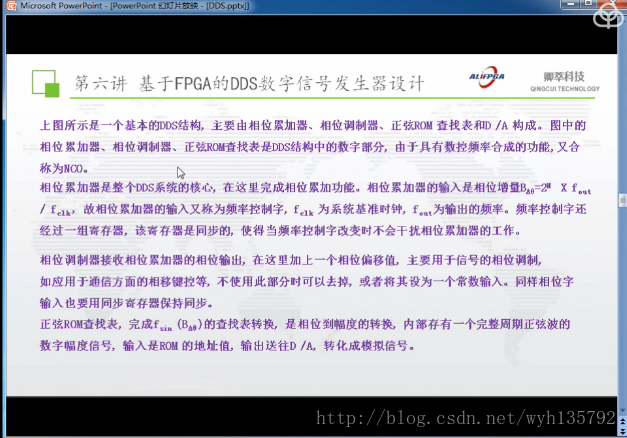

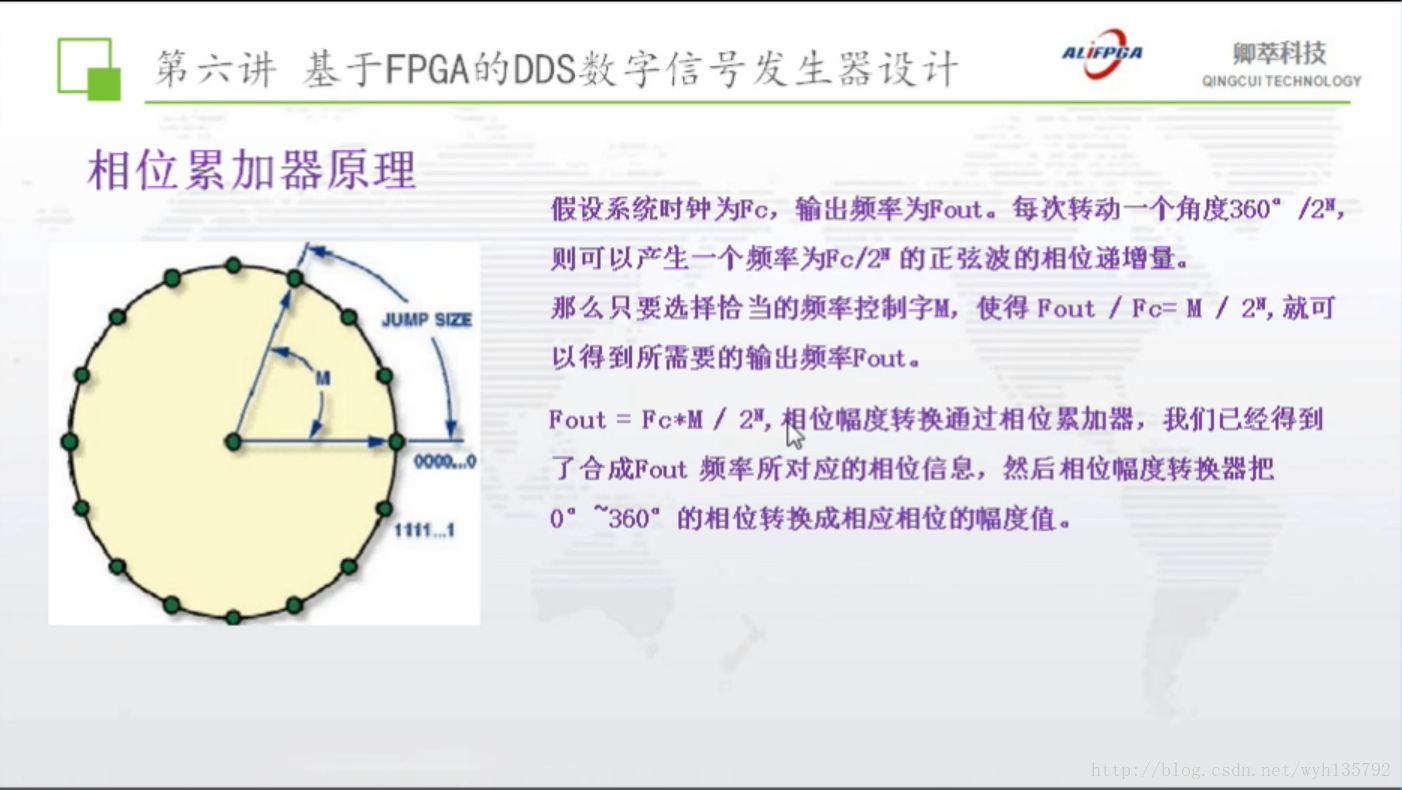

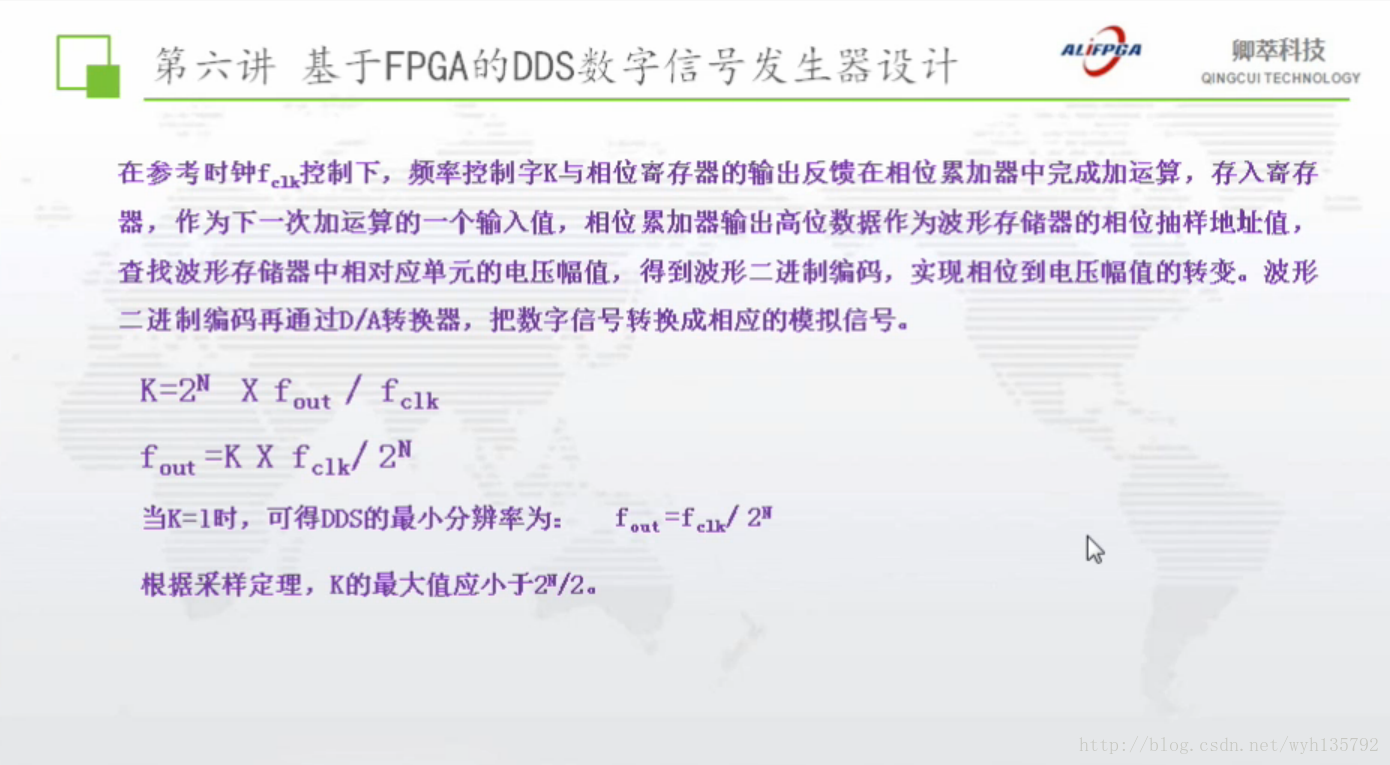

DDS的工作原理:输出频率由频率控制字决定,公式如下:

为输出频率,为时钟频率=50MHz,K为频率控制字,N为相位累加器的位数32。当输出频率500KHz,1MHz时,其对应的频率字分别为32’h028F_5C29、32’h028F_5C29 * 2,因此本实验中设定输出频率为500KHz。波形量化比特数为12bit,ROM波表尺寸为10bit地址。

实验代码:

module dds(

CLK , // clock, posedge valid

RST , // reset, high level reset

FWEN , // frequency word update enable, high level enable

//FWIN ,

addr_R, // input frequency word

CLKOUT, // output clock

SINOUT); // sine signal output, 2's complement format

input CLK;

input RST;

input FWEN;

//input [32-1:0] FWIN;

output [9:0] addr_R;

output[12-1:0] SINOUT;

output CLKOUT;

parameter FW_WL = 32; // frequency word word length in bit

parameter RA_WL = 10; // rom address word length in bit

parameter RD_WL = 12; // rom data word word length in bit

parameter VAL_FREQ_500K = 32'h028F_5C29;

reg [FW_WL -1:0] fwin_R; // freq word DFF

reg [FW_WL -1:0] acc_R; // phase ACC DFF

reg [RA_WL -1:0] addr_R; // rom address DFF

reg [RD_WL -1:0] sinout_R; // sin wave output DFF

wire [RD_WL -1:0] romout_W; // rom data output wire

always @ (posedge CLK or posedge RST) begin

if(RST) begin

fwin_R <= 0;

acc_R <= 0;

addr_R <= 0;

sinout_R <= 0;

本次实验旨在设计一个DDS系统,使用50MHz时钟产生不同频率的正弦波。通过Signaltap观察波形正确性,并在Matlab中进行频域分析。实验中,相位累加器为32位,频率控制字决定输出频率,如500KHz时对应的频率字为32'h028F_5C29。波形量化比特数为12bit,ROM波表尺寸为10bit地址。

本次实验旨在设计一个DDS系统,使用50MHz时钟产生不同频率的正弦波。通过Signaltap观察波形正确性,并在Matlab中进行频域分析。实验中,相位累加器为32位,频率控制字决定输出频率,如500KHz时对应的频率字为32'h028F_5C29。波形量化比特数为12bit,ROM波表尺寸为10bit地址。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5974

5974

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?