Sitara™处理器的产品开发路线图

概述

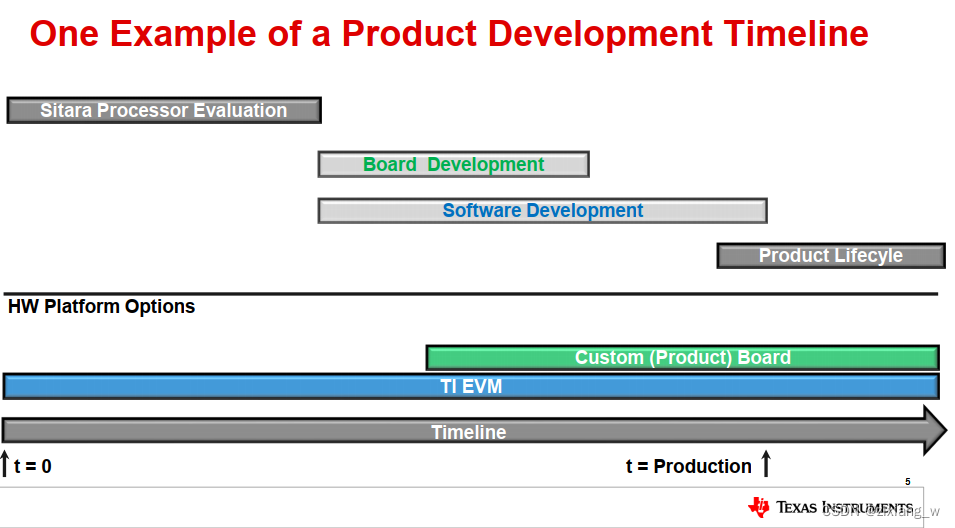

一般情况下,会存在四个主要的发展阶段,其中TI EVM为我们提供了良好的软硬件基础,可以在不同的阶段进行参考和验证。

Evaluation Phase(评估阶段)

这个阶段主要是根据应用场景和要求选择合适的处理器,可以参考的资料有:

- Data Sheet

- 处理器支持的频率

- 可供使用的外设

- DDR支持的 Memory 类型

- 电源和时钟功能

- Technical Reference Manual(TRM)

- 是对DataSheet的补充指导

- 详细介绍了设备中每个外设和子系统的集成、环境、功能描述和编程模型

- 白皮书

- 应用手册

- 硬件设计指导

- 原理图检查表

- EMIF Tool

- 技术文章

- SYSCONFIG TOOL

- 软件工具,提供图形用户界面配置引脚多路复用设置,解决冲突

- 对特定应用程序可能的引脚多路复用配置执行“what-if”

总结:

- 使用数据表和技术参考手册确定处理器兼容性

查看可用的应用说明, - 使用SYSCONFIG工具评估可能的引脚多路复用输出,以确定“如果”处理器配置

- 审查TI参考设计,以确定要在新产品中使用的设计元素

- 使用TI评估模块和RTOS和Linux软件开发工具包进行实验,以评估处理器功能

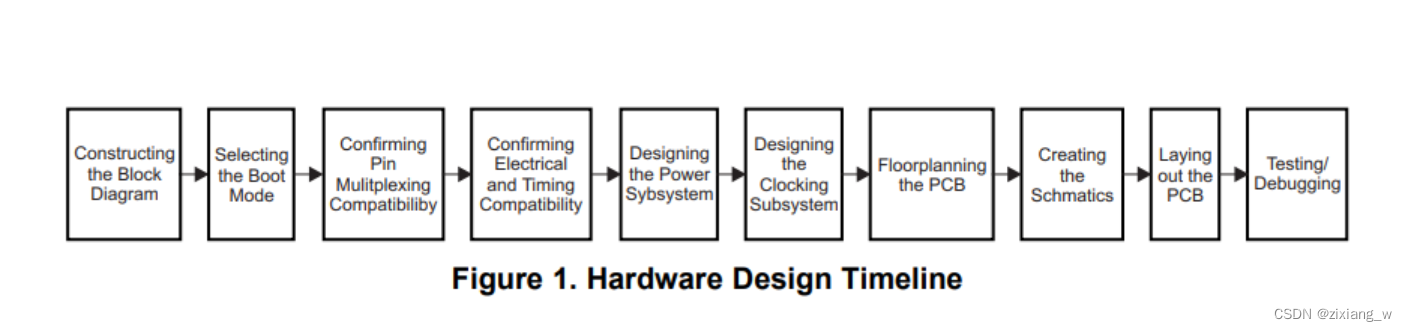

Board Development Phase(硬件发展阶段,硬件设计人员应重点关注这个阶段)

Constructing the Block Diagram 参考:

- DataSheet

- Device interconnections

- Electrical & Timing requirements

- Pin Muxing

- Power

- DDR Memory Interfacing

- TRM

- Boot Modes

- Peripheral Clocking and operations

- Control Module, register descriptions

Confirming Pin Mulitplexing Compatibility :使用SYSCONFIG TOOL

Confirming Electrical and Timing Compatibility:使用IBIS Models for Timing Analysis

Creating the Schmatics:参考Schematics Checklist

Laying out the PCB: 参考High Speed Interface Layout Guidelines

总结:

- 遵循硬件设计指南中显示的步骤

- 利用处理器产品文件夹中提供的文档

- 使用数据表和TRM创建系统框图

- SYSCONFIG工具,EMIF工具有助于确定引脚多路配置

Software Development Phase(软件发展阶段)

- Software Development RTOS

- 健壮的实时TI-RTOS内核,包括TCP/IP网络堆栈

- Posix线程兼容的API层可用

- 可以使用的驱动程序库

- TI-RTOS或不带内核

- 免费并开放源代码

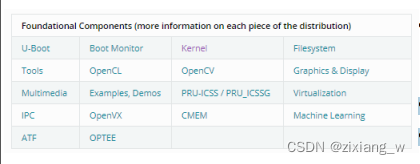

- Software Development Linux

总结: - TI为每个处理器提供RTOS和Linux SDK操作系统

- sdk为应用开发提供了起点

- 应该使用SYSCONFIG和EMIF工具来加速将操作系统移植到新板上

1140

1140

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?