目录

前言

DSP的中断默认是不可嵌套的,即当执行某个中断服务函数时,即使有更高优先级的中断触发,也需要等待当前中断执行完后才可响应。近来工作需要保证TMS320F28377D的IPC中断优先执行,即使当前正在执行其它中断也需要挂起,优先执行IPC中断。

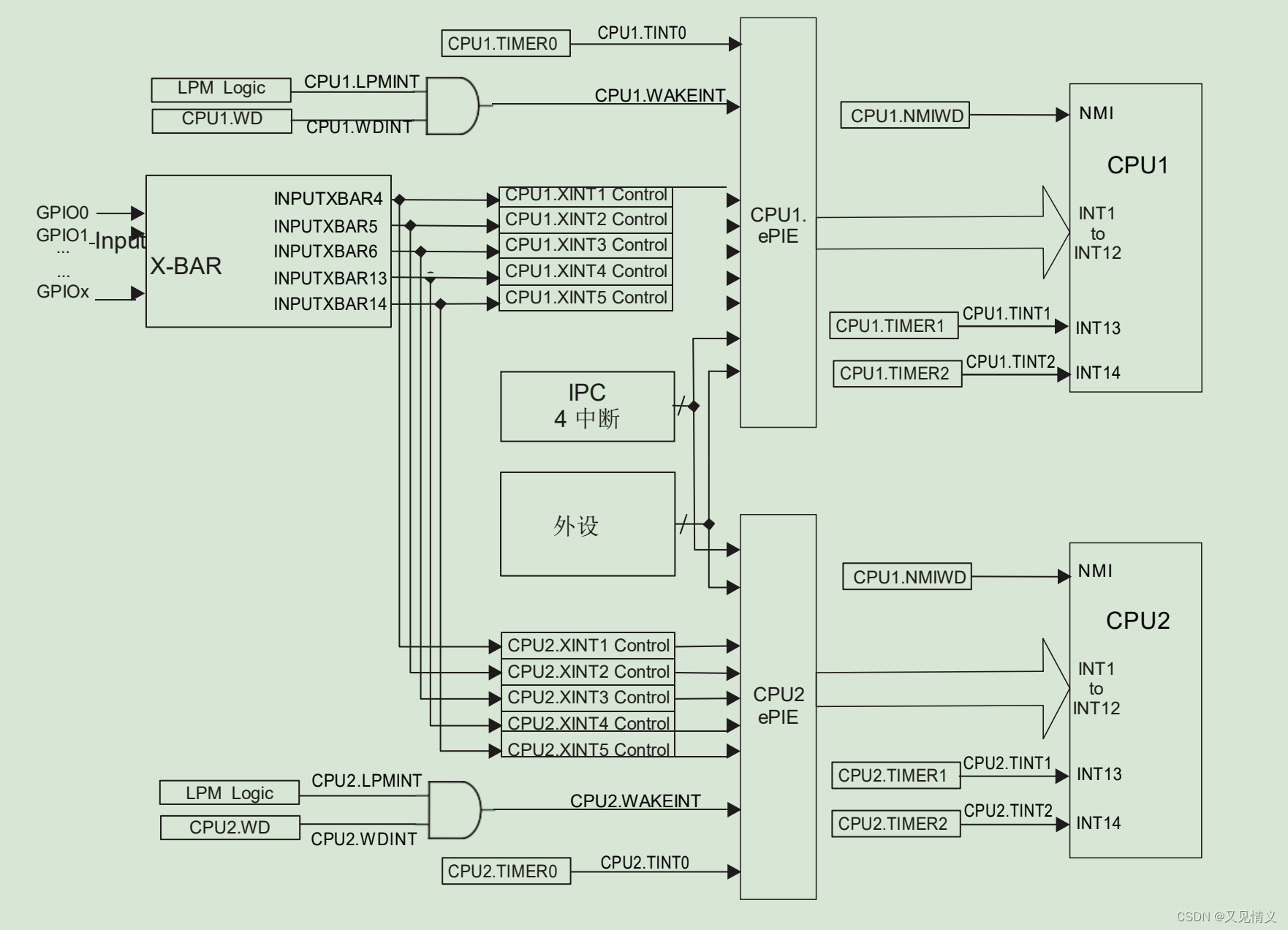

28377D的CPU有14个外设中断线,其中两个(INT13和INT14)分别直接连接到CPU定时器1和2.其余12个通过增强型外设中断扩展模块(ePIE)连接到外设中断信号。CPU内核有IER中断使能寄存器和IFR中断标志寄存器,这两个十六位的寄存器的低十四位分别对应INT1到INT14的中断使能和中断标志。如果使用的是新的driverlib库,在cpu.h文件中有如下声明,可直接代码中对IER和IFR寄存器读写。

#ifndef _TMS320C28XX_CLA_

extern _cregister volatile uint16_t IFR;

#endif

#ifndef _TMS320C28XX_CLA_

extern _cregister volatile uint16_t IER;

#endif

PIE将多达16个外设中断复用到每个CPU中断线上,它还扩展中断向量表,以允许每个中断具有自己的ISR,这允许CPU支持大量的外设。

中断路径位外设->PIE->CPU,每个级都有自己的使能和标志寄存器,该系统在处理一个中断时,其它可屏蔽中断是禁止的,需要在软件中实现嵌套中断,并在某些关键任务期间禁用中断。

设备中断架构

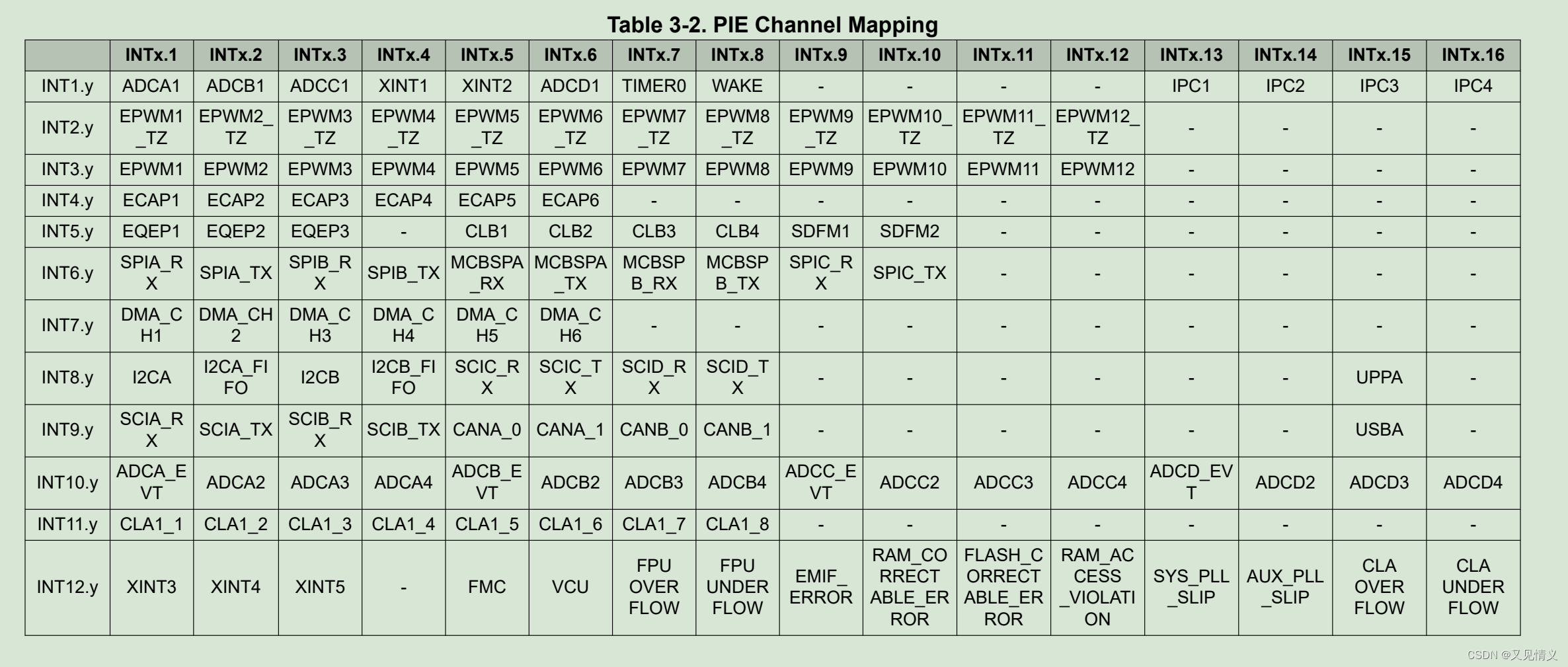

28377D的PIE有12组,每组有16个通道中断,其中断优先级如下表从上往下优先级逐减,从左往右优先级逐减,即左上优先级最高,右下优先级最低。

PIE的寄存器如下

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?