文章目录

1. 什么是中断

中断是硬件和软件驱动事件,它使得CPU暂停当前的主程序,转而去执行一个中断服务子程序。X281x的中断系统从上至下分成了三级,即CPU级中断、PIE级中断、外设中断。

2. CPU中断

通常中断申请信号是由外围设备提出的,表示一个特殊的时间已经发生,请求CPU暂停正在执行的主程序,去处理相应的更为紧急的事件。

2.1 CPU中断的概述

中断的触发有两种:一种是在软件中写指令,例如INTR、OR IFR或者TRAP指令;另一种是硬件方式触发,例如来自片内外设或者外设设备的中断信号,表示某个事件已经发生。

无论是软件中断还是硬件中断,都可以归结为可屏蔽中断和不可屏蔽中断。

| 中断类型 | 中断信号 | 特点 |

|---|---|---|

| 不可屏蔽中断 | INTR指令和TRAP指令、硬件中断NMI、非法指令陷阱以及硬件复位中断 | 一旦中断申请信号发出,CPU必须无条件的立即去响应 |

| 可屏蔽中断 | 大部分的中断 | CPU检查这个中断的使能情况,决定是否响应中断 |

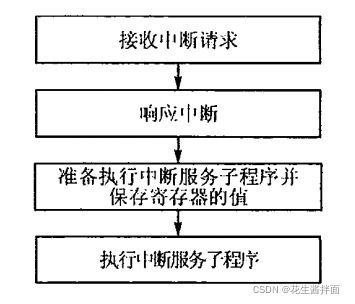

接受到中断信号后,CPU会按照以下4个步骤来处理中断:

- 接收中断信号:外设或者其他方式向CPU提出中断请求。

- 响应中断:如果是个可屏蔽中断,会检查它的使能情况,决定是否响应,如果是不可屏蔽中断,就立即响应。

- CPU会完整地执行当前指令,为了记住当前主程序的状态,CPU必须做一些准备工作,例如将寄存器的内容存放到堆栈。

- 准备工作做完之后,CPU就取回中断向量,开始执行中断服务子程序。

2.2 CPU中断向量和优先级

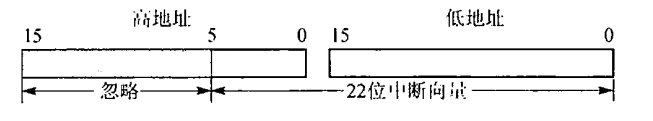

X2812支持32个CPU中断,其中每一个中断都是一个32位的中断向量,即两个16位的寄存器,里面存储的是相应中断服务子程序的入口地址,这个入口地址是个22位的地址。

2.3 CPU中断的寄存器

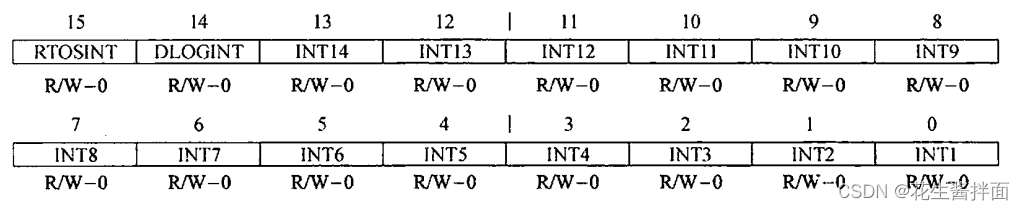

CPU中断里,INT1-INT14是14个通用中断,DLOGINT数据标志中断和RTOSINT实时操作系统中断是为仿真而设计的两个中断。这16个中断都是可屏蔽中断,通过CPU中断使能寄存器IER就可以实现使能或者禁止中断。

| 寄存器 | 位数 | 功能 |

|---|---|---|

| 中断使能寄存器IER | 16 | 使能或者禁止可屏蔽中断 |

| 标志寄存器IFR | 16 | 表示对应CPU中断是否提出请求 |

2.4 可屏蔽中断的响应过程

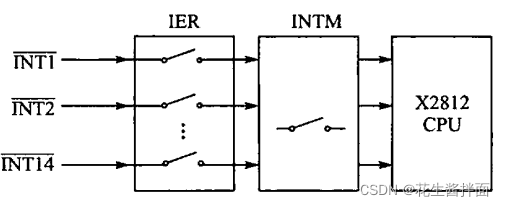

可屏蔽中断的响应过程如上图所示。、

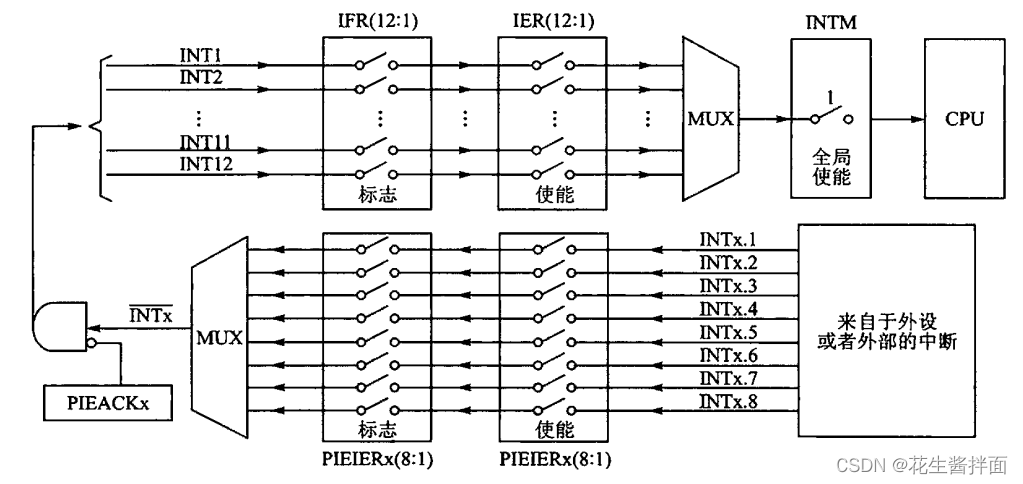

- 某个可屏蔽中断提出请求时,将其在IFR中的对应位置位;

- CPU检测到中断标志位被置位后,接着检测该中断是否被使能;

- 如果IER中对应位被使能,CPU检查全局中断INTM是否被使能;

- 如果INTM被使能,CPU响应中断,暂停主程序并转向执行相应的中断服务子程序。

2.5 X2812的PIE中断

上图是DSP的中断源,CPU共有16根中断线,包括2个不可屏蔽中断RS和NMI,以及14各个可屏蔽中断INT1-INT14。

3.1 PIE中断概述

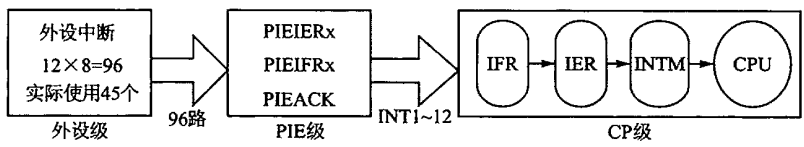

DSP内部有很多可以产生中断的外设,为了能够及时地处理好各个外设的请求,专门增添了处理外设中断的扩展模块,简称外设中断控制器PIE。

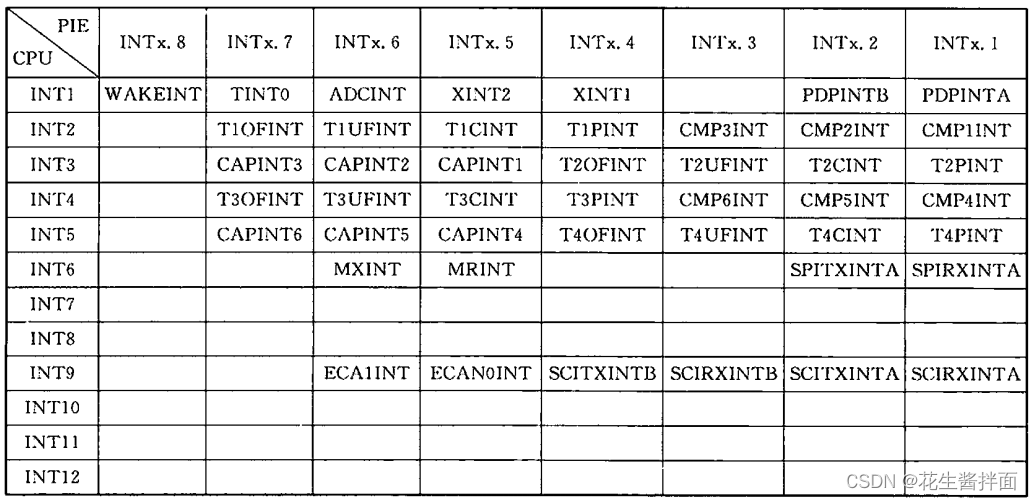

PIE一共可以支持96个不同的中断,将这些中断分成了12个组,每个组8个中断,每个组都被反馈到CPU内核的INT1-INT12这12条中断线中的某一条线上。

在12条中断线中,INT1的优先级最高,INT12的优先级最低,同一组内,INTx.1的优先级最高。

3.2 PIE中断寄存器

| 寄存器名称 | 大小 | 说明 |

|---|---|---|

| PIECTRL | 16 | PIE控制寄存器,保存从PIE向量表取回的向量地址 |

| PIEACK | 16 | PIE中断应答寄存器,表示每一组中断的CPU响应情况 |

| PIEIER1 | 16 | PIE,INT1组使能寄存器 |

| PIEIFR1 | 16 | PIE,INT1组标志寄存器 |

| … | ||

| PIEIER12 | 16 | PIE,INT12组使能寄存器 |

| PIEIFR12 | 16 | PIE,INT12组标志寄存器 |

3.3 PIE中断向量表

PIE一共可支持96个中断,每个中断都有中断服务子程序ISR,将这些子程序的地址存储在一片连续的RAM空间内,就是PIE中断向量表,它由256x16的RAM空间组成。

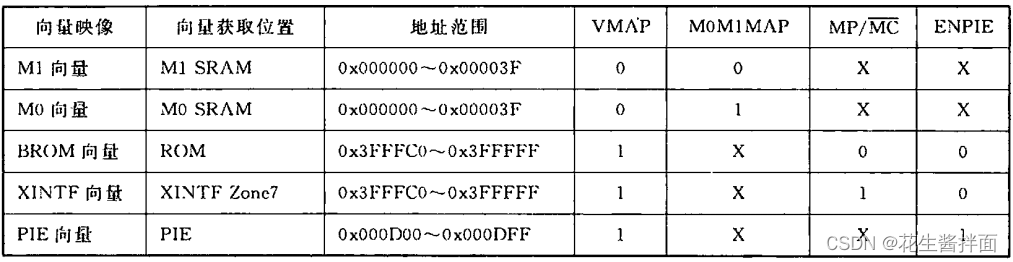

在DSP中,中断向量表可以映射到5个不同的存储空间,主要由以下几个信号来控制。

M1向量和M0向量仅留给TI测试用,VMAP值上电后是默认取1的,而初始化PIE时,会将ENPIE的值设为1,即F2812芯片正常情况下只使用PIE向量映射表。

4. X281x的三级中断系统分析

X281x采用的是如上图所示的三级中断机制,分为外设级、PIE级、CPU级,对于某一个具体的外设中断请求,只要有任一级不允许,CPU最终都不会响应该外设级中断。下面以CPU定时器0的周期中断为例。

4.1 外设级

- CPU定时器0的计数器寄存器TIMH:TIM计数到0时,就产生了一个T0INT时间,即CPU定时器0的周期中断;

- 若CPU定时器0的控制寄存器TIMER0TCR的第15位定时器中断标志TIF被置位为1,若第14位定时器中断使能位TIE也是1,就会向PIE控制器发出中断请求;

4.2 PIE级

- CPU定时器0的周期中断T0INT对应于PIEIFR1的第七位和PIEIER1的第七位;

- 由于PIE控制器是多路复用的,每一个组同一时间内只能有一个中断被响应,根据PIEACK各位的状态决定谁被响应;

4.3 CPU级

- CPU定时器0的周期中断T0INT发送到CPU,IFR的第0位INT1标志就会被置位,该状态锁存在IFR中;

- 检查IER寄存器中相关位的使能情况和CPU寄存器和CPU寄存器ST1中全局中断屏蔽位INTM的使能情况,如果都被置位,则响应中断;

- CPU将相应的IFR位进行清除,EALLOW清除,INTM置位,即不响应其他中断,存储返回地址并自动保存相关信息,例如将正在处理的数据放入堆栈;

- 从PIE向量表中取出对应的中断向量ISR,转而去执行中断服务子程序。

2743

2743

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?