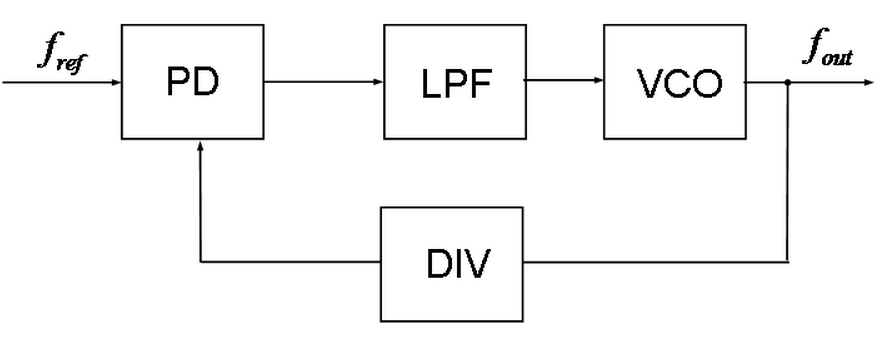

PLL就是Phase-locked loop,锁相环。在许多场合,我们需要获得一个和输入信号或者载波同频同相的本地信号,这就要用到PLL,它是当前频率合成常用手段之一。其结构如下:

PD是鉴相器,用于检测两个输入信号的相位差,有数字方式的也有模拟方式。模拟方式最好理解,设输入信号分别为cos(wt+a)和cos(wt+b),两者相位不同,经过一个乘法器:

cos(wt+a)*cos(wt+b)=0.5cos(2wt+a+b)+0.5cos(a-b)

这样我们就得到了一个直流分量0.5cos(a-b),只要后面的LPF能够将这个直流分量滤出来就可以控制VCO了。不过这种结构已经不用了,因为容易出现振幅调制现象。现在的鉴相器都采用数字结构,设计简单,效果也好。不过用这种原始的模拟方法来理解鉴相器的原理是个不错的选择。数字架构的鉴相器实现方式也有几种,时间原因,有机会再和大家探讨。

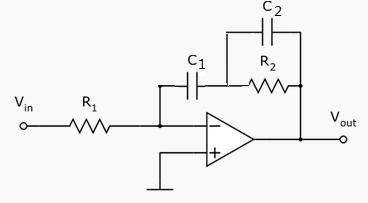

LPF滤波器,将鉴相器输出信号变为直流信号来控制VCO,滤波器大家应该都比较熟悉了,种类很繁多,设计技巧也太多了,一篇博文根本写不下,专著很多大家可以查阅,这里只是举个例子,如下图是一个运放构成的有源滤波器:

优点是可以有效驱动下一级的VCO,设计关键是带宽,如果带宽太窄,运放带来的相位滞后,很有可能导致整个电路的不稳定;与之相反,如果频带太宽引入的噪声有太大,需要相互兼顾,极端偏颇是行不通的。电路设计中这样的矛盾很多,如何拿捏那个度往往是设计的难题,但恰恰也正是电路设计的乐趣所在。

VCO压控振荡器,顾名思义就是振荡频率随输入电平改变。压控振荡器的形式种类纷繁复杂,各种结构也有各自的优缺点,在上一篇DIY功率表文章中就给出了一个晶振三点式振荡器,其原理简单,振荡稳定,但是很难量化计算电容的数值,只能粗略的计算一个范围,调试起来也相对于其他的RC,LC振荡器难度大一些。就像前辈们说的这是门艺术~

DIV分频器,这个可用的IC很多,电路也很简单,大家拿过来直接用就好了,在VHF频段这并不是设计难题,不过VHF并不是很高的频段,只有30MHz到300MHz,距离厘米波毫米波还远着呢,设计难度很低,随频率的提高,分频器的问题也有很多,功耗怎么解决,工作频段如何提升,都是很好的课题,之前也做了半年这方面的改进尝试,还是很有趣味很有挑战的。

最后,如何衡量一个PLL电路的好坏呢,主要是从以下三个方面着手,噪声、动态性能和稳定度,一款优秀的PLL在这三个方面应该都有比较好的表现。

624

624

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?