名称:16x16点阵滚动显示汉字Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

16x16点阵滚动显示汉字

要求:控制16x16点阵显示器显示汉字,并滚动显示

1. 工程文件

2. 程序文件

3. 程序编译

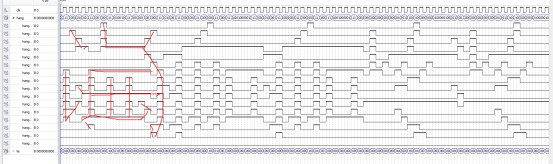

4. 仿真图

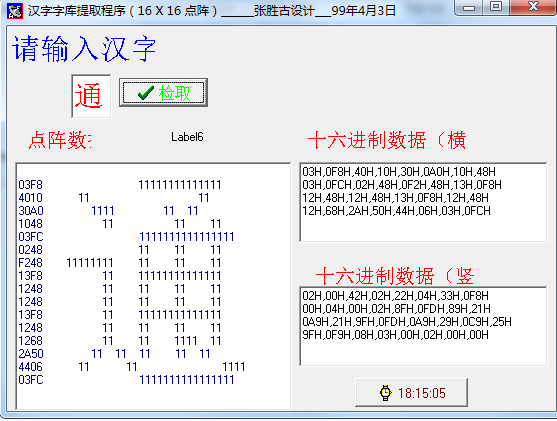

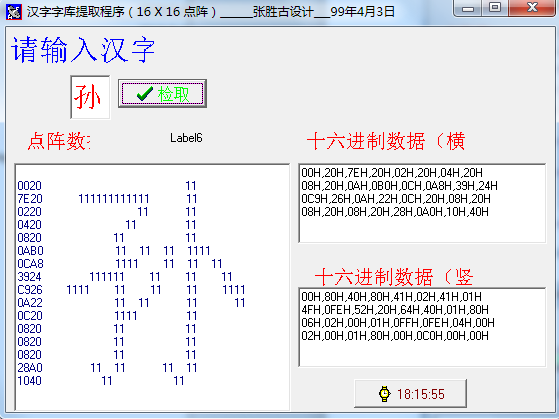

附字模软件

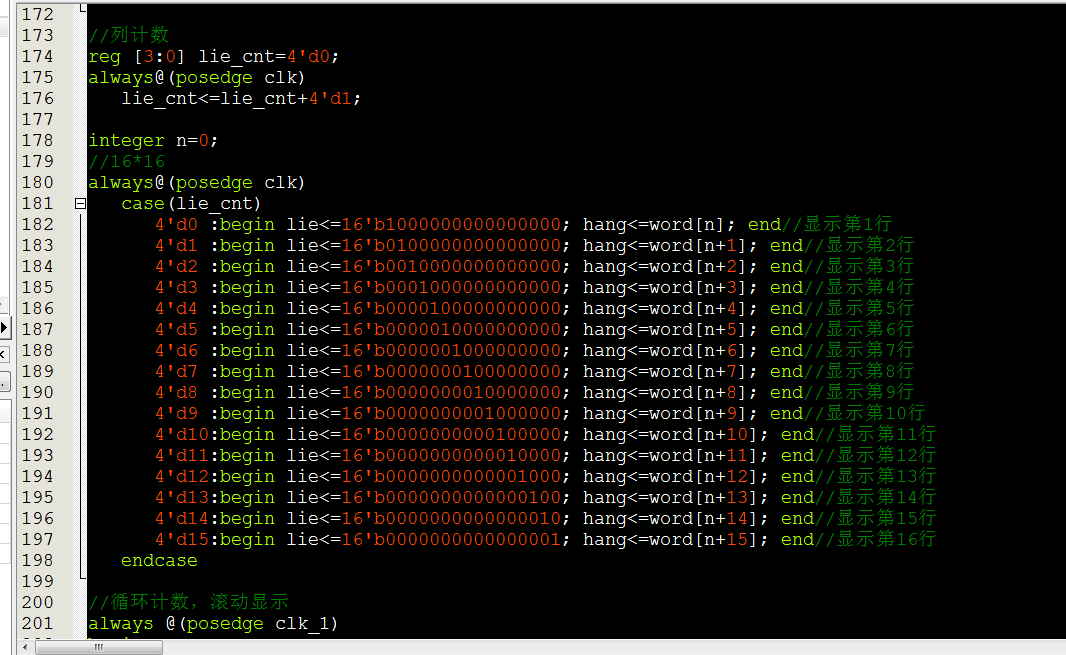

部分代码展示:

//滚动显示“通信孙晗” module led_16X16( input clk,//时钟 output reg [15:0] hang,//行 output reg [15:0] lie//列 ); //汉字1--通 //03H,0F8H,40H,10H,30H,0A0H,10H,48H //03H,0FCH,02H,48H,0F2H,48H,13H,0F8H //12H,48H,12H,48H,13H,0F8H,12H,48H //12H,68H,2AH,50H,44H,06H,03H,0FCH reg [15:0] word1_1=16'h03F8; reg [15:0] word1_2=16'h4010; reg [15:0] word1_3=16'h30A0; reg [15:0] word1_4=16'h1048; reg [15:0] word1_5=16'h03FC; reg [15:0] word1_6=16'h0248; reg [15:0] word1_7=16'hF248; reg [15:0] word1_8=16'h13F8; reg [15:0] word1_9=16'h1248; reg [15:0] word1_10=16'h1248; reg [15:0] word1_11=16'h13F8; reg [15:0] word1_12=16'h1248; reg [15:0] word1_13=16'h1268; reg [15:0] word1_14=16'h2A50; reg [15:0] word1_15=16'h4406; reg [15:0] word1_16=16'h03FC; //汉字2--信 reg [15:0] word2_1=16'h0880; reg [15:0] word2_2=16'h0844; reg [15:0] word2_3=16'h0FFE; reg [15:0] word2_4=16'h1000; reg [15:0] word2_5=16'h1008; reg [15:0] word2_6=16'h37FC; reg [15:0] word2_7=16'h5000; reg [15:0] word2_8=16'h9008; reg [15:0] word2_9=16'h17FC; reg [15:0] word2_10=16'h1000; reg [15:0] word2_11=16'h13F8; reg [15:0] word2_12=16'h1208; reg [15:0] word2_13=16'h1208; reg [15:0] word2_14=16'h1208; reg [15:0] word2_15=16'h13F8; reg [15:0] word2_16=16'h1208; //汉字3--孙 reg [15:0] word3_1=16'h0020; reg [15:0] word3_2=16'h7E20; reg [15:0] word3_3=16'h0220; reg [15:0] word3_4=16'h0420; reg [15:0] word3_5=16'h0820; reg [15:0] word3_6=16'h0AB0; reg [15:0] word3_7=16'h0CA8; reg [15:0] word3_8=16'h3924; reg [15:0] word3_9=16'hC926; reg [15:0] word3_10=16'h0A22; reg [15:0] word3_11=16'h0C20; reg [15:0] word3_12=16'h0820; reg [15:0] word3_13=16'h0820; reg [15:0] word3_14=16'h0820; reg [15:0] word3_15=16'h28A0; reg [15:0] word3_16=16'h1040; //汉字4--晗 reg [15:0] word4_1=16'h0040; reg [15:0] word4_2=16'h0840; reg [15:0] word4_3=16'h7CA0; reg [15:0] word4_4=16'h48A0; reg [15:0] word4_5=16'h4990; reg [15:0] word4_6=16'h4A4E; reg [15:0] word4_7=16'h4C04; reg [15:0] word4_8=16'h7BF0; reg [15:0] word4_9=16'h4820; reg [15:0] word4_10=16'h4848; reg [15:0] word4_11=16'h4BFC; reg [15:0] word4_12=16'h4A08; reg [15:0] word4_13=16'h7A08; reg [15:0] word4_14=16'h4A08; reg [15:0] word4_15=16'h03F8; reg [15:0] word4_16=16'h0208; reg [15:0] word [0:63]; //字符初始化 always@(posedge clk) begin word[0]<=word1_1; word[1]<=word1_2; word[2]<=word1_3; word[3]<=word1_4; word[4]<=word1_5; word[5]<=word1_6; word[6]<=word1_7; word[7]<=word1_8; word[8]<=word1_9; word[9]<=word1_10; word[10]<=word1_11; word[11]<=word1_12; word[12]<=word1_13; word[13]<=word1_14; word[14]<=word1_15; word[15]<=word1_16; word[16]<=word2_1; word[17]<=word2_2; word[18]<=word2_3; word[19]<=word2_4; word[20]<=word2_5; word[21]<=word2_6; word[22]<=word2_7; word[23]<=word2_8; word[24]<=word2_9; word[25]<=word2_10; word[26]<=word2_11; word[27]<=word2_12; word[28]<=word2_13; word[29]<=word2_14; word[30]<=word2_15; word[31]<=word2_16; word[32]<=word3_1; word[33]<=word3_2; word[34]<=word3_3; word[35]<=word3_4; word[36]<=word3_5; word[37]<=word3_6; word[38]<=word3_7; word[39]<=word3_8; word[40]<=word3_9; word[41]<=word3_10; word[42]<=word3_11; word[43]<=word3_12; word[44]<=word3_13; word[45]<=word3_14; word[46]<=word3_15; word[47]<=word3_16;

源代码

扫描文章末尾的公众号二维码

7万+

7万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?