名称:电梯请求显示系统Verilog代码Quartus 实验箱(文末获取)

软件:Quartus

语言:Verilog

代码功能:

电梯请求显示系统

二、题目要求:

(1)按键S1为一楼上行请求按钮,按键S2为二楼上行请求按钮,按键S3为三楼上行请求按钮,按键S4为四楼上行请求按钮,按键S5为五楼上行请求按钮,按键S6为六楼上行请求按钮;拨动开关K2为二楼下行请求按钮,拨动开关K3为三楼下行请求按钮,拨动开关K4为四楼下行请求按钮,拨动开关K5为五楼下行请求按钮,拨动开关K6为六楼下行请求按钮,拨动开关K7为七楼下行请求按钮;七段数码管显示当前电梯所在楼层数字(初始为4);每次只有一个有效请求(不用考虑优先级);当请求发出后,比较请求楼层和当前楼层数值,数码管按照电梯每秒升或降一层(1Hz)进行数值变换,直到显示楼层与请求楼层相等后停止,同时绿灯闪烁三次(4Hz)。

(2)外部输入脉冲信号频率为1mhz;

三、设计原理:

(1)计数:输入脉冲信号为1mhz,七段数码管显示改变为1s,需要计数脉冲信号或者设计分频器。

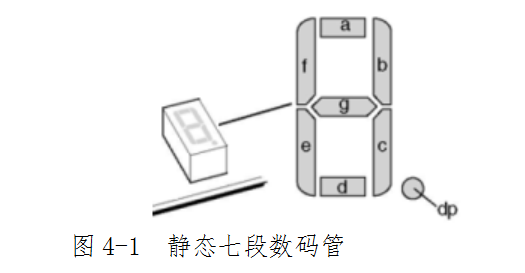

(2)七段数码管显示:七段数码管是电子开发过程中常用的输出显示设备。在实验系统中使用的是两个四位一体、共阴极型七段数码管。其单个静态数码管如下图4-1所示。

由于七段数码管公共端连接到GND(共阴极型),当数码管的中的那一个段被输入高电平,则相应的这一段被点亮。反之则不亮。共阳极性的数码管与之相么。四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

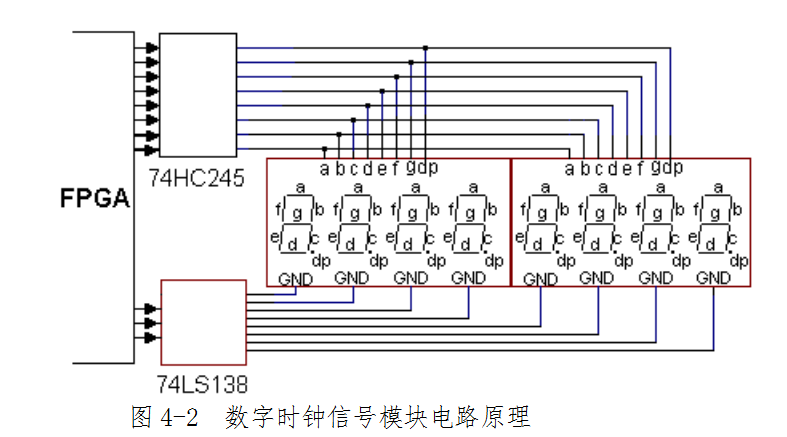

数码管显示模块的电路原理如图4-2所示,表4-1是其数码管的输入与FPGA的管脚连接表。

(3)消抖的原理:按键默认输入逻辑‘1’,当有按键按下时对应的输入为逻辑‘0’(但会存在抖动),当FPGA开始检测到该引脚从‘1’变为‘0’后开始定时(按键抖动时间大约10ms),定时时间结束后若该引脚仍然为‘0’则表示确实发生按键按下,否则视为抖动而不予以理会;按键松开过程的消抖处理和按下时原理一样。

基于VerilogHDL语言的电路设计、仿真与综合;主要包括:各个电路子模块的Verilog源文件、仿真文件,功能仿真波形;顶层设计的Verilog源文件、仿真源文件,功能仿真波形。

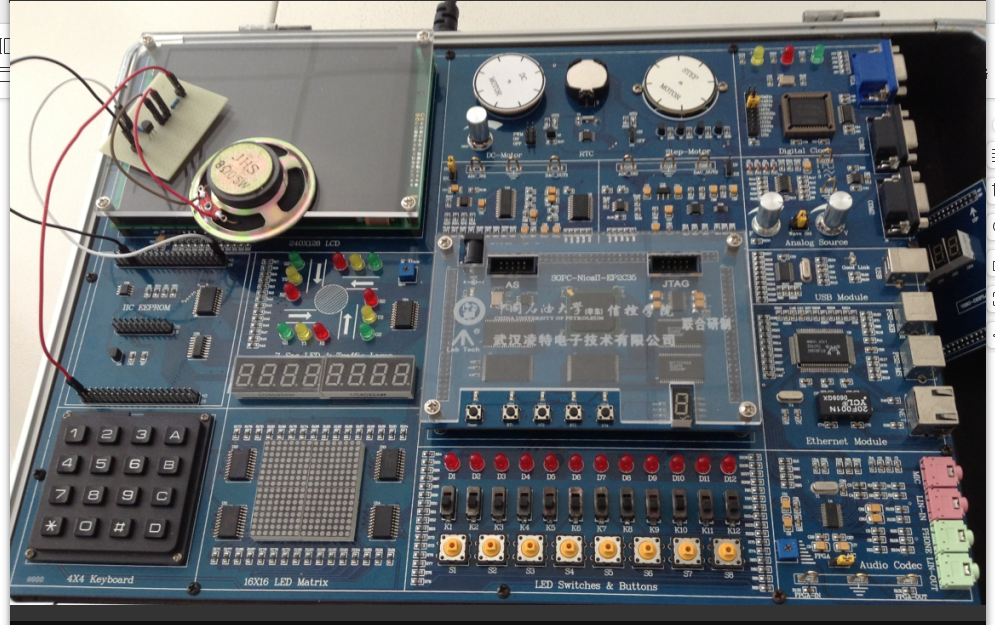

本代码已在实验箱验证,实验箱如下,其他开发板可以修改管脚适配:

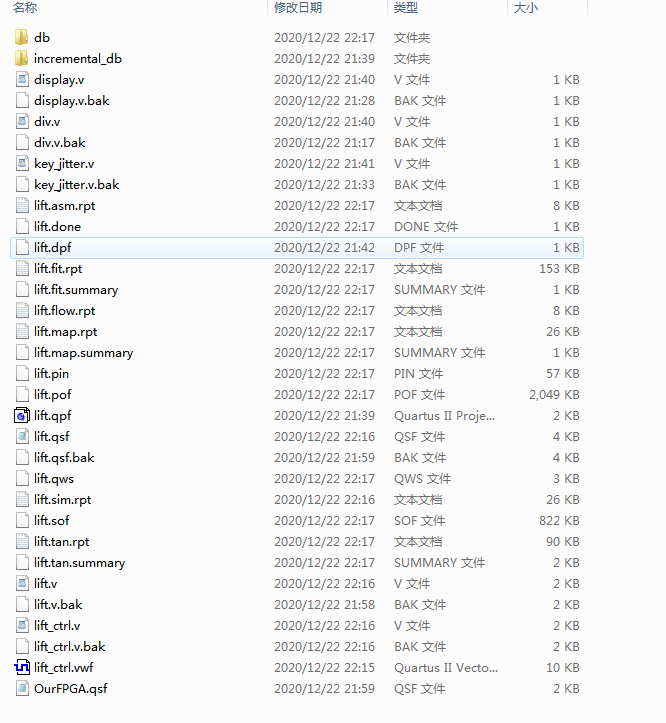

1. 工程文件

2. 程序文件

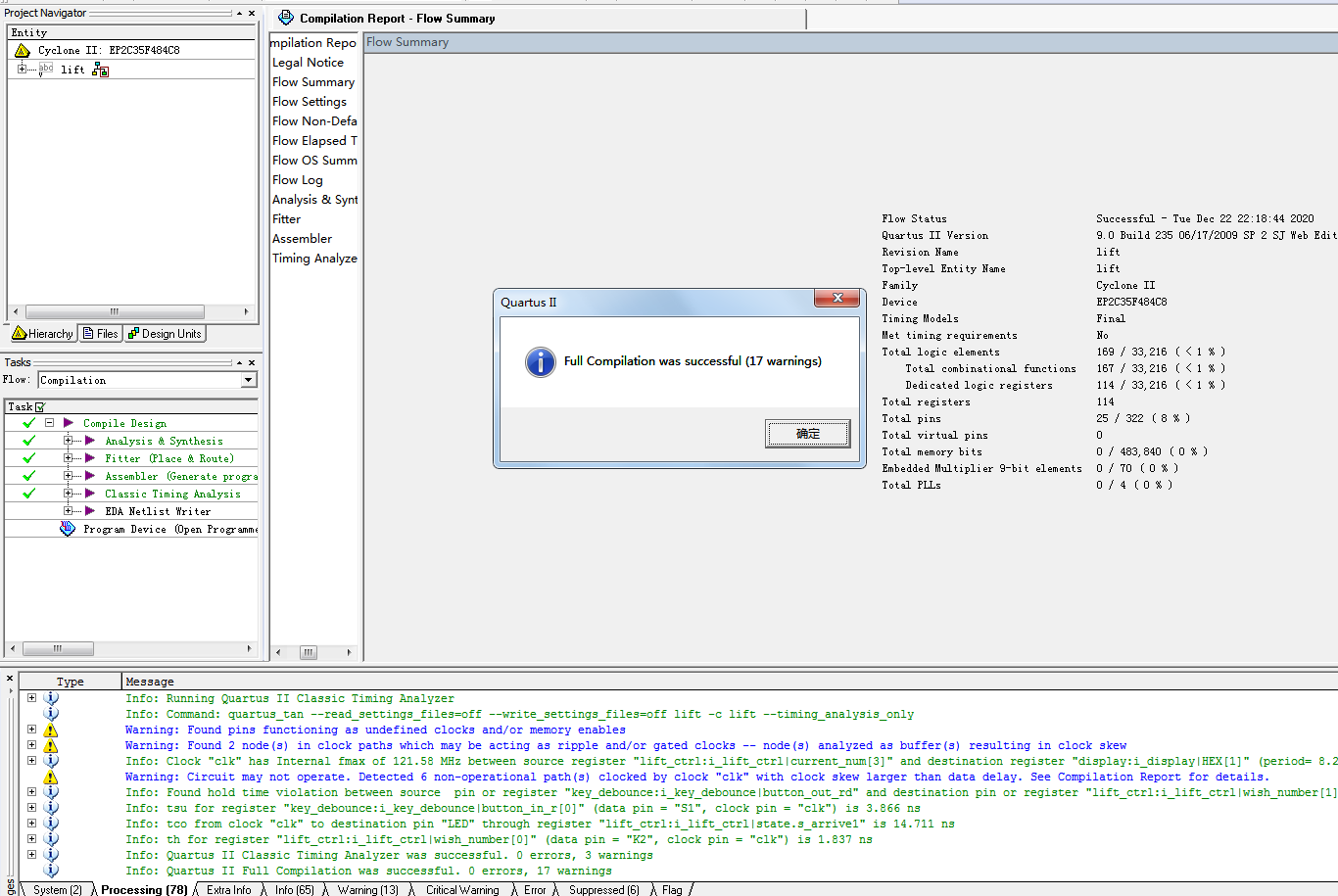

3. 程序编译

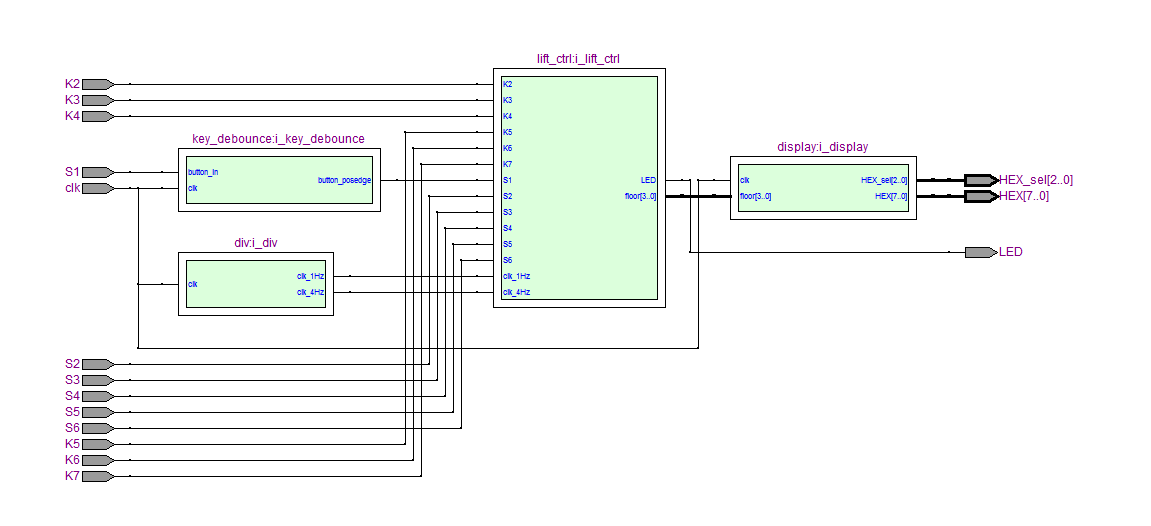

4. RTL图

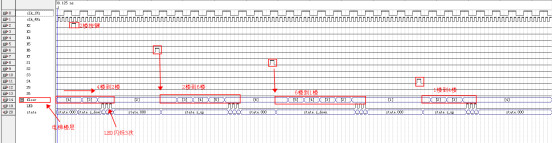

5. 仿真文件

6. 仿真图

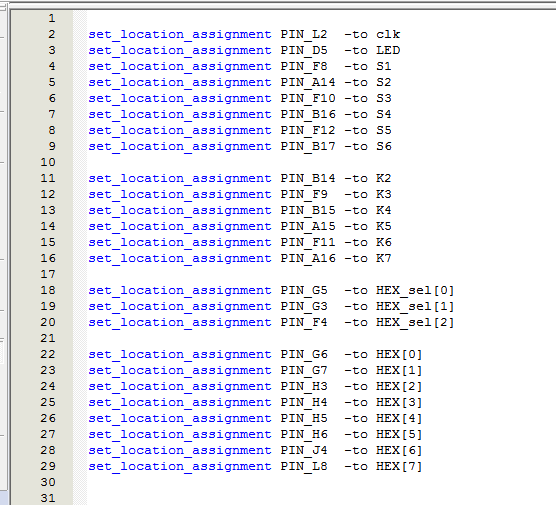

管脚分配

部分代码展示:

//电梯 module lift( input clk,//1MHz input S1,S2,S3,S4,S5,S6,//上行请求按键 input K2,K3,K4,K5,K6,K7,//下行请求按键 output LED,//green led output [2:0] HEX_sel,//数码管位选 output [7:0] HEX//共阴极数码管,高电平亮 ); wire clk_1Hz;//1Hz时钟 wire clk_4Hz;//4Hz时钟 wire [3:0] floor;//电梯楼层 wire S1_debounce;//消抖后S1 //按键消抖 key_debounce i_key_debounce( . clk(clk), . button_in(S1),//输入 . button_posedge(S1_debounce)//消抖后按键 ); //分频模块 div i_div( . clk(clk),//1MHz . clk_1Hz(clk_1Hz),//1Hz时钟 . clk_4Hz(clk_4Hz)//4Hz时钟 ); //电梯控制模块 lift_ctrl i_lift_ctrl( //. clk(clk),//1MHz . clk_1Hz(clk_1Hz),//1Hz时钟 . clk_4Hz(clk_4Hz),//4Hz时钟 . S1(S1_debounce),//消抖后S1 . S2(S2), . S3(S3), . S4(S4), . S5(S5), . S6(S6),//上行请求按键 . K2(K2), . K3(K3), . K4(K4), . K5(K5), . K6(K6), . K7(K7),//下行请求按键 . LED(LED), . floor(floor)//电梯楼层 );

源代码

扫描文章末尾的公众号二维码

1869

1869

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?