名称:三人智力竞赛抢答器Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

三人智力竞赛抢答器

当某一参赛者首先按下抢答开关时,相应显示灯亮。此时抢答器不再接受其他输入信号。电路具有回答时间控制功能,要求回答问题时间小于10s,时间采用倒计时方式。当达到限定时间时发出声响警告。

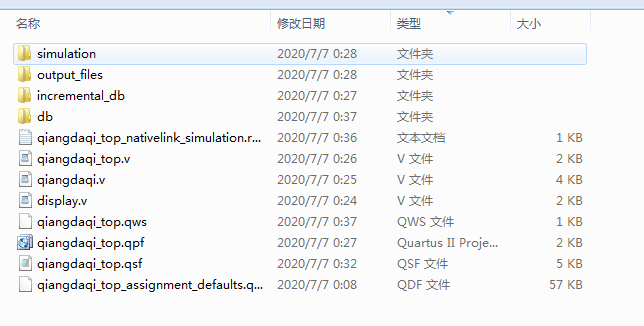

1. 工程文件

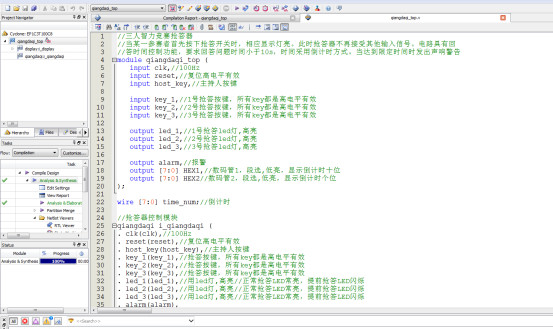

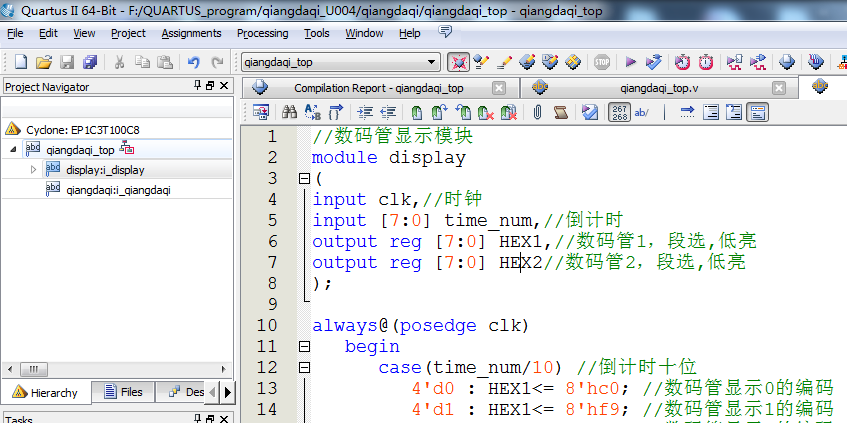

2. 程序文件

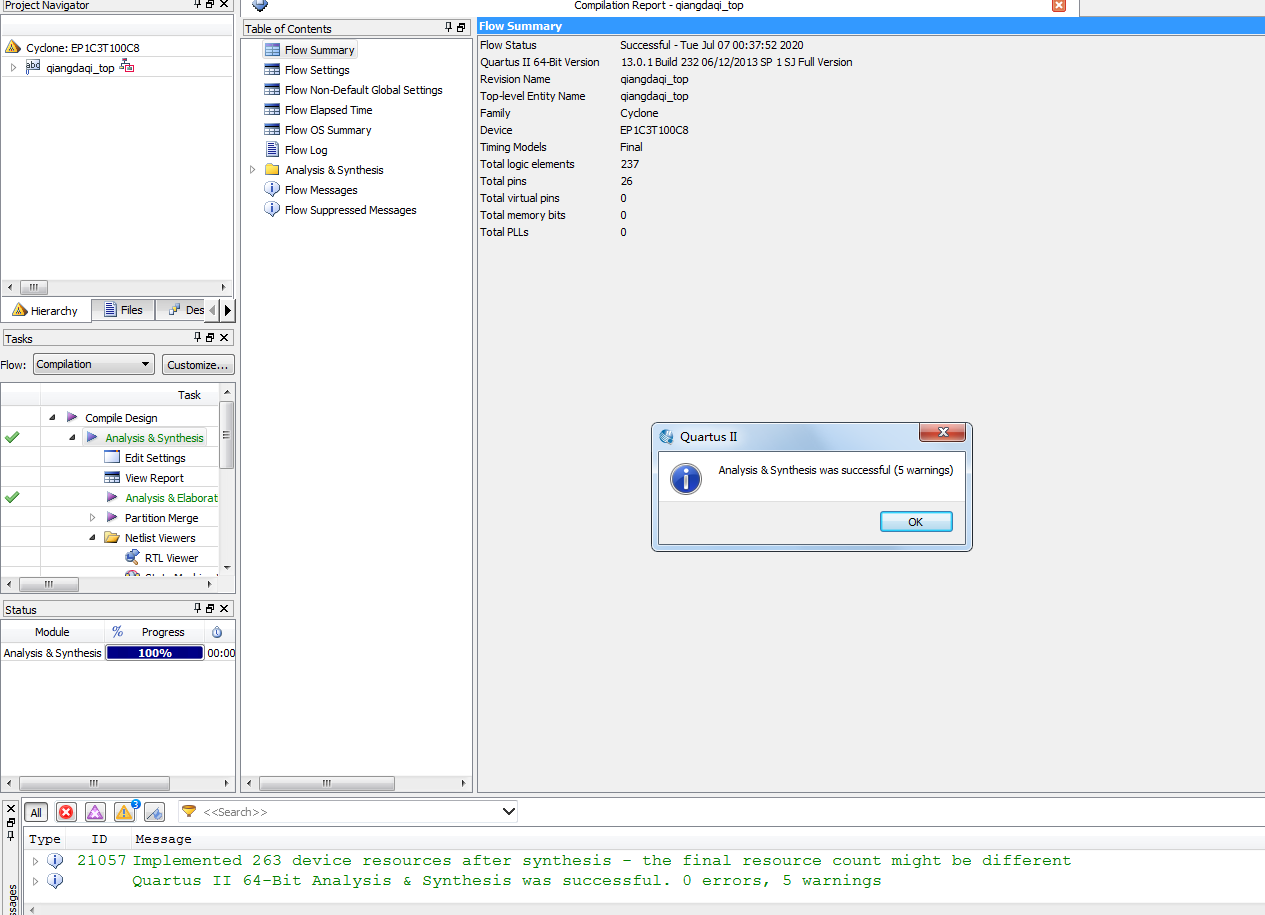

3. 程序编译

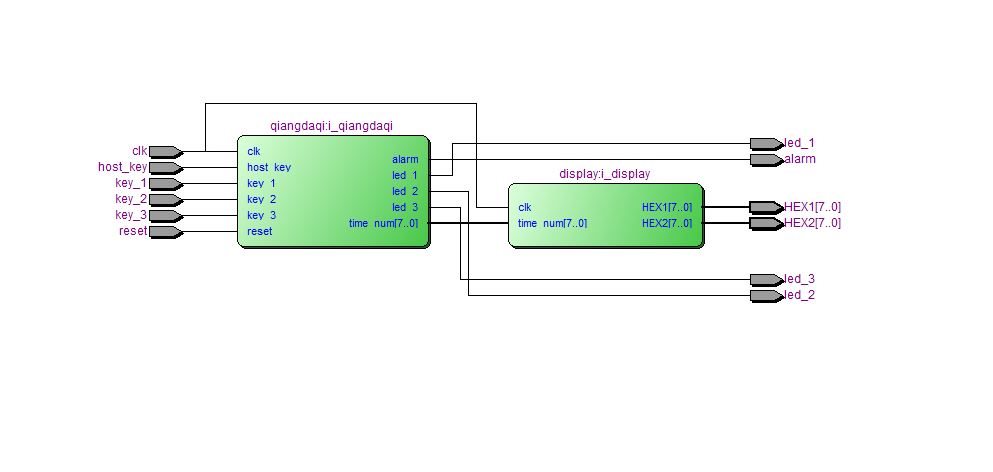

4. RTL图

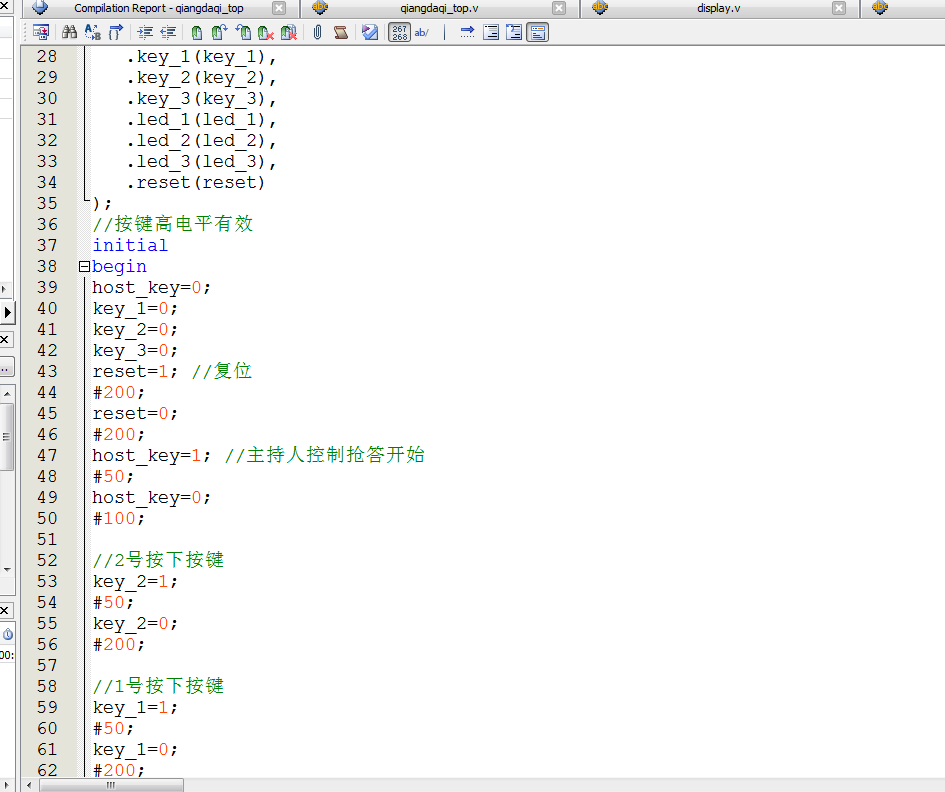

5. Testbench

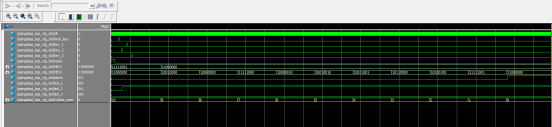

6. 仿真图

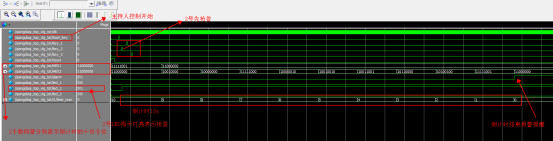

整体仿真图

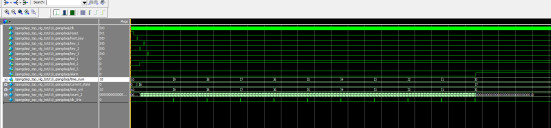

抢答器控制模块

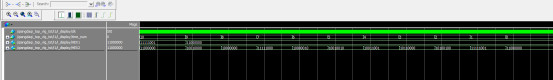

显示模块

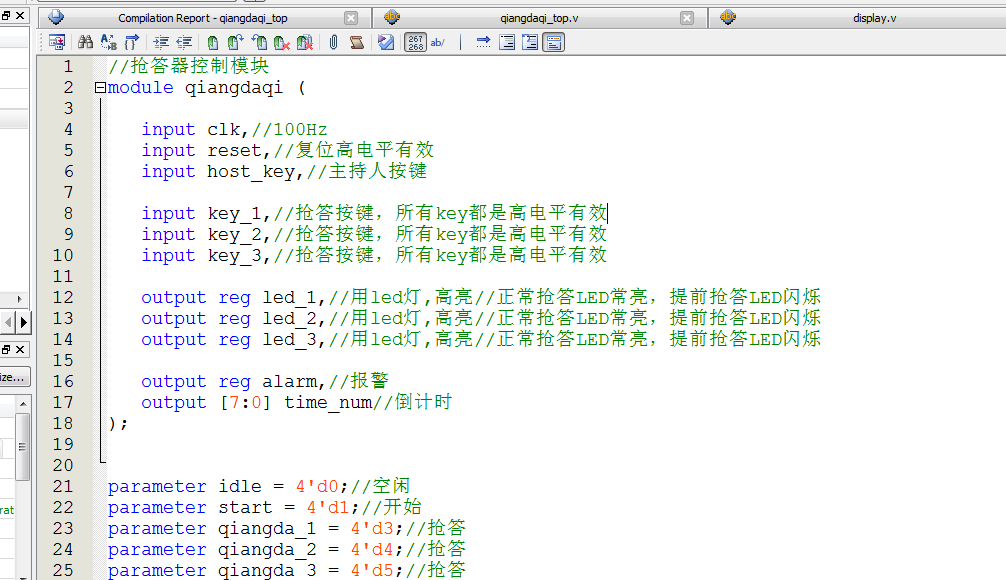

部分代码展示:

//抢答器控制模块 module qiangdaqi ( input clk,//100Hz input reset,//复位高电平有效 input host_key,//主持人按键 input key_1,//抢答按键,所有key都是高电平有效 input key_2,//抢答按键,所有key都是高电平有效 input key_3,//抢答按键,所有key都是高电平有效 output reg led_1,//用led灯,高亮//正常抢答LED常亮,提前抢答LED闪烁 output reg led_2,//用led灯,高亮//正常抢答LED常亮,提前抢答LED闪烁 output reg led_3,//用led灯,高亮//正常抢答LED常亮,提前抢答LED闪烁 output reg alarm,//报警 output [7:0] time_num//倒计时 ); parameter idle = 4'd0;//空闲 parameter start = 4'd1;//开始 parameter qiangda_1 = 4'd3;//抢答 parameter qiangda_2 = 4'd4;//抢答 parameter qiangda_3 = 4'd5;//抢答 parameter down_cnt = 4'd6;//倒计时状态 parameter s_alarm = 4'd7;//报警状态 reg [3:0]current_state=4'd0;//定义状态 //状态机 reg [7:0] time_cnt=8'd10;//预置答题时间为10s always@(posedge clk or posedge reset) begin if(reset==1'd1)//复位 current_state <= idle; else case(current_state) idle: //未开始抢答状态 begin if(host_key==1'd1)//主持人按键 current_state <= start;//开始抢答 else current_state <= idle; end start: //开始抢答状态 begin if(key_1==1) current_state <= qiangda_1;//1号抢答 else if(key_2==1) current_state <= qiangda_2;//2号抢答 else if(key_3==1) current_state <= qiangda_3;//3号抢答 else current_state <= start; end qiangda_1: current_state <= down_cnt;//1号答题 qiangda_2: current_state <= down_cnt;//2号答题 qiangda_3: current_state <= down_cnt;//3号答题 down_cnt://倒计时 if(time_cnt==0)//倒计时结束 current_state <=s_alarm; else current_state <= down_cnt; s_alarm: current_state <=s_alarm;//报警状态 default: current_state <=idle; endcase end always@(posedge clk or posedge reset) if(reset==1'd1) alarm<=0; else if(current_state==s_alarm)//报警状态 alarm<=1; reg [31:0] count_2=32'd0; reg clk_1Hz=0;//1Hz信号 always@(posedge clk or posedge reset) begin if(reset==1'd1)begin count_2<=32'd0; clk_1Hz<=0; end else if(current_state==down_cnt)//倒计时状态 if(count_2==32'd99)begin//计数0~99 count_2<=32'd0; clk_1Hz<=1;//1Hz信号,用于控制倒计时 end else begin count_2<=count_2+32'd1; clk_1Hz<=0; end end always@(posedge clk or posedge reset) begin if(reset==1) time_cnt<=8'd10;//预置答题时间10秒 else if(clk_1Hz==1)//1Hz计时使能 time_cnt<=time_cnt-1;//倒计时 else time_cnt<=time_cnt; end assign time_num=time_cnt;//输出倒计时 //抢答LED常亮 //控制led灯

源代码

扫描文章末尾的公众号二维码

本文详细介绍了使用Verilog语言在Quartus平台上设计的三人智力竞赛抢答器,包括控制逻辑、倒计时功能和LED显示。抢答器允许主持人启动,当有人按下抢答键后锁定并开始倒计时,10秒后发出警告。

本文详细介绍了使用Verilog语言在Quartus平台上设计的三人智力竞赛抢答器,包括控制逻辑、倒计时功能和LED显示。抢答器允许主持人启动,当有人按下抢答键后锁定并开始倒计时,10秒后发出警告。

3140

3140

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?