名称:可编程方波信号发生器Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

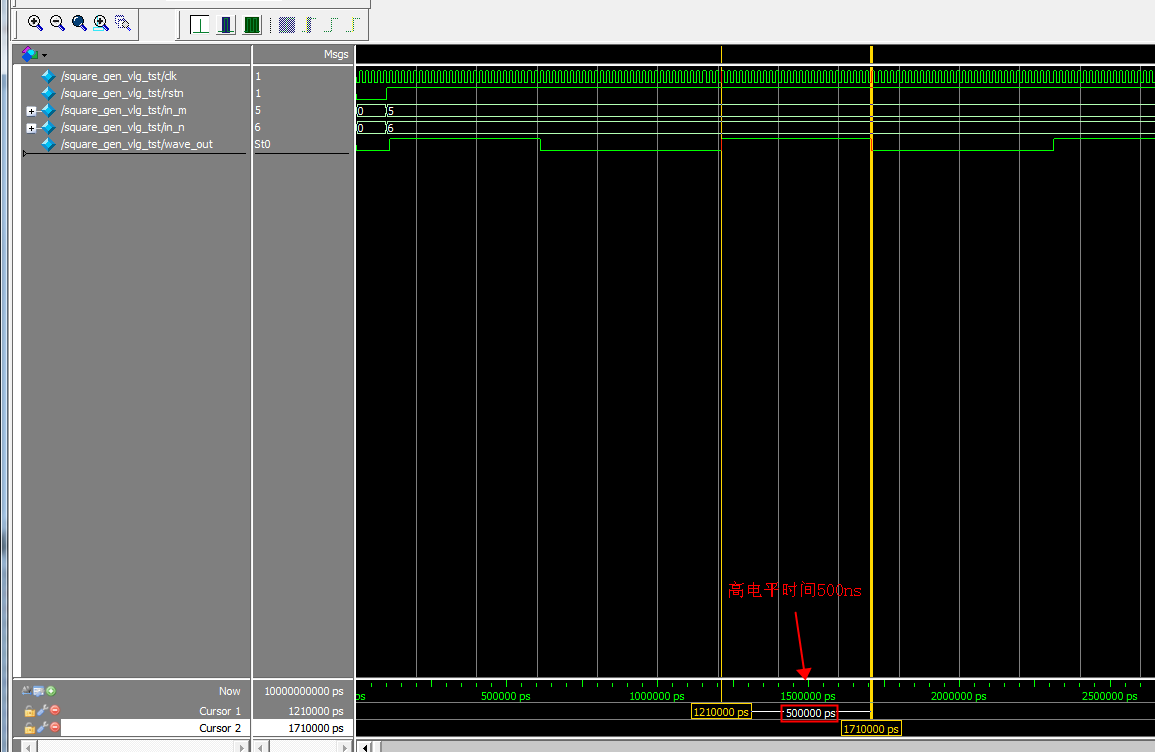

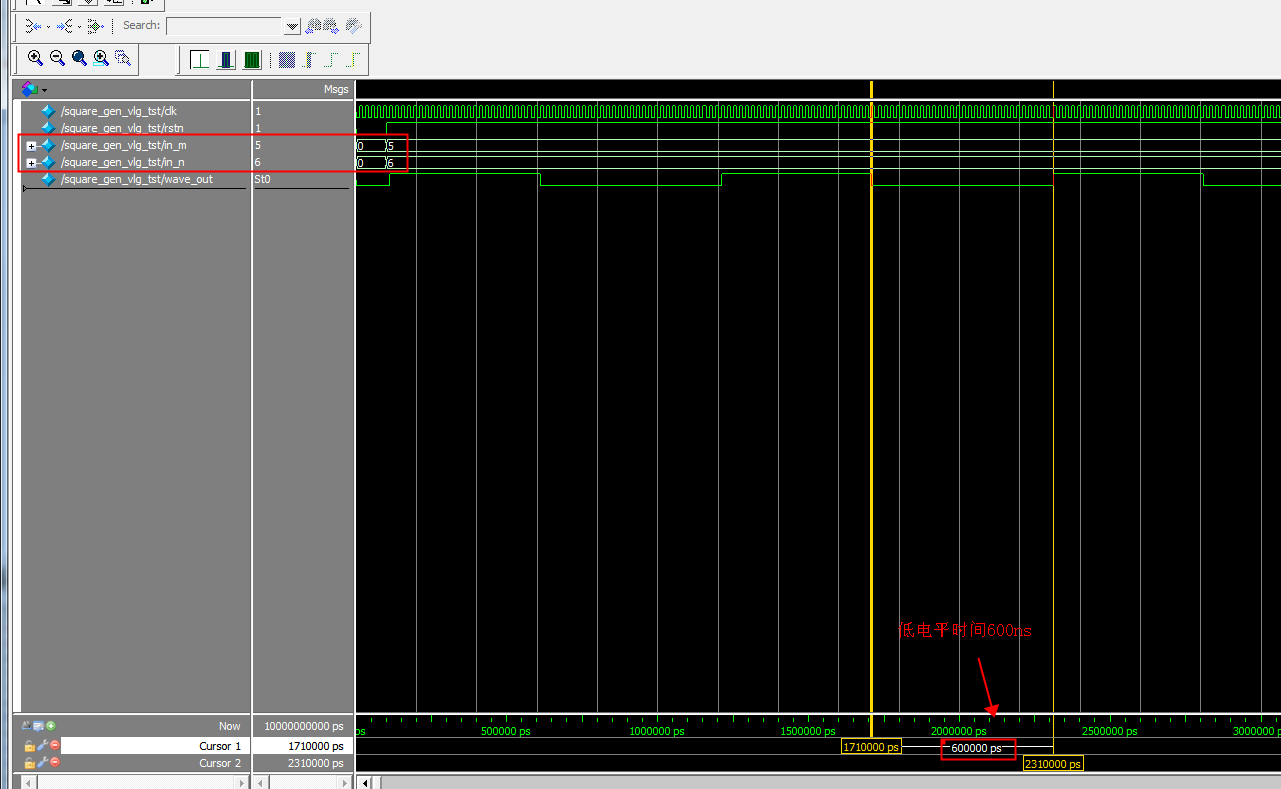

1、方波信号发生器,可以控制高电平和低电平时间

2、通过输入信号M控制高电平时间

3、通过输入信号N控制低电平时间

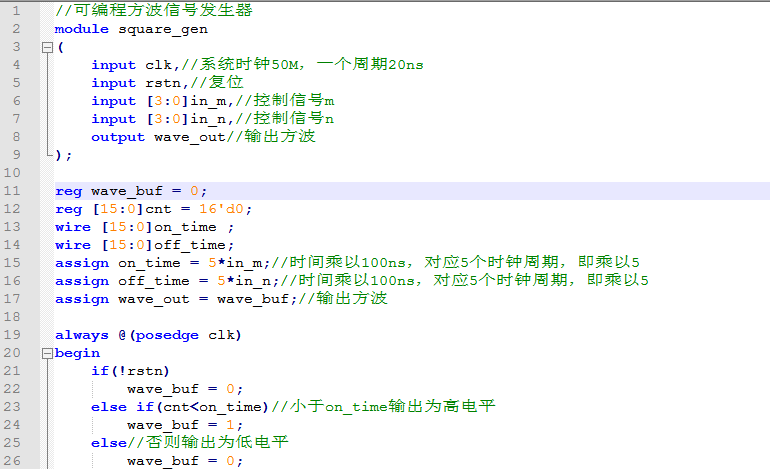

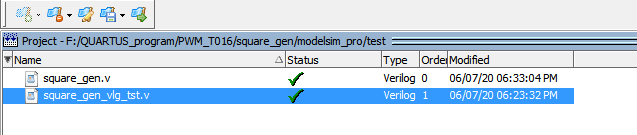

1. 程序文件

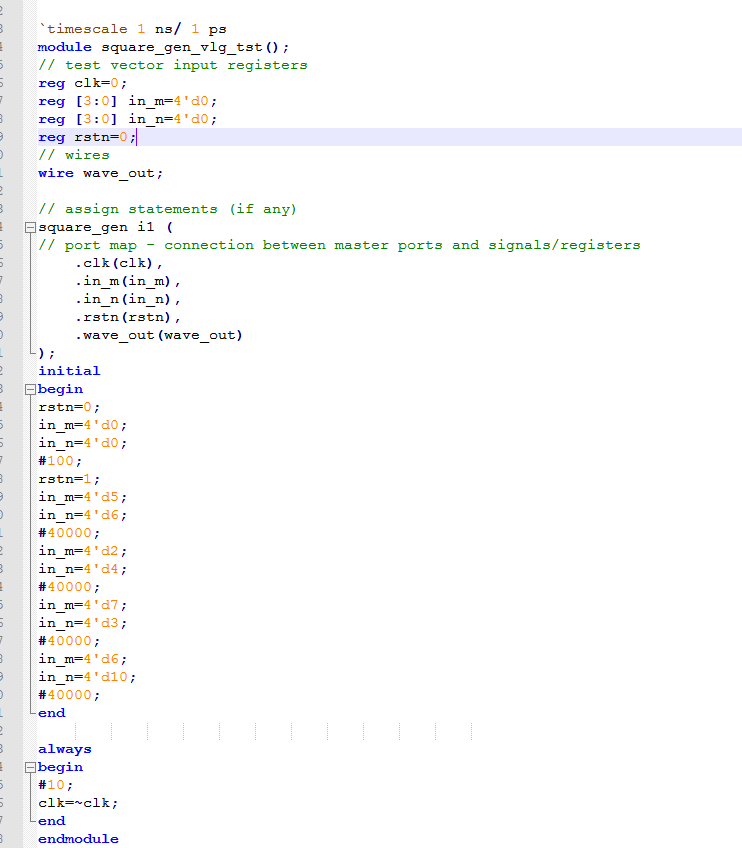

2. Testbench文件

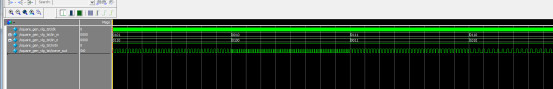

3. 仿真图

M控制高电平时间,n控制低电平时间

部分代码展示:

//可编程方波信号发生器 module square_gen ( input clk,//系统时钟50M,一个周期20ns input rstn,//复位 input [3:0]in_m,//控制信号m input [3:0]in_n,//控制信号n output wave_out//输出方波 ); reg wave_buf = 0; reg [15:0]cnt = 16'd0; wire [15:0]on_time ; wire [15:0]off_time; assign on_time = 5*in_m;//时间乘以100ns,对应5个时钟周期,即乘以5 assign off_time = 5*in_n;//时间乘以100ns,对应5个时钟周期,即乘以5 assign wave_out = wave_buf;//输出方波 always @(posedge clk) begin if(!rstn) wave_buf = 0; else if(cnt<on_time)//小于on_time输出为高电平 wave_buf = 1; else//否则输出为低电平 wave_buf = 0; end always @(posedge clk) begin if(!rstn) cnt <= 16'd0; else if (cnt >= (on_time+off_time-1))//打开和关闭时间加起来就是一周期 cnt <= 16'd0; else cnt <= cnt + 16'd1;//计数 end endmodule

源代码

扫描文章末尾的公众号二维码

547

547

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?