名称:伪随机序列(m序列)发生器Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

伪随机序列(m序列)发生器

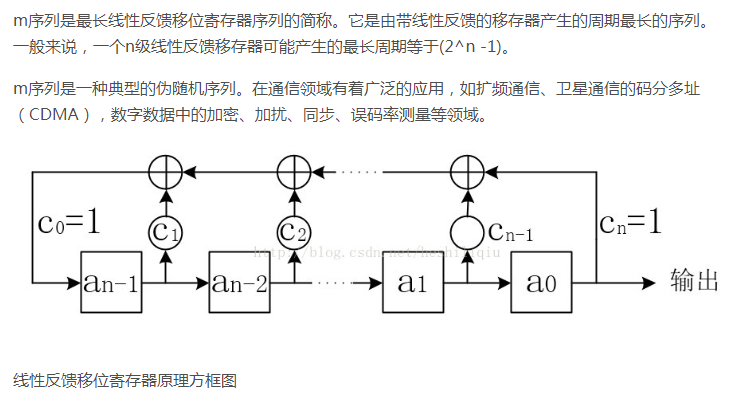

线性反馈移位寄存器设计(m序列)

1. 设计原理

2. 工程文件

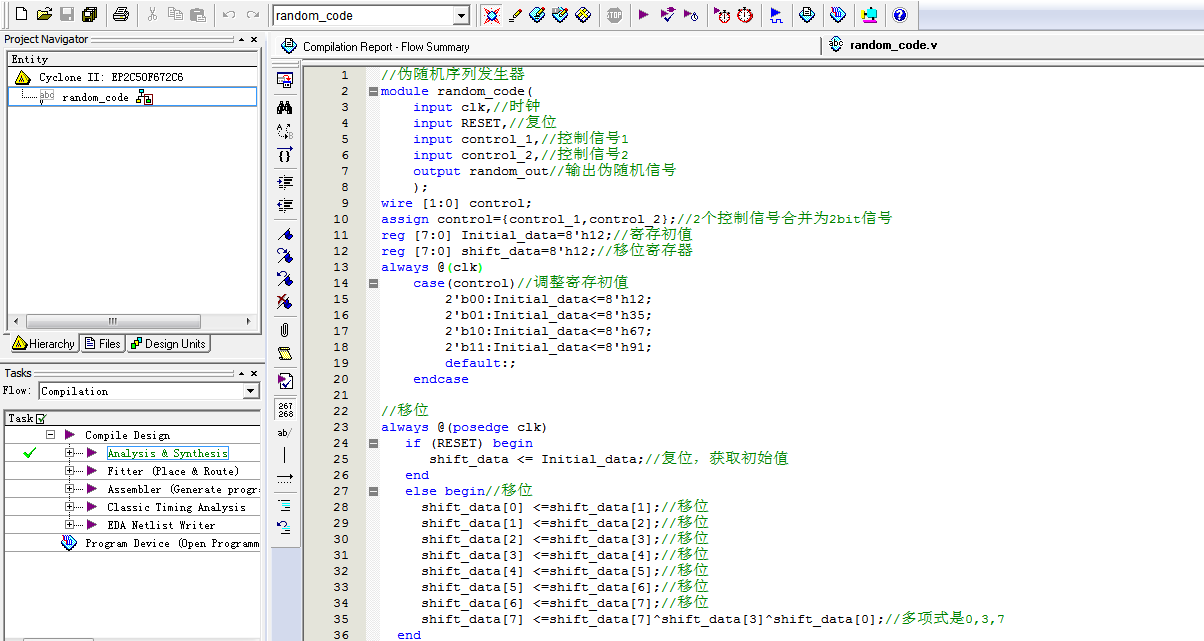

3. 程序文件

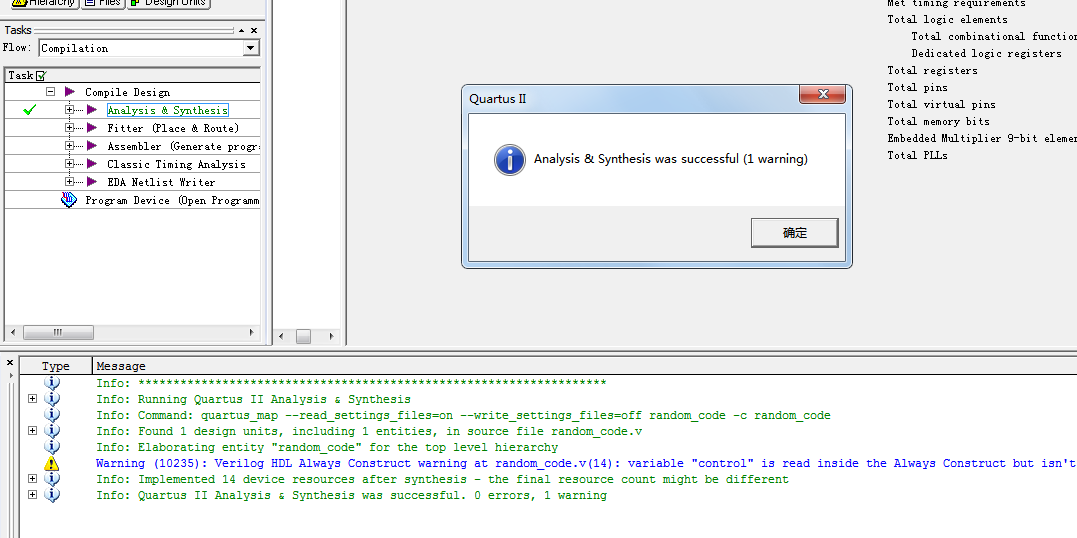

4. 程序编译

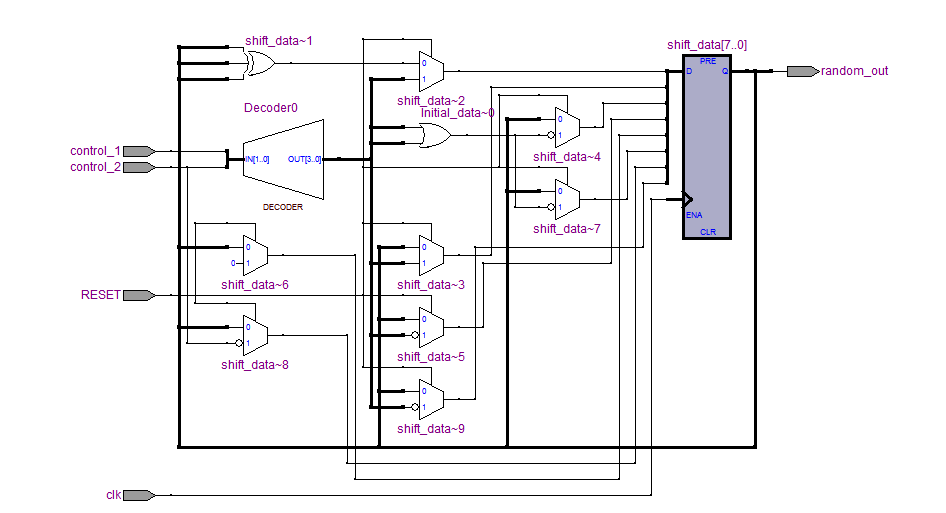

5. RTL图

6. 仿真文件

7. 仿真图

部分代码展示:

//伪随机序列发生器

module random_code(

input clk,//时钟

input RESET,//复位

input control_1,//控制信号1

input control_2,//控制信号2

output random_out//输出伪随机信号

);

wire [1:0] control;

assign control={control_1,control_2};//2个控制信号合并为2bit信号

reg [7:0] Initial_data=8'h12;//寄存初值

reg [7:0] shift_data=8'h12;//移位寄存器

always @(clk)

case(control)//调整寄存初值

2'b00:Initial_data<=8'h12;

2'b01:Initial_data<=8'h35;

2'b10:Initial_data<=8'h67;

2'b11:Initial_data<=8'h91;

default:;

endcase

//移位

always @(posedge clk)

if (RESET) begin

shift_data <= Initial_data;//复位,获取初始值

end

else begin//移位

源代码

扫描文章末尾的公众号二维码

4974

4974

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?