名称:基于FPGA的adc0809采集数据设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

adc0809采集数据

通过CPLD,最后把数据存储到随机存储器中

输出仿真波形图

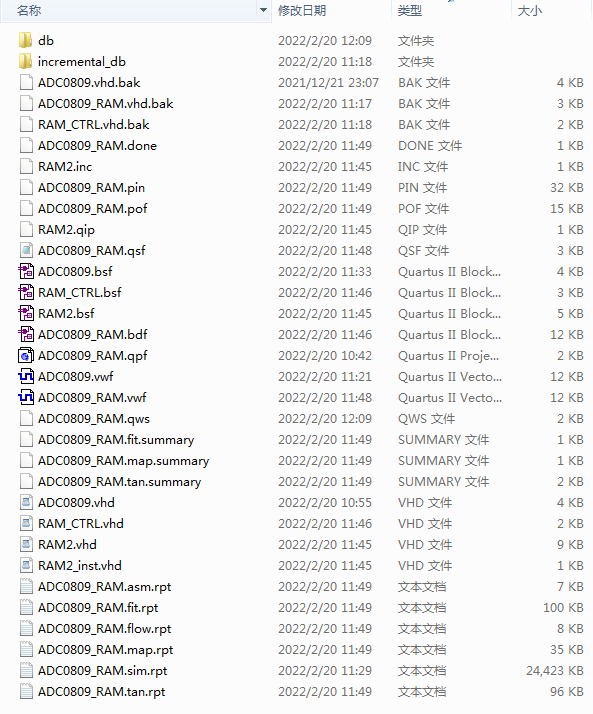

1. 工程文件

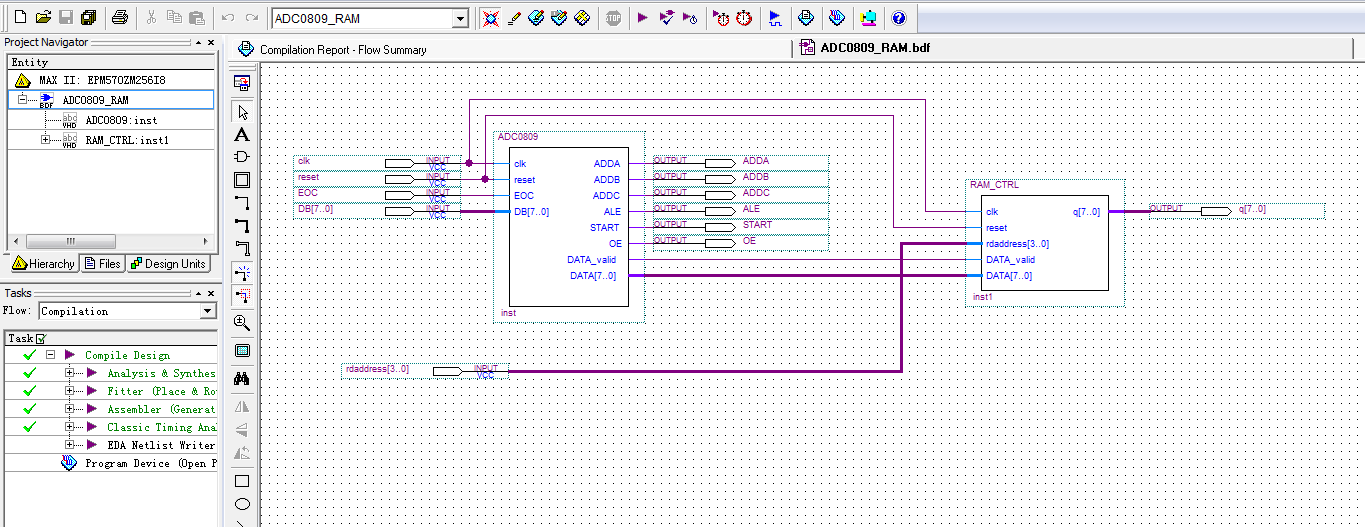

2. 顶层原理图

程序文件

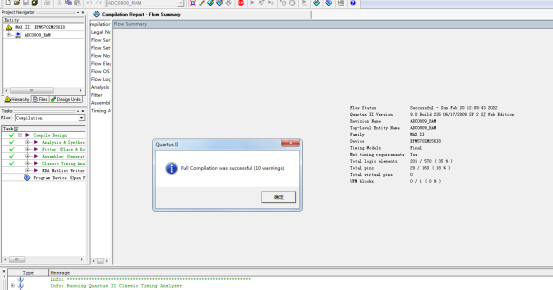

3. 程序编译

4. 仿真图

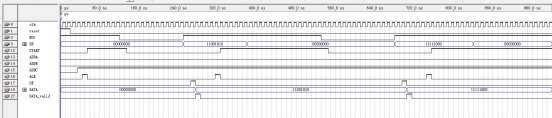

AD模块仿真

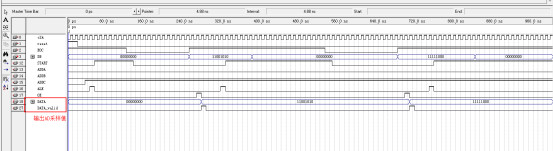

随机存储器模块仿真

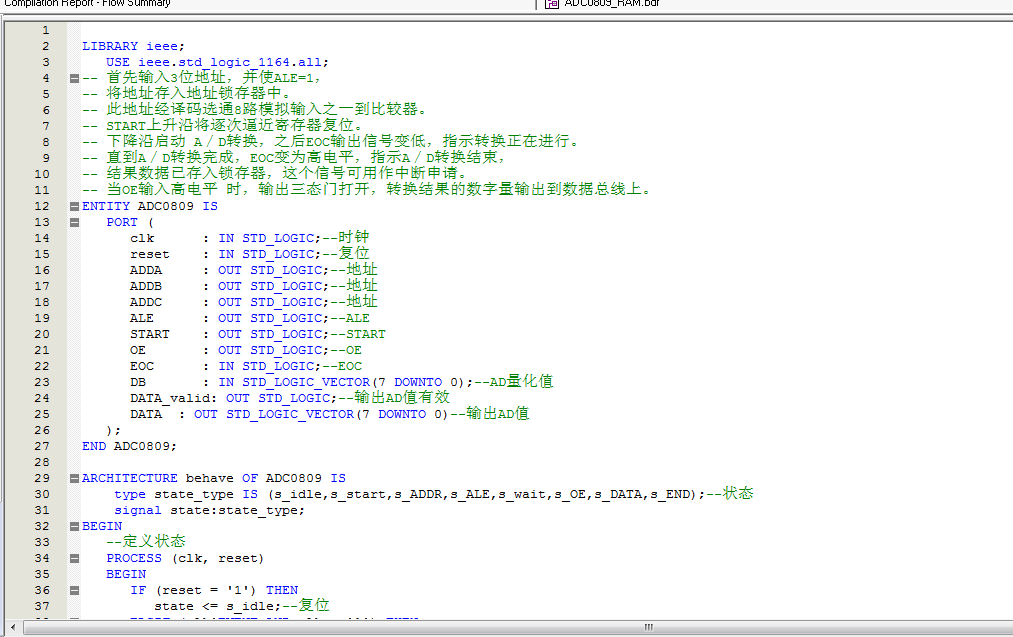

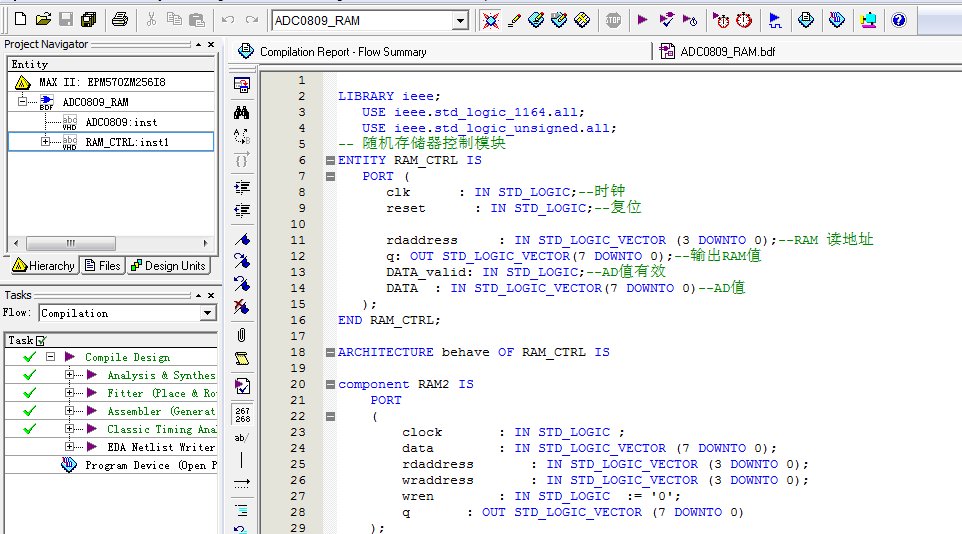

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; -- 首先输入3位地址,并使ALE=1, -- 将地址存入地址锁存器中。 -- 此地址经译码选通8路模拟输入之一到比较器。 -- START上升沿将逐次逼近寄存器复位。 -- 下降沿启动 A/D转换,之后EOC输出信号变低,指示转换正在进行。 -- 直到A/D转换完成,EOC变为高电平,指示A/D转换结束, -- 结果数据已存入锁存器,这个信号可用作中断申请。 -- 当OE输入高电平 时,输出三态门打开,转换结果的数字量输出到数据总线上。 ENTITY ADC0809 IS PORT ( clk : IN STD_LOGIC;--时钟 reset : IN STD_LOGIC;--复位 ADDA : OUT STD_LOGIC;--地址 ADDB : OUT STD_LOGIC;--地址 ADDC : OUT STD_LOGIC;--地址 ALE : OUT STD_LOGIC;--ALE START : OUT STD_LOGIC;--START OE : OUT STD_LOGIC;--OE EOC : IN STD_LOGIC;--EOC DB : IN STD_LOGIC_VECTOR(7 DOWNTO 0);--AD量化值 DATA_valid: OUT STD_LOGIC;--输出AD值有效 DATA : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--输出AD值 ); END ADC0809; ARCHITECTURE behave OF ADC0809 IS type state_type IS (s_idle,s_start,s_ADDR,s_ALE,s_wait,s_OE,s_DATA,s_END);--状态 signal state:state_type; BEGIN --定义状态 PROCESS (clk, reset) BEGIN IF (reset = '1') THEN state <= s_idle;--复位 ELSIF (clk'EVENT AND clk = '1') THEN CASE state IS WHEN s_idle => state <= s_ADDR;--输入地址 WHEN s_ADDR => state <= s_ALE;--锁存地址 WHEN s_ALE => state <= s_start;--开始转换 WHEN s_start => IF (EOC = '0') THEN state <= s_wait;--等待 ELSE state <= s_start; END IF; WHEN s_wait =>--等待转换完成 IF (EOC = '1') THEN--转换完成 state <= s_OE; END IF; WHEN s_OE =>--使能三态门 state <= s_DATA; WHEN s_DATA =>--读取AD值 state <= s_END; WHEN s_END =>--结束 state <= s_idle; WHEN OTHERS => END CASE; END IF; END PROCESS; --输入地址 PROCESS (clk, reset) BEGIN IF (reset = '1') THEN ADDA <= '0'; ADDB <= '0'; ADDC <= '0'; ELSIF (clk'EVENT AND clk = '1') THEN IF (state = s_ADDR) THEN--输入地址状态,选择通道1 ADDA <= '0'; ADDB <= '0'; ADDC <= '1'; END IF; END IF; END PROCESS; -- PROCESS (clk, reset) BEGIN IF (reset = '1') THEN ALE <= '0';--复位 ELSIF (clk'EVENT AND clk = '1') THEN IF (state = s_ALE) THEN--锁存地址 ALE <= '1';----锁存地址 ELSE ALE <= '0'; END IF; END IF; END PROCESS;

源代码

扫描文章末尾的公众号二维码

1148

1148

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?