名称:基于FPGA的83编码器及42优先编码器设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

83编码器及42优先编码器

1、设计8线-3线编码器

2、设计4-2优先编码器

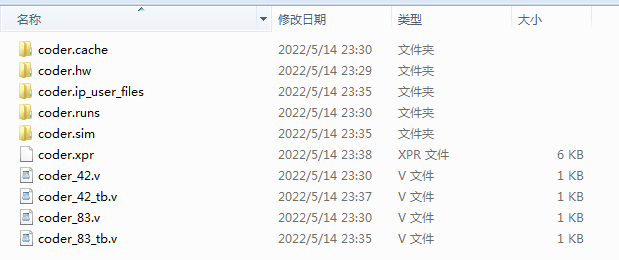

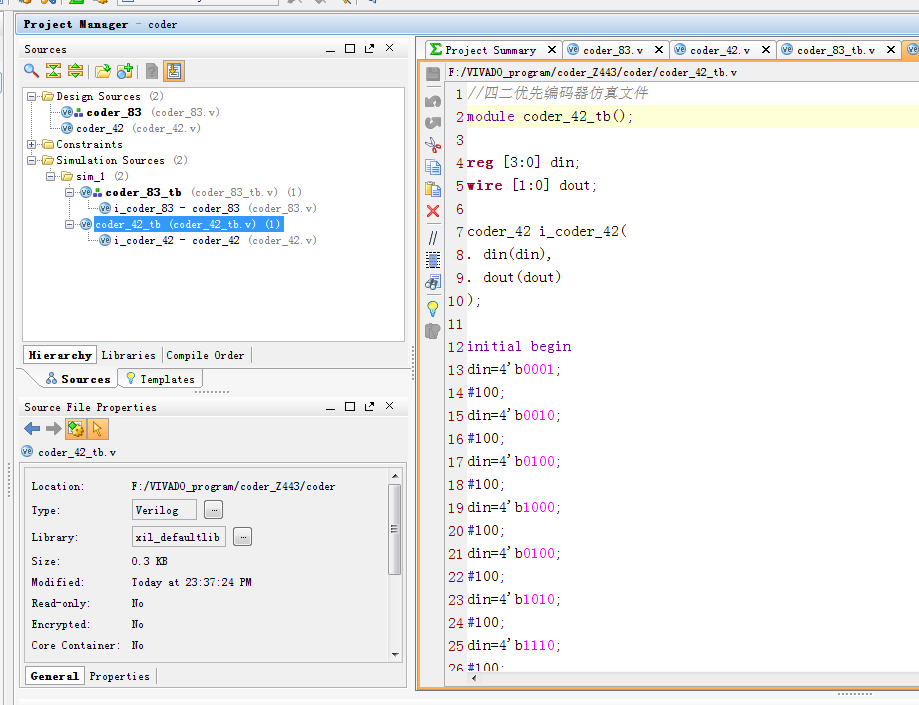

1. 工程文件

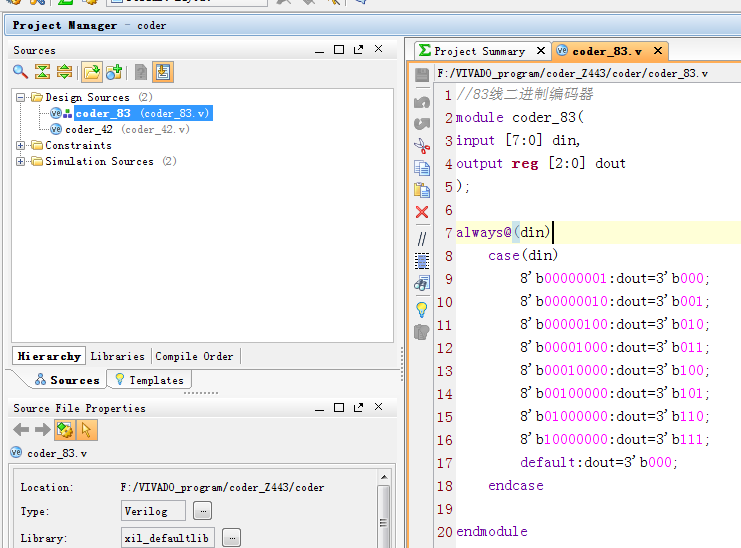

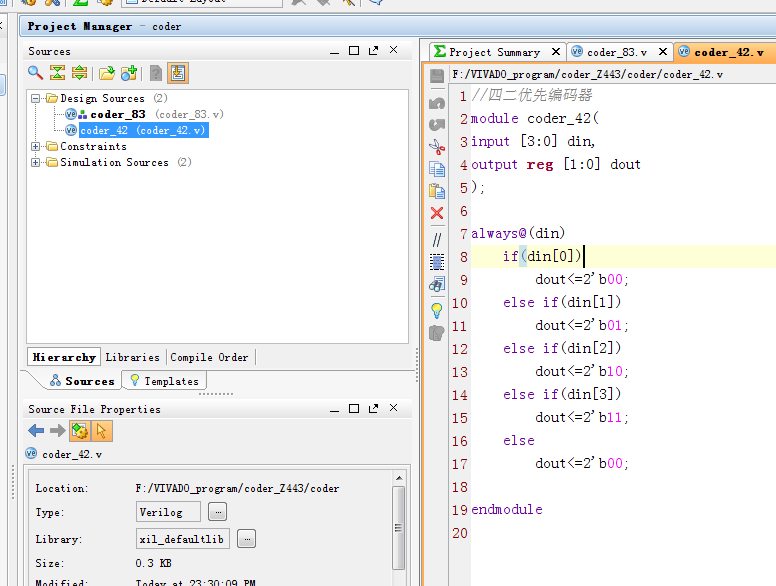

2. 程序文件

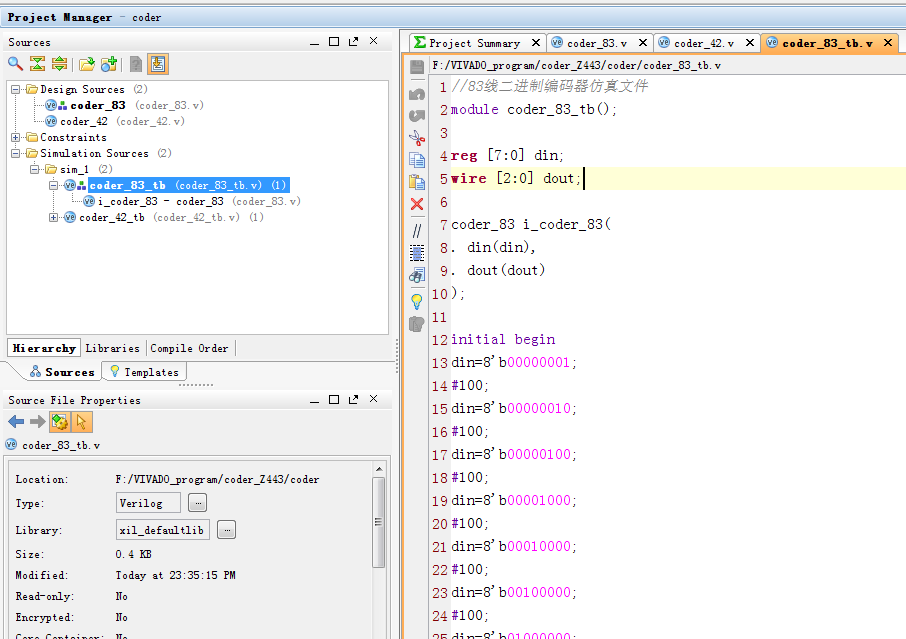

Testbench

3. 程序编译

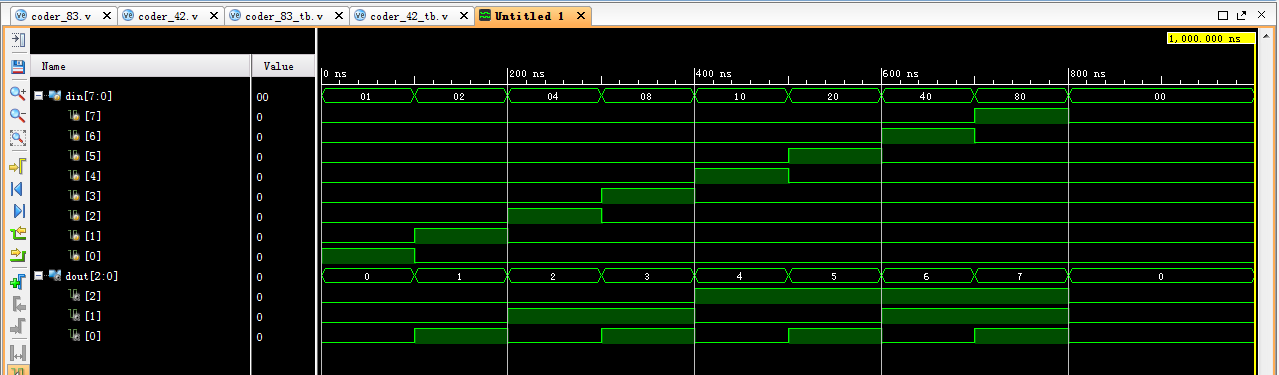

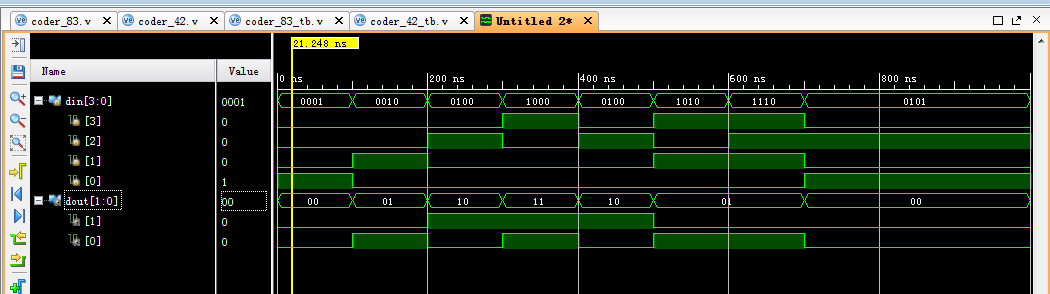

4. 仿真图

83线二进制编码器

四二优先编码器

部分代码展示:

//四二优先编码器

module coder_42( input [3:0] din, output reg [1:0] dout ); always@(din) if(din[0]) dout<=2'b00; else if(din[1]) dout<=2'b01; else if(din[2]) dout<=2'b10; else if(din[3]) dout<=2'b11; else dout<=2'b00; endmodule

源代码

扫描文章末尾的公众号二维码

3812

3812

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?