名称:FPGA到ARM的通信接口设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

设计一个通信接口,完成从FPGA到ARM的数据传输。

任务要求

一、 数据位宽16位,传输速率为100Mb/s;

二、采用主从式通信传输(建议ARM为主机FPGA为从机)

(1)从机向主机发送“有数据需要发送”的指令之后,从机开始传输数据

(2)数据发送完毕之后,从机向主机发送“无数据发送”的指令

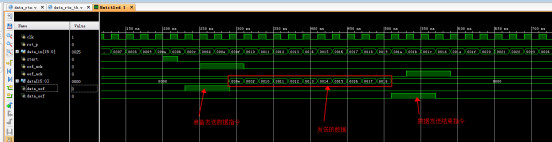

1. 协议设计

从机向主机发送data_sof信号作为有数据需要发送的指令

然后从机向主机发送16位的data信号

发送完成后,从机向主机发送data_eof信号作为无有数据需要发送的指令

主机收到data_sof信号后发送一个sof_ack作为应答信号

主机收到data_eof信号后发送一个eof_ack作为应答信号

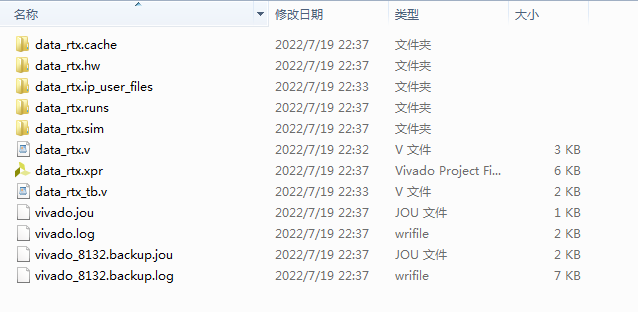

2. 工程文件

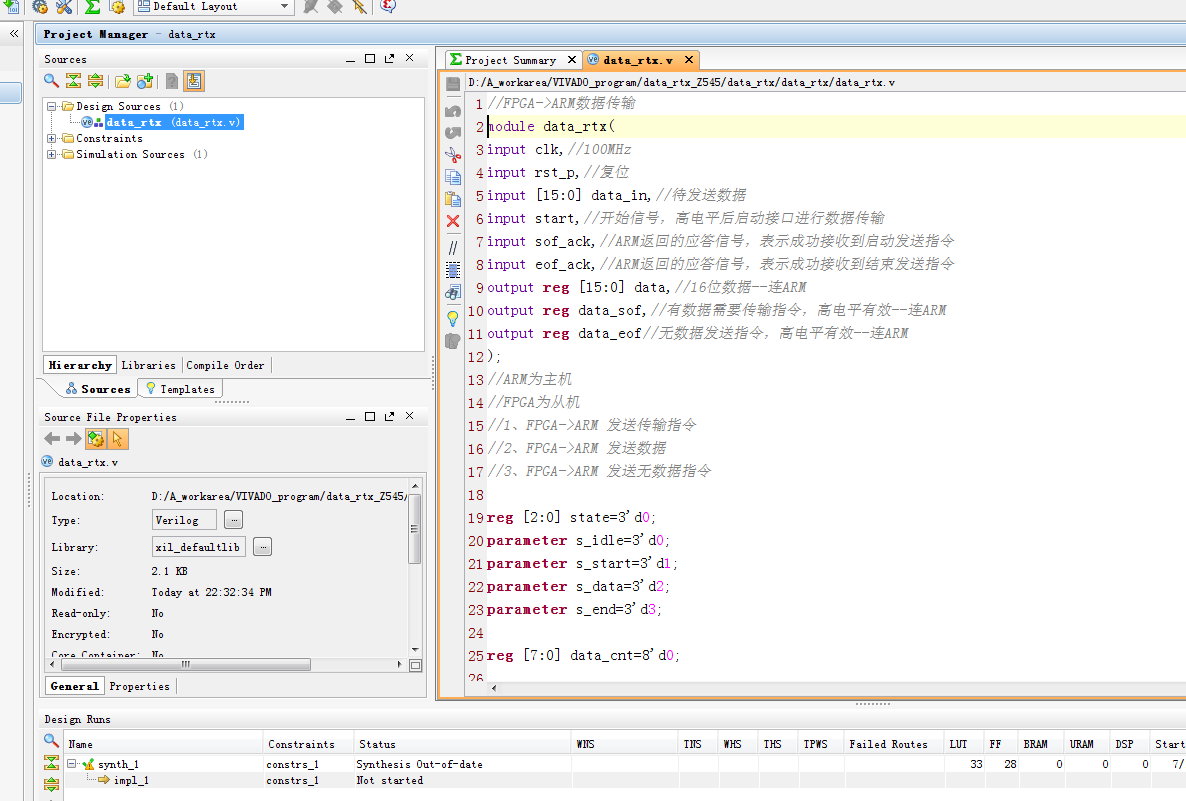

3. 程序文件

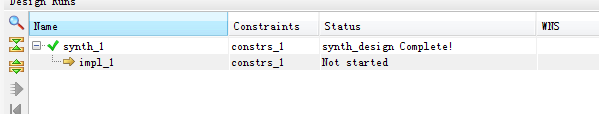

4. 程序编译

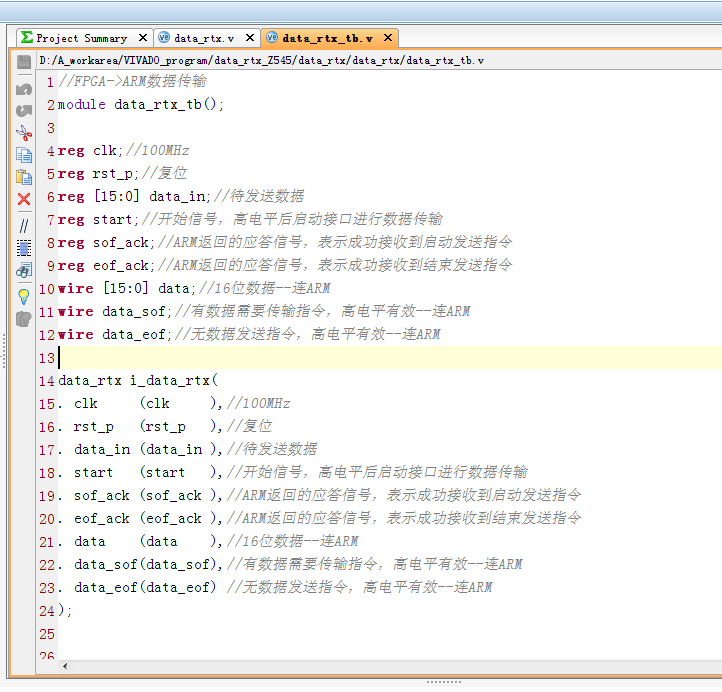

5. Testbench

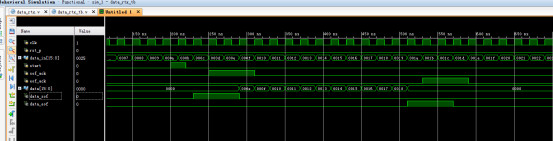

6. 仿真图

部分代码展示:

//FPGA->ARM数据传输 m (2) odule data_rtx( input clk,//100MHz input rst_p,//复位 input [15:0] data_in,//待发送数据 input start,//开始信号,高电平后启动接口进行数据传输 input sof_ack,//ARM返回的应答信号,表示成功接收到启动发送指令 input eof_ack,//ARM返回的应答信号,表示成功接收到结束发送指令 output reg [15:0] data,//16位数据--连ARM output reg data_sof,//有数据需要传输指令,高电平有效--连ARM output reg data_eof//无数据发送指令,高电平有效--连ARM ); //ARM为主机 //FPGA为从机 //1、FPGA->ARM 发送传输指令 //2、FPGA->ARM 发送数据 //3、FPGA->ARM 发送无数据指令 reg [2:0] state=3'd0; parameter s_idle=3'd0; parameter s_start=3'd1; parameter s_data=3'd2; parameter s_end=3'd3; reg [7:0] data_cnt=8'd0; always@(posedge clk or posedge rst_p) if(rst_p) state<=s_idle; else case(state) s_idle://空闲状态 if(start)//接收到开始信号,高电平后启动接口进行数据传输 state<=s_start; s_start://开始状态,传输启动发送指令(有数据需要传输指令) if(sof_ack)//ARM返回的应答信号,表示成功接收到启动发送指令 state<=s_data;//发送数据 s_data://发送数据状态 if(data_cnt>=8'd10)//设每次发送10个数据 state<=s_end;//结束 s_end://无数据发送状态 if(eof_ack)//ARM返回的应答信号,表示成功接收到结束发送指令 state<=s_idle; default:; endcase

源代码

扫描文章末尾的公众号二维码

4482

4482

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?