名称:AD7705驱动及UART发送设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

AD7705输入(4000喻上m入)/7(仿真输出=学号后3位),8位UART发送输出

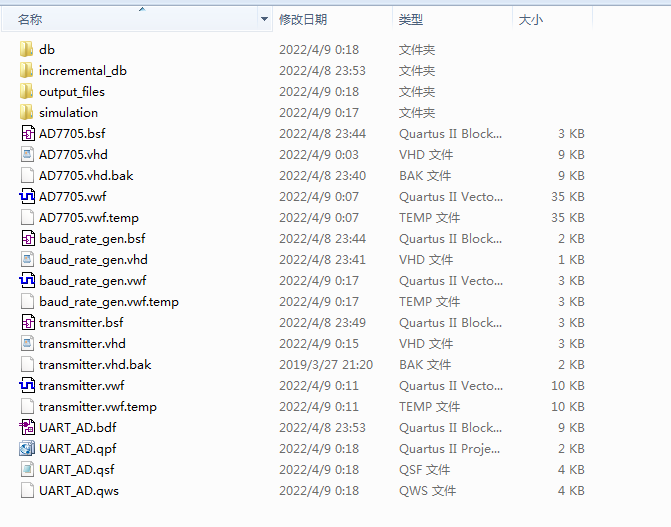

1. 工程文件

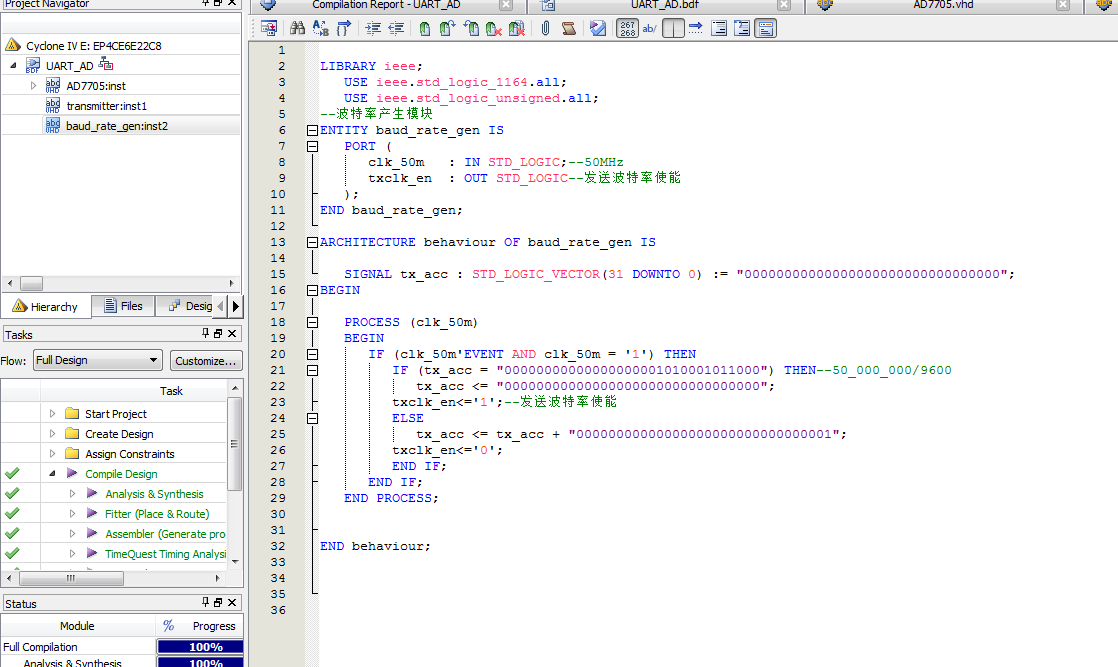

2. 程序文件

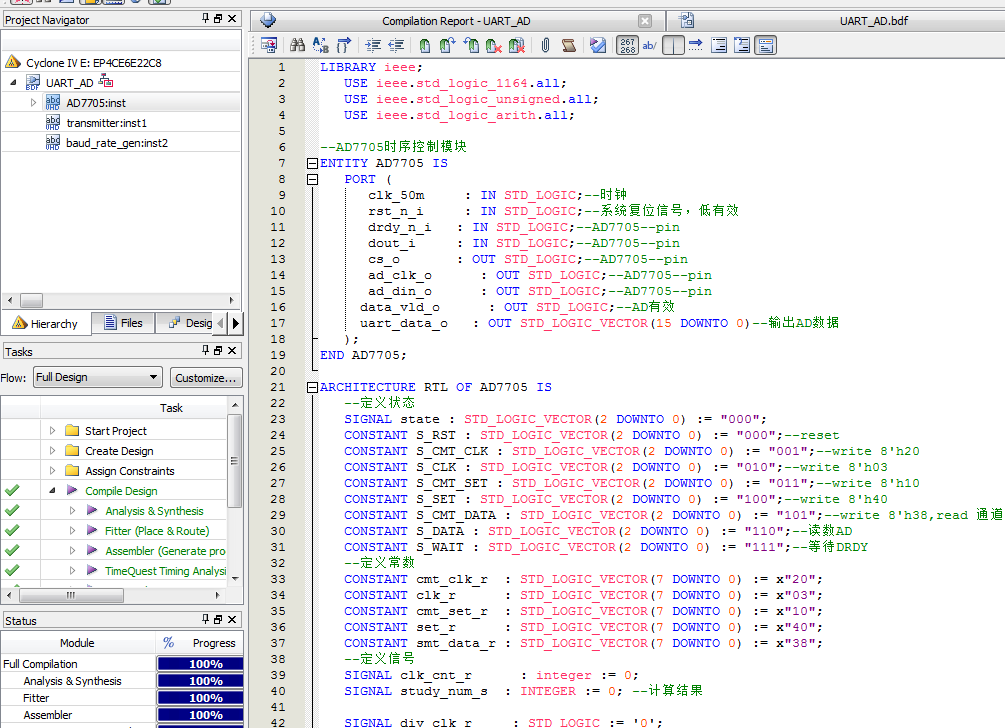

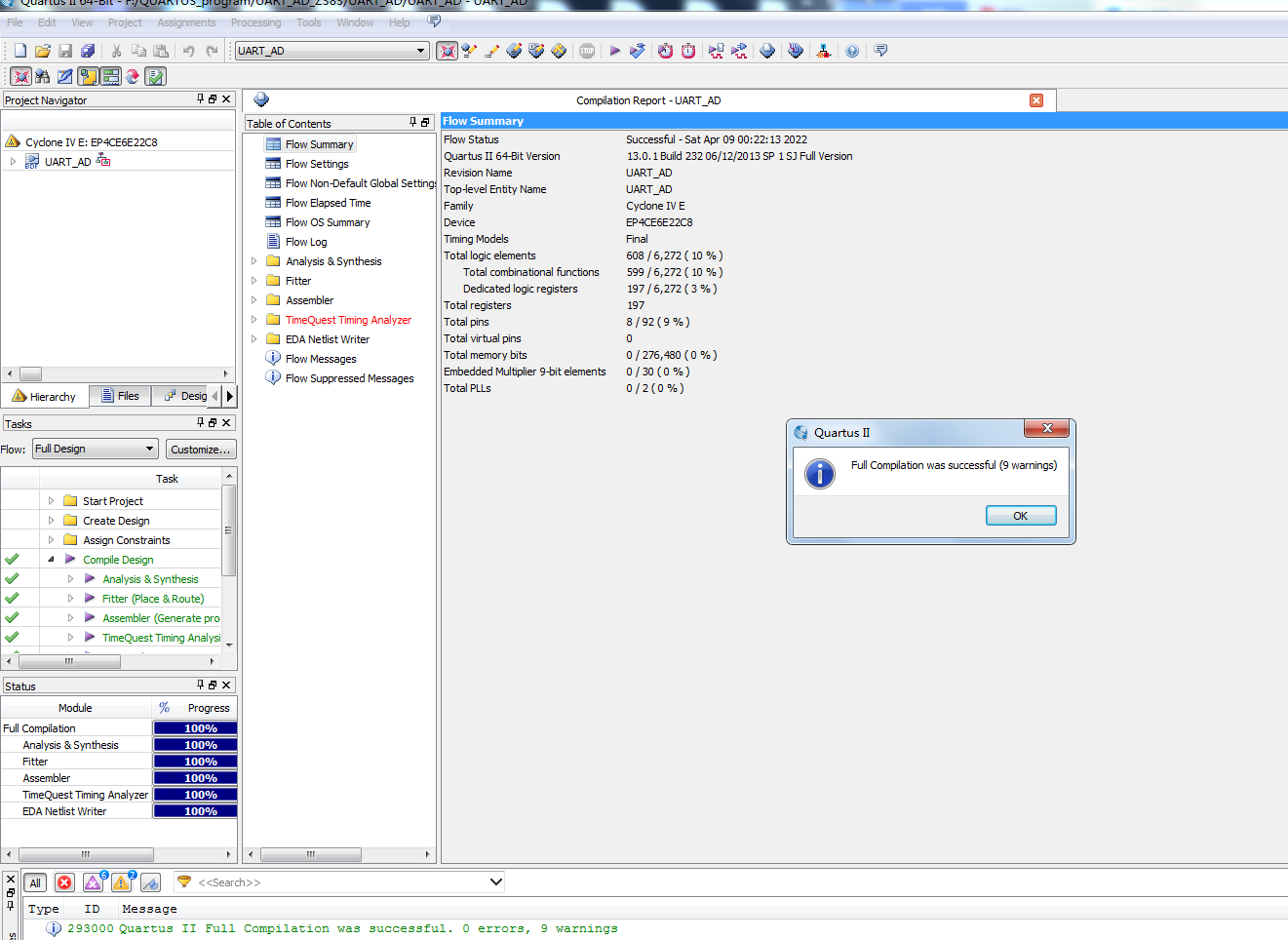

3. 程序编译

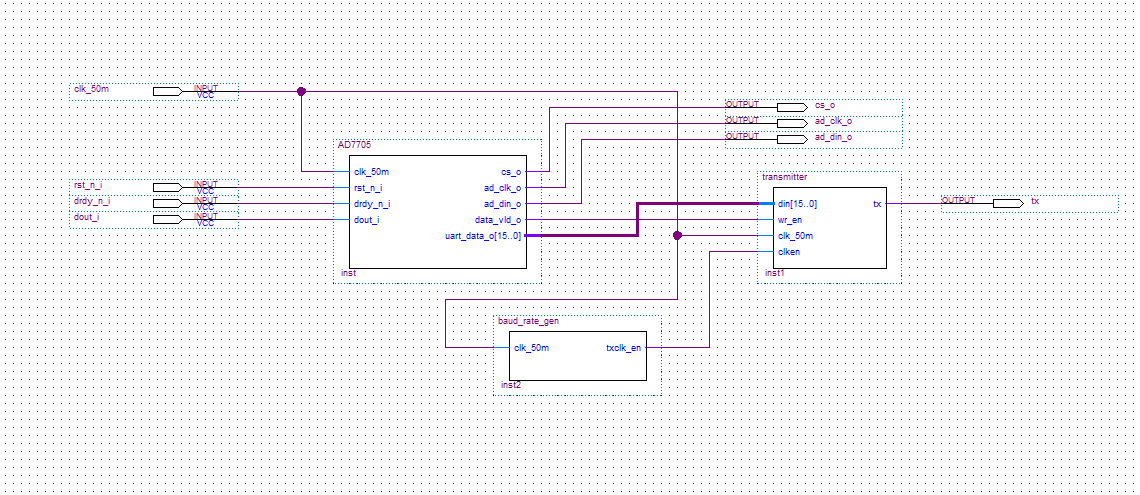

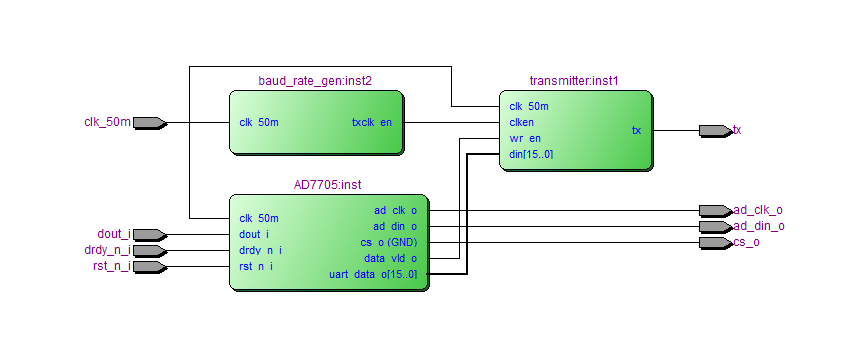

4. RTL图

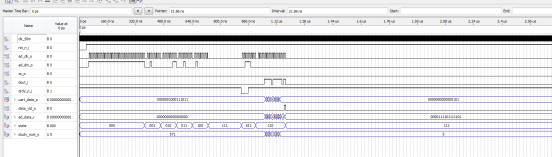

5. 仿真图

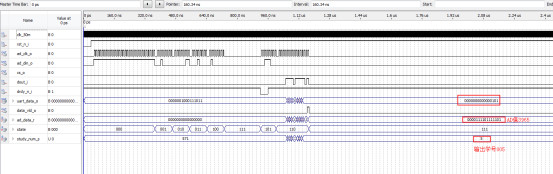

AD7705模块仿真

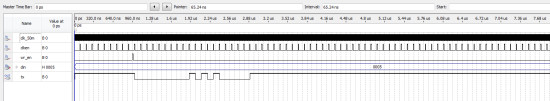

波特率产生模块

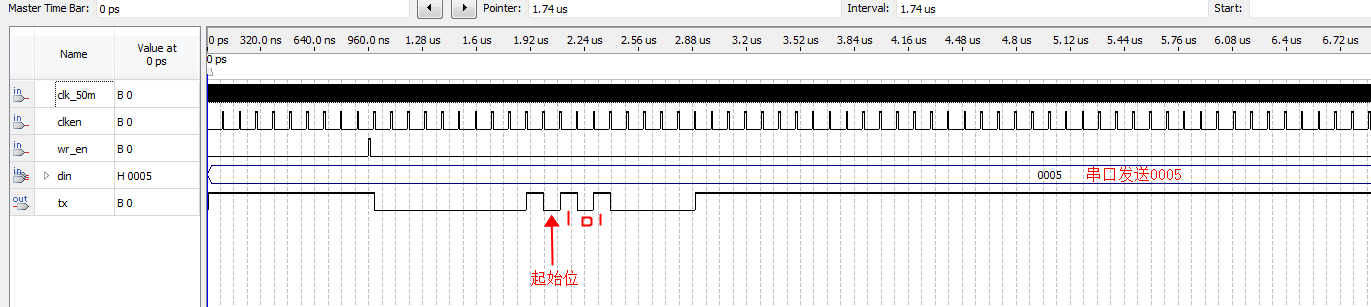

串口发送模块仿真

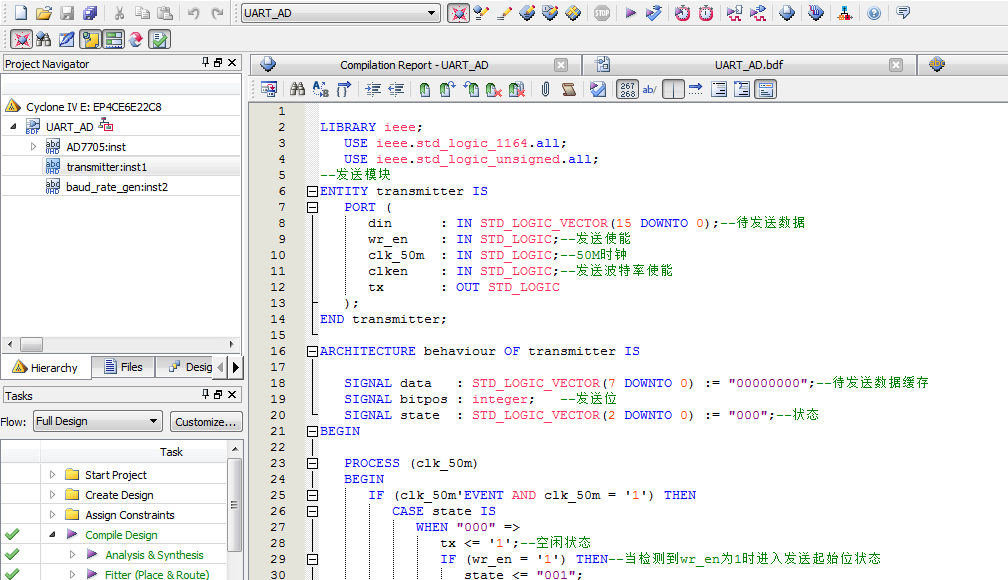

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; USE ieee.std_logic_arith.all; --AD7705时序控制模块 ENTITY AD7705 IS PORT ( clk_50m : IN STD_LOGIC;--时钟 rst_n_i : IN STD_LOGIC;--系统复位信号,低有效 drdy_n_i : IN STD_LOGIC;--AD7705--pin dout_i : IN STD_LOGIC;--AD7705--pin cs_o : OUT STD_LOGIC;--AD7705--pin ad_clk_o : OUT STD_LOGIC;--AD7705--pin ad_din_o : OUT STD_LOGIC;--AD7705--pin data_vld_o : OUT STD_LOGIC;--AD有效 uart_data_o : OUT STD_LOGIC_VECTOR(15 DOWNTO 0)--输出AD数据 ); END AD7705; ARCHITECTURE RTL OF AD7705 IS --定义状态 SIGNAL state : STD_LOGIC_VECTOR(2 DOWNTO 0) := "000"; CONSTANT S_RST : STD_LOGIC_VECTOR(2 DOWNTO 0) := "000";--reset CONSTANT S_CMT_CLK : STD_LOGIC_VECTOR(2 DOWNTO 0) := "001";--write 8'h20 CONSTANT S_CLK : STD_LOGIC_VECTOR(2 DOWNTO 0) := "010";--write 8'h03 CONSTANT S_CMT_SET : STD_LOGIC_VECTOR(2 DOWNTO 0) := "011";--write 8'h10 CONSTANT S_SET : STD_LOGIC_VECTOR(2 DOWNTO 0) := "100";--write 8'h40 CONSTANT S_CMT_DATA : STD_LOGIC_VECTOR(2 DOWNTO 0) := "101";--write 8'h38,read 通道1 CONSTANT S_DATA : STD_LOGIC_VECTOR(2 DOWNTO 0) := "110";--读数AD CONSTANT S_WAIT : STD_LOGIC_VECTOR(2 DOWNTO 0) := "111";--等待DRDY --定义常数 CONSTANT cmt_clk_r : STD_LOGIC_VECTOR(7 DOWNTO 0) := x"20"; CONSTANT clk_r : STD_LOGIC_VECTOR(7 DOWNTO 0) := x"03"; CONSTANT cmt_set_r : STD_LOGIC_VECTOR(7 DOWNTO 0) := x"10"; CONSTANT set_r : STD_LOGIC_VECTOR(7 DOWNTO 0) := x"40"; CONSTANT smt_data_r : STD_LOGIC_VECTOR(7 DOWNTO 0) := x"38"; --定义信号 SIGNAL clk_cnt_r : integer := 0; SIGNAL study_num_s : INTEGER := 0; --计算结果 SIGNAL div_clk_r : STD_LOGIC := '0'; SIGNAL div_clk_cnt_r : integer := 0; SIGNAL clk_vld : STD_LOGIC := '0'; SIGNAL ad_in_r : STD_LOGIC := '0'; SIGNAL div_clk_rr : STD_LOGIC := '0'; SIGNAL div_clk_n_s: STD_LOGIC; SIGNAL div_clk_p_s: STD_LOGIC; SIGNAL ad_data_r : STD_LOGIC_VECTOR(15 DOWNTO 0) := "0000000000000000"; SIGNAL ad_data_int : INTEGER := 0; BEGIN --分频计数 PROCESS (clk_50m) BEGIN IF (clk_50m'EVENT AND clk_50m = '1') THEN IF (rst_n_i = '0') THEN div_clk_cnt_r <= 0; div_clk_rr<='0'; ELSIF (div_clk_cnt_r = 9) THEN--分频比为10 div_clk_cnt_r <= 0; ELSE div_clk_cnt_r <= div_clk_cnt_r + 1; END IF; IF (div_clk_cnt_r >= 5) THEN div_clk_r <= '1';--分频为5MHz ELSE div_clk_r <= '0'; END IF;

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?