名称:串口(UART)接口转FIFO接口设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

串口(UART)接口转FIFO接口

1、设计UART串口发送及接收代码

2、通过UART接收到的数据写入接收FIFO中

3、待发送的数据先写入发送FIFO中,再通过UART发送出去

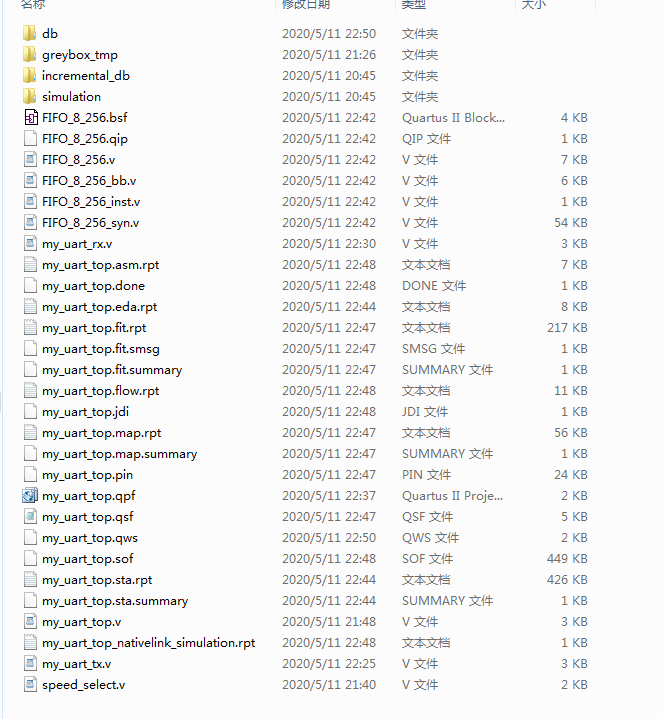

1. 工程文件

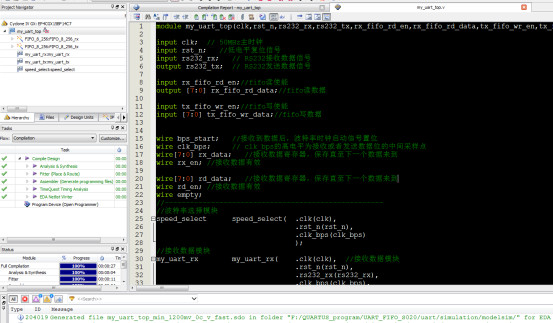

2. 程序文件

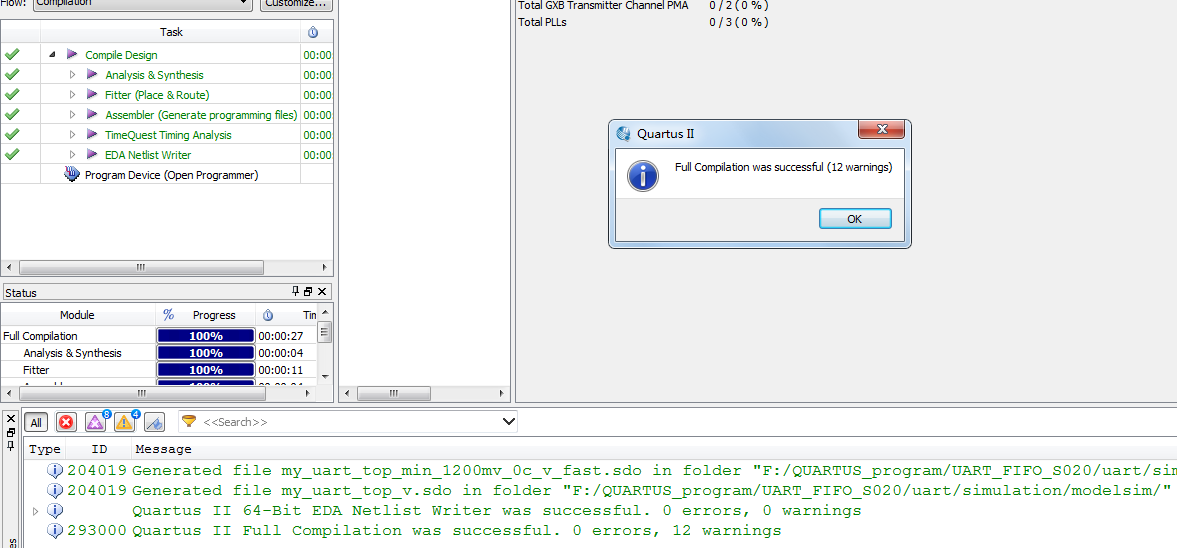

3. 程序综合

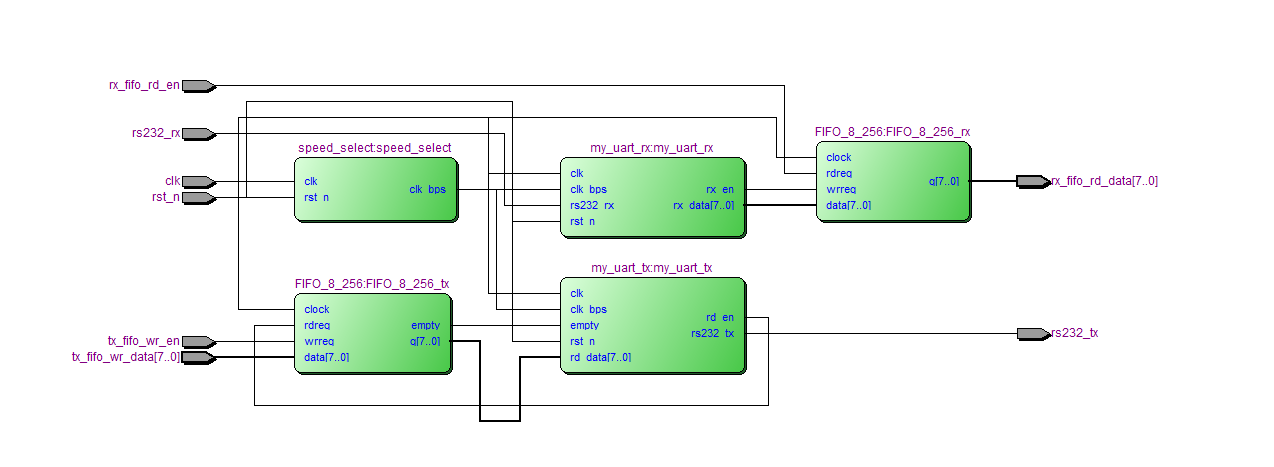

4. RTL图

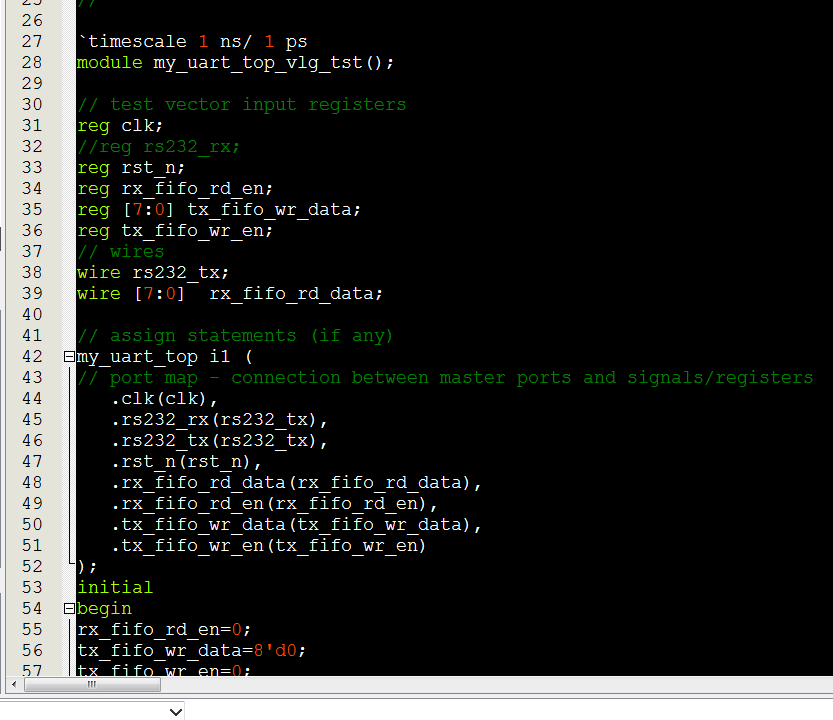

5. Testbench

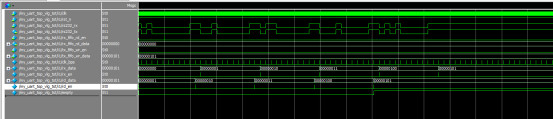

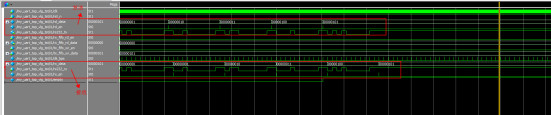

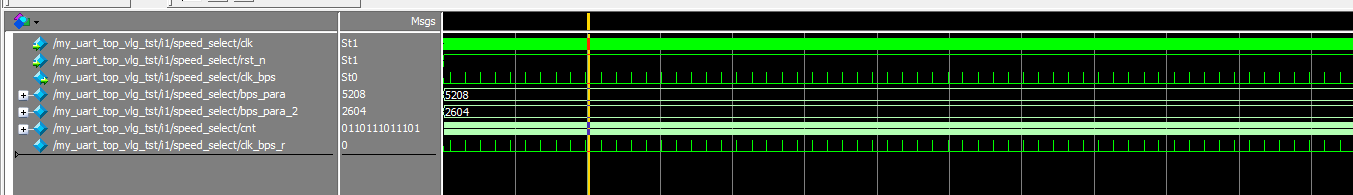

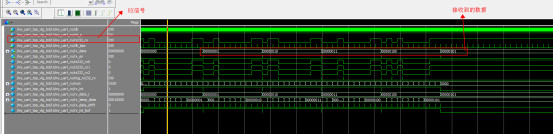

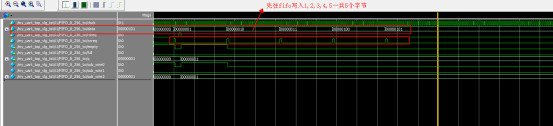

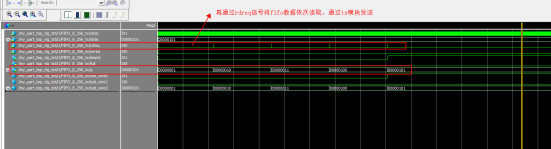

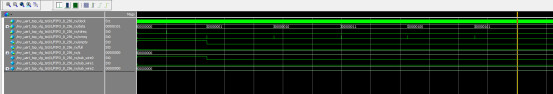

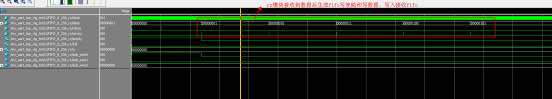

6. 仿真图

整体仿真

波特率模块

发送模块

接收模块

发送FIFO

接收FIFO

部分代码展示:

module my_uart_top(clk,rst_n,rs232_rx,rs232_tx,rx_fifo_rd_en,rx_fifo_rd_data,tx_fifo_wr_en,tx_fifo_wr_data); input clk;// 50MHz主时钟 input rst_n;//低电平复位信号 input rs232_rx;// RS232接收数据信号 output rs232_tx;//RS232发送数据信号 input rx_fifo_rd_en;//fifo读使能 output [7:0] rx_fifo_rd_data;//fifo读数据 input tx_fifo_wr_en;//fifo写使能 input [7:0] tx_fifo_wr_data;//fifo写数据 wire bps_start;//接收到数据后,波特率时钟启动信号置位 wire clk_bps;// clk_bps的高电平为接收或者发送数据位的中间采样点 wire[7:0] rx_data;//接收数据寄存器,保存直至下一个数据来到 wire rx_en;//接收数据有效 wire[7:0] rd_data;//接收数据寄存器,保存直至下一个数据来到 wire rd_en;//接收数据有效 wire empty; //---------------------------------------------------- //波特率选择模块 speed_selectspeed_select(.clk(clk), .rst_n(rst_n), .clk_bps(clk_bps) ); //接收数据模块 my_uart_rxmy_uart_rx(.clk(clk),//接收数据模块 .rst_n(rst_n), .rs232_rx(rs232_rx), .clk_bps(clk_bps), .rx_data(rx_data), .rx_en(rx_en) );

源代码

点击下方的公众号卡片获取

15万+

15万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?