名称:6路抢答器带倒计时计分功能设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

6路抢答器带倒计时计分功能

1、设计抢答器组数最多为6组,每组的序号分别为1,2,3, 4,5, 6,启动后方可抢答,按键后组号在LED显示器上显示,同时封锁其他组的按键信号。

2、设置抢答开启控制键,数字抢答器定时为20秒,通过按键启动抢答器后要求20秒倒计时器开始工作。

3、抢答者在20秒内进行抢答,则有效;若在20秒定时到达时,仍无抢答者则定时器自动清零。

4、具有计分功能, 每组每答对一-题计 10分。

1. 工程文件

2. 程序文件

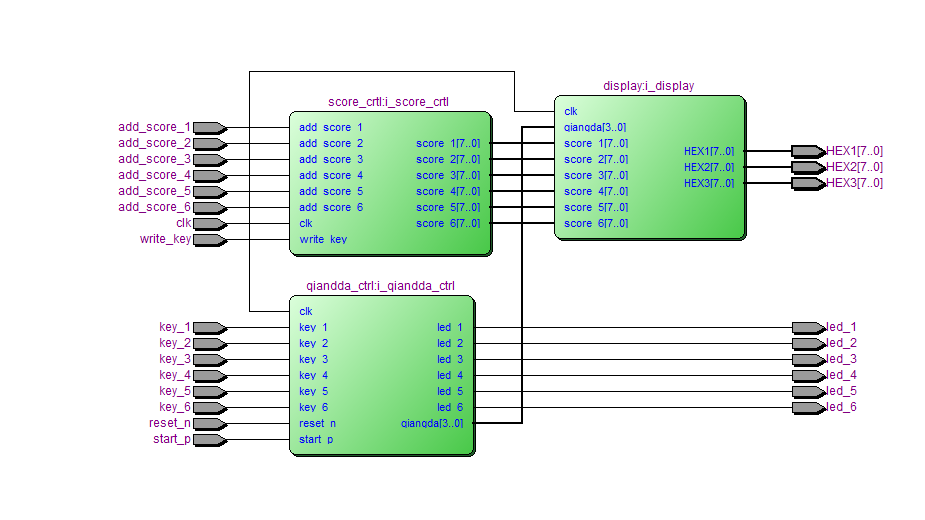

3. 程序编译

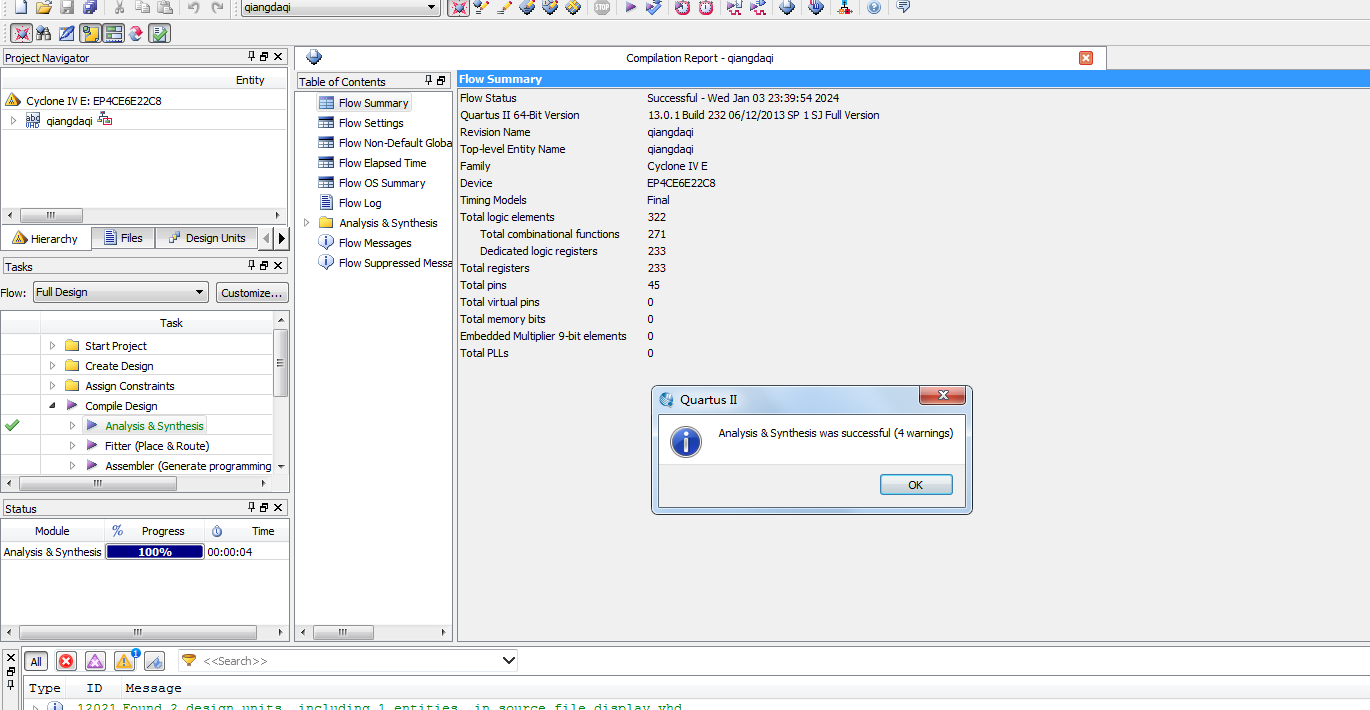

4. RTL图

5. 仿真图

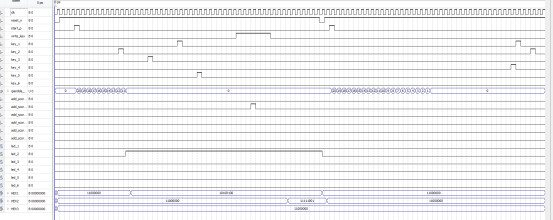

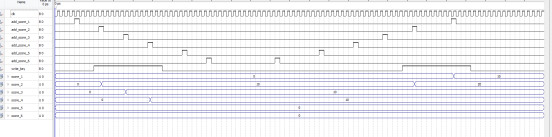

整体仿真图

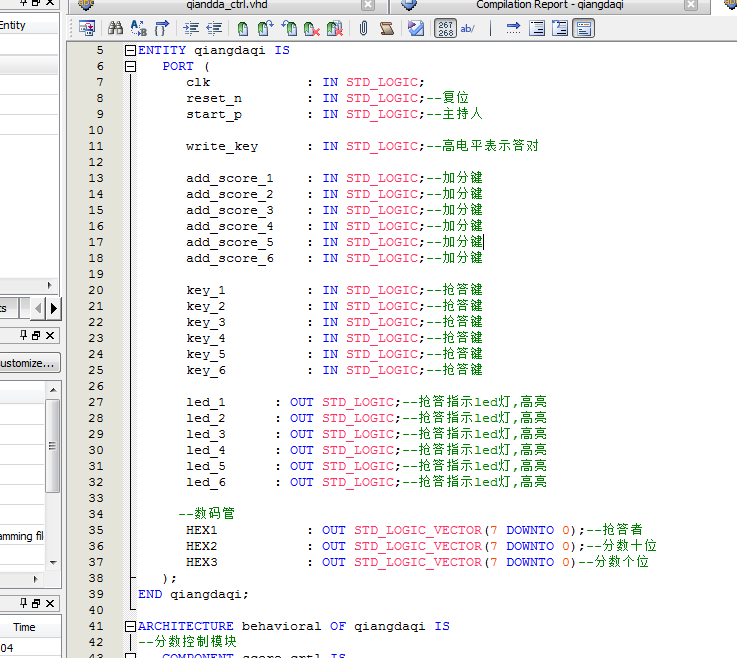

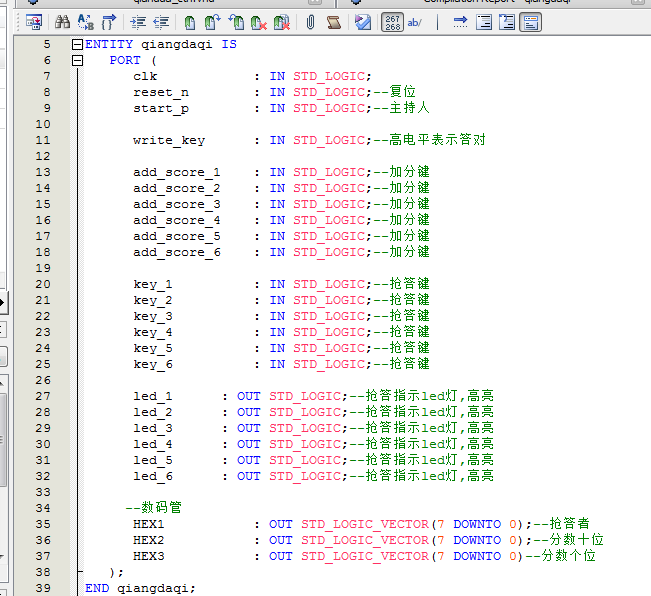

上图为端口信号定义

上图中,复位后,按下主持人控制按键,此时开始抢答,同时开始计时,图中,2号先抢答,led2变为高电平。数码管显示2号,且2号答对(write_kety高电平)。后半段仿真了超时抢答的情况,20秒内没有抢答,后续在抢答也无效。

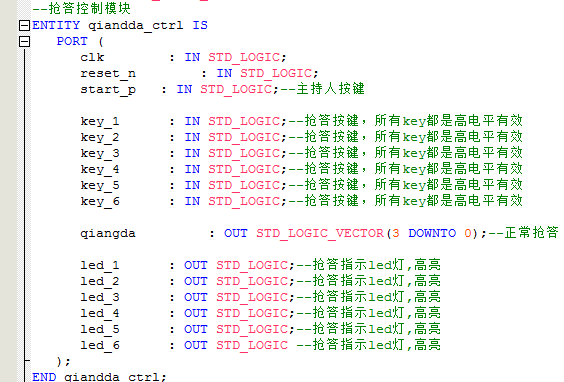

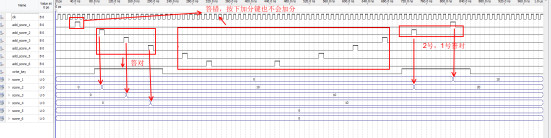

抢答控制模块

上图为端口信号定义

上图中,复位后,按下主持人控制按键,此时开始抢答,同时开始计时,图中,2号先抢答,led2变为高电平。抢答号为2。后半段仿真了超时抢答的情况,20秒内没有抢答,后续再抢答也无效。

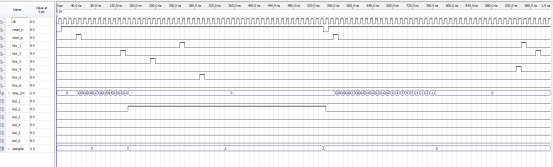

分数控制模块

上图为端口信号定义

上图中,仿真了分数控制模块,write_kety高电平表示答对。当答对时,按下加分按键才能加10分,否则不能加分

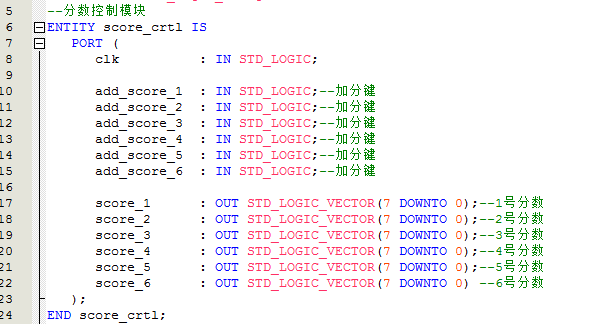

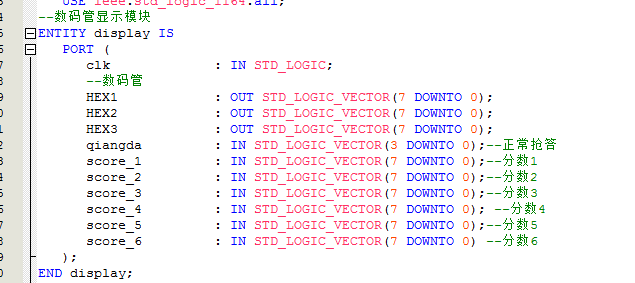

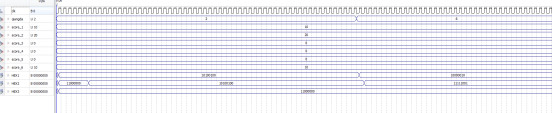

数码管显示模块

上图为端口信号定义

上图中,仿真了显示模块,先后显示了抢答号2和6。显示2时,同时显示了分数为20.

显示6时,同时显示了分数为10.

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --抢答控制模块 ENTITY qiandda_ctrl IS PORT ( clk : IN STD_LOGIC; reset_n : IN STD_LOGIC; start_p : IN STD_LOGIC;--主持人按键 key_1 : IN STD_LOGIC;--抢答按键,所有key都是高电平有效 key_2 : IN STD_LOGIC;--抢答按键,所有key都是高电平有效 key_3 : IN STD_LOGIC;--抢答按键,所有key都是高电平有效 key_4 : IN STD_LOGIC;--抢答按键,所有key都是高电平有效 key_5 : IN STD_LOGIC;--抢答按键,所有key都是高电平有效 key_6 : IN STD_LOGIC;--抢答按键,所有key都是高电平有效 qiangda : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--正常抢答 led_1 : OUT STD_LOGIC;--抢答指示led灯,高亮 led_2 : OUT STD_LOGIC;--抢答指示led灯,高亮 led_3 : OUT STD_LOGIC;--抢答指示led灯,高亮 led_4 : OUT STD_LOGIC;--抢答指示led灯,高亮 led_5 : OUT STD_LOGIC;--抢答指示led灯,高亮 led_6 : OUT STD_LOGIC --抢答指示led灯,高亮 ); END qiandda_ctrl; ARCHITECTURE RTL OF qiandda_ctrl IS TYPE State_type IS (idle, start, qiangda_1, qiangda_2,qiangda_3,qiangda_4,qiangda_5,qiangda_6, s_timeout); -- 定义状态 SIGNAL current_state : State_Type; -- 创建信号 SIGNAL qiangda_temp : STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL time_cnt : STD_LOGIC_VECTOR(7 DOWNTO 0); --20秒计数 BEGIN --状态机-- PROCESS (clk,reset_n) BEGIN IF (reset_n = '0') THEN--复位 current_state <= idle;--开始抢答 ELSIF (clk'EVENT AND clk = '1') THEN CASE current_state IS WHEN idle =>--未开始抢答状态 IF (start_p = '1') THEN--主持人按键 current_state <= start;--开始抢答 ELSE current_state <= idle; END IF; WHEN start =>--开始抢答状态 IF (key_1 = '1') THEN current_state <= qiangda_1;--1号抢答 ELSIF (key_2 = '1') THEN current_state <= qiangda_2;--2号抢答 ELSIF (key_3 = '1') THEN current_state <= qiangda_3;--3号抢答 ELSIF (key_4 = '1') THEN current_state <= qiangda_4;--4号抢答 ELSIF (key_5 = '1') THEN current_state <= qiangda_5;--5号抢答 ELSIF (key_6 = '1') THEN current_state <= qiangda_6;--6号抢答 ELSIF (time_cnt = "00000000") THEN--20秒 current_state <= s_timeout;--超时 ELSE current_state <= start; END IF; WHEN qiangda_1 => current_state <= qiangda_1;--1号抢答 WHEN qiangda_2 => current_state <= qiangda_2;--2号抢答 WHEN qiangda_3 => current_state <= qiangda_3;--3号抢答 WHEN qiangda_4 => current_state <= qiangda_4;--4号抢答 WHEN qiangda_5 => current_state <= qiangda_5;--5号抢答 WHEN qiangda_6 => current_state <= qiangda_6;--6号抢答 WHEN s_timeout => current_state <= idle ; WHEN OTHERS => current_state <= idle; END CASE; END IF; END PROCESS;

源代码

点击下方的公众号卡片获取

894

894

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?