名称:出租车计价器设计Verilog代码Quartus SOPCEDA实验箱(文末获取)

软件:Quartus

语言:Verilog

代码功能:

功能描述

1、 起步价为13元,起步公里为3公里。

2、 超过3公里,每公里按2元收费。

3、 要求用数码管显示里程、等候时间和计费;用按钮实现启动、等候、结束等功能。

4、 单程行驶里程超过15公里,每公里租价加收50%

5、 等候时间累积5分钟,加收1元。

6、 自定义其它功能

预计模块划分:

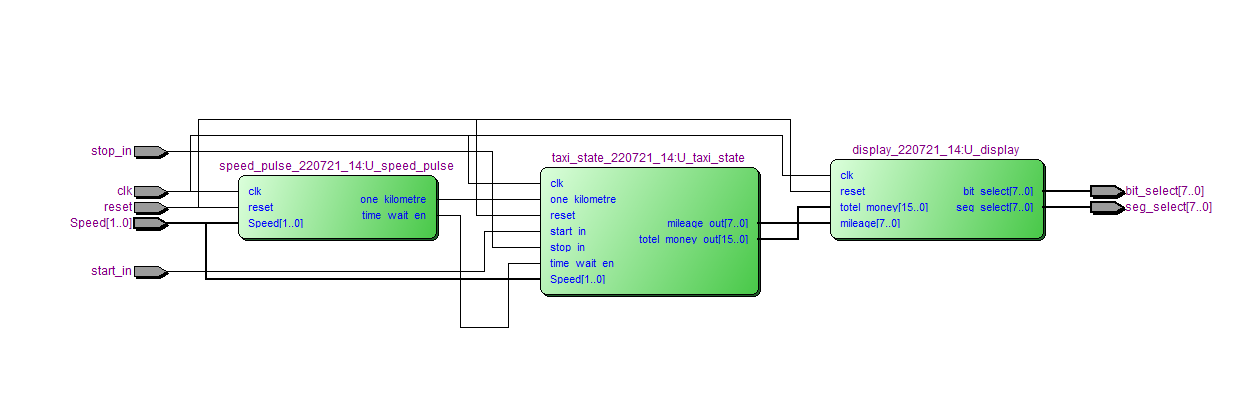

1、 公里脉冲模块,用于产生1公里脉冲信号,用于公里计费。使用计数器实现信号的产生。

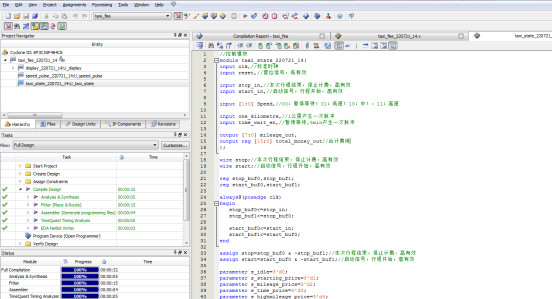

2、 控制模块,使用状态机控制实现出租车计费器的主要功能,包括起步价、安公里计费。时间计费等。

3、 数码管显示模块,用数码管显示里程、等候时间和计费,将控制模块输出的里程、等候时间和费用通过译码器显示为数码管上的数字。

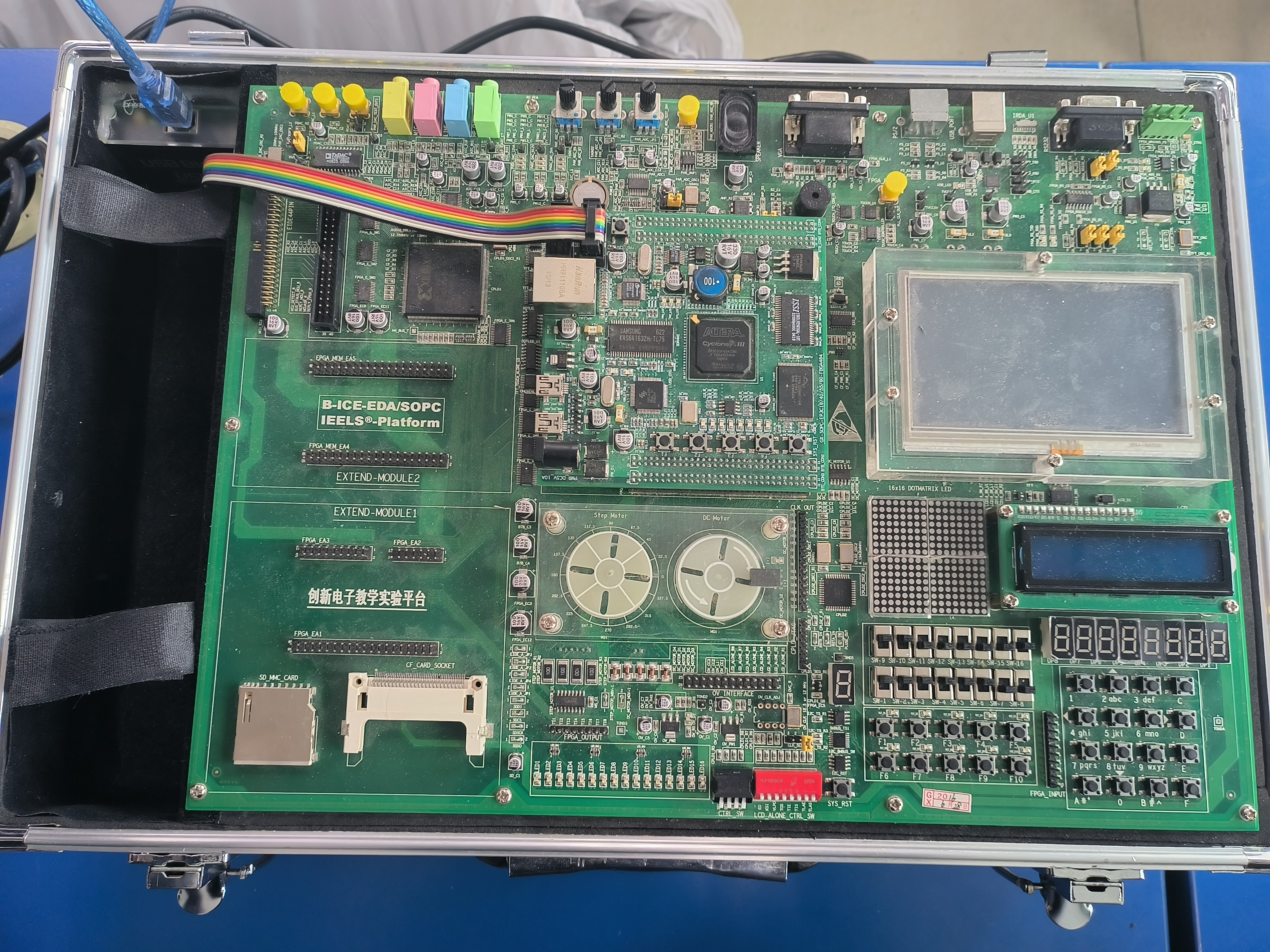

本代码已在SOPCEDA实验箱验证,SOPCEDA实验箱如下,其他开发板可以修改管脚适配:

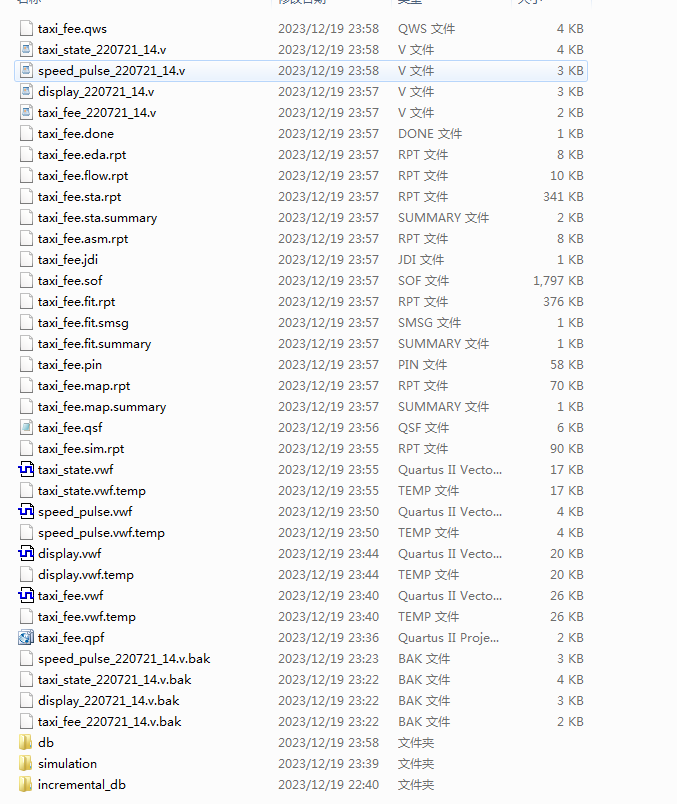

1. 工程文件

2. 程序文件

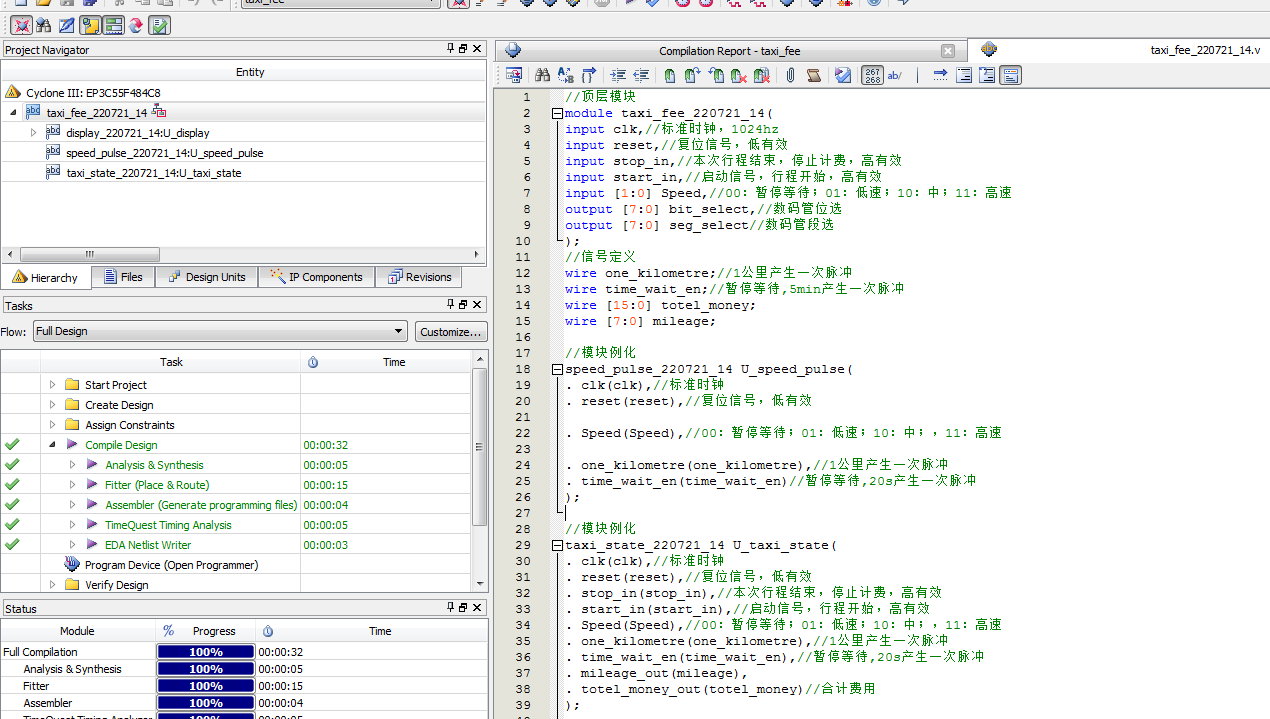

3. 程序编译

4. RTL图

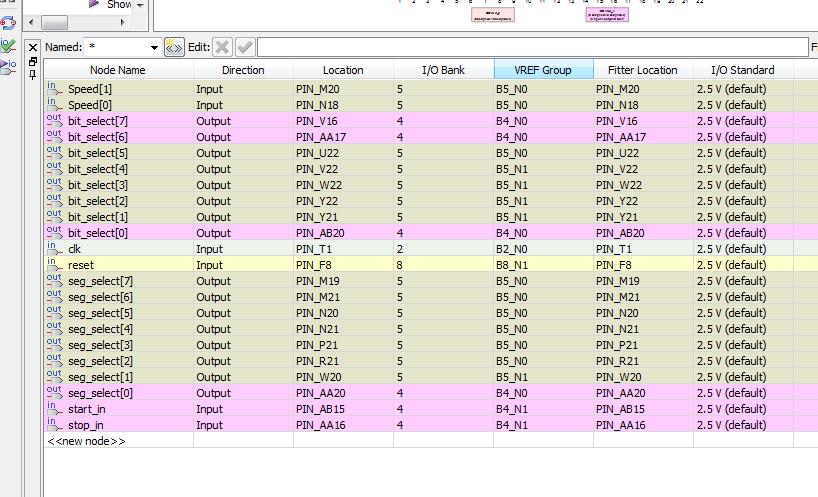

5. 管脚分配

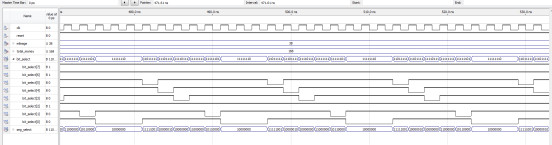

6. 仿真图

顶层模块

公里及时间产生模块

控制模块

显示模块

部分代码展示:

//顶层模块 module taxi_fee_220721_14( input clk,//标准时钟,1024hz input reset,//复位信号,低有效 input stop_in,//本次行程结束,停止计费,高有效 input start_in,//启动信号,行程开始,高有效 input [1:0] Speed,//00:暂停等待;01:低速;10:中;11:高速 output [7:0] bit_select,//数码管位选 output [7:0] seg_select//数码管段选 ); //信号定义 wire one_kilometre;//1公里产生一次脉冲 wire time_wait_en;//暂停等待,5min产生一次脉冲 wire [15:0] totel_money; wire [7:0] mileage; wire [7:0] wait_time;//时间 wire clk_1KHz; //分频模块,分频到1000Hz fenping i_fenping( . clk_in(clk), . clk_1000Hz(clk_1KHz) ); //模块例化 speed_pulse_220721_14 U_speed_pulse( . clk(clk_1KHz),//标准时钟 . reset(reset),//复位信号,低有效 . Speed(Speed),//00:暂停等待;01:低速;10:中;,11:高速 . wait_time(wait_time), . one_kilometre(one_kilometre),//1公里产生一次脉冲 . time_wait_en(time_wait_en)//暂停等待,20s产生一次脉冲 ); //模块例化 taxi_state_220721_14 U_taxi_state( . clk(clk_1KHz),//标准时钟 . reset(reset),//复位信号,低有效 . stop_in(stop_in),//本次行程结束,停止计费,高有效 . start_in(start_in),//启动信号,行程开始,高有效 . Speed(Speed),//00:暂停等待;01:低速;10:中;,11:高速 . one_kilometre(one_kilometre),//1公里产生一次脉冲 . time_wait_en(time_wait_en),//暂停等待,20s产生一次脉冲 . mileage_out(mileage), . totel_money_out(totel_money)//合计费用 );

源代码

点击下方的公众号卡片获取

1025

1025

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?