名称:35进制计数器设计Quartus仿真(文末获取)

软件:Quartus

功能:

35进制计数器的设计与实现要求

1、按照模块化层次化,自顶向下的设计与自底向上的实现进行;

2、提交各层次的原理图和仿真图;

3、输出计数结果以2位842BCD码的形式给出

1. 设计原理

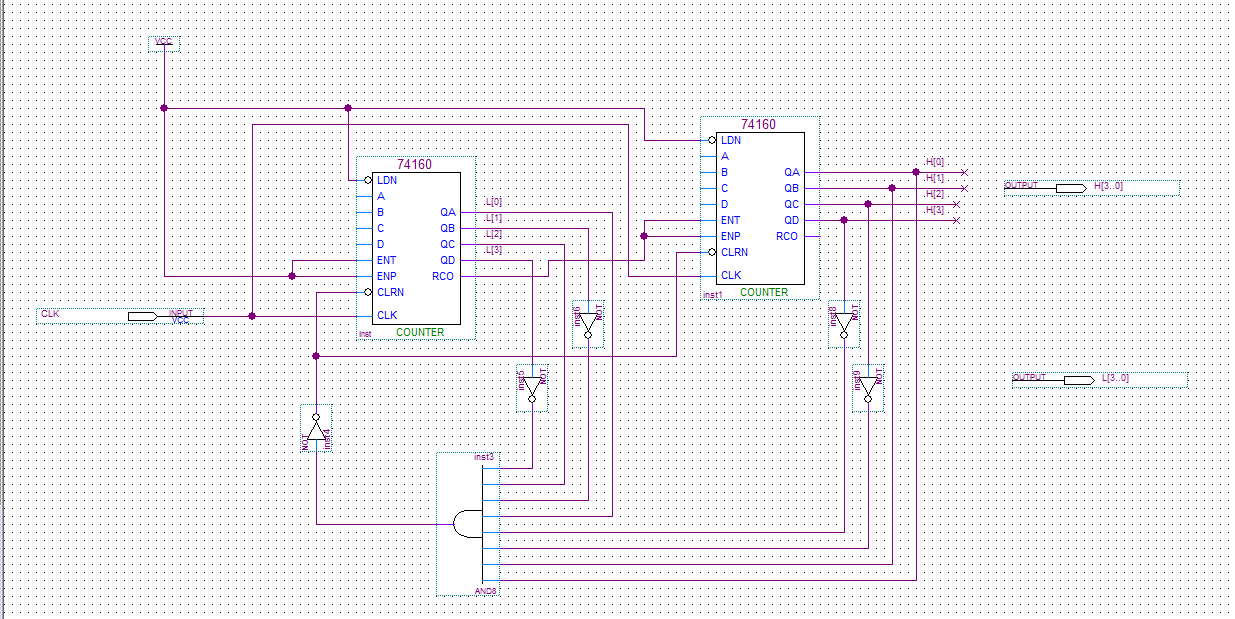

设计35进制计数器,即计数0~34,输出用2位8421BCD码显示。设计思路如下:在使用2片74160芯片设计,74160是10进制计数器,通过俩片74150组合可以设计为35进制。一片74160作为个位计数,一片作为十位计数,当个位计数到9时,十位加1,若个位为5且十位为3时表示计数到35.此时将系统复位清零,即重新开始0~34计数。

2. 工程文件

Quartus9.0版本

3. 电路图

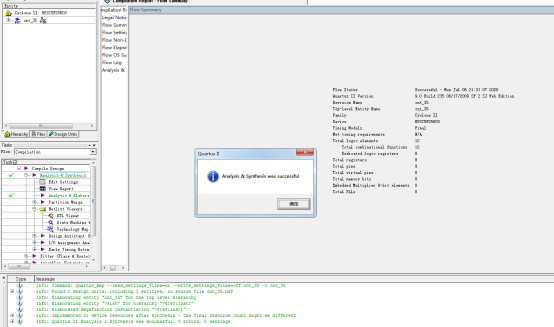

4. 编译

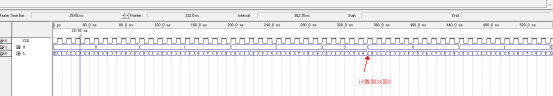

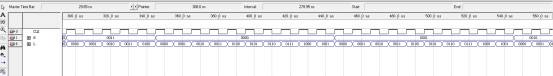

5. 仿真图

二进制显示

源代码

点击下方的公众号卡片获取

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?