八位计数器的设计

仿真代码

module count8 (

input clk, // 时钟信号

input rst, // 复位信号

output reg [7:0] count // 输出计数器值

);

always @(posedge clk or posedge rst) begin

if (rst) begin // 如果复位信号为高电平,则计数器被重置为0

count <= 8'b0;

end

else begin // 如果时钟信号为上升沿,则计数器增加1

count <= count + 1;

end

end

endmodule

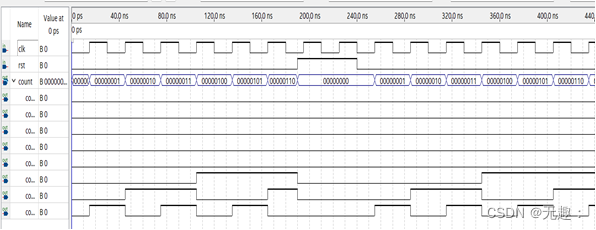

仿真波形

波形图说明:在每个时钟“clk”的上升沿时,计数器开始自动从“00000000”增加到“11111111”,当计数器遇到复位信号“rst”为高电平时,计数器会自动清零,计数器即会变成“00000000”,然后又重新开始计数。

该文描述了一个八位计数器的设计,使用Verilog语言编写。当接收到时钟信号的上升沿或复位信号时,计数器状态会发生变化。在复位信号为高时,计数器清零;否则,在每个时钟上升沿,计数器加1,从0递增到255。仿真波形显示了这一过程。

该文描述了一个八位计数器的设计,使用Verilog语言编写。当接收到时钟信号的上升沿或复位信号时,计数器状态会发生变化。在复位信号为高时,计数器清零;否则,在每个时钟上升沿,计数器加1,从0递增到255。仿真波形显示了这一过程。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?