名称:整点报时数字电子时钟设计VHDL代码Quartus 正点原子开拓者开发板

软件:Quartus

语言:VHDL

代码功能:

设计一数字电子时钟

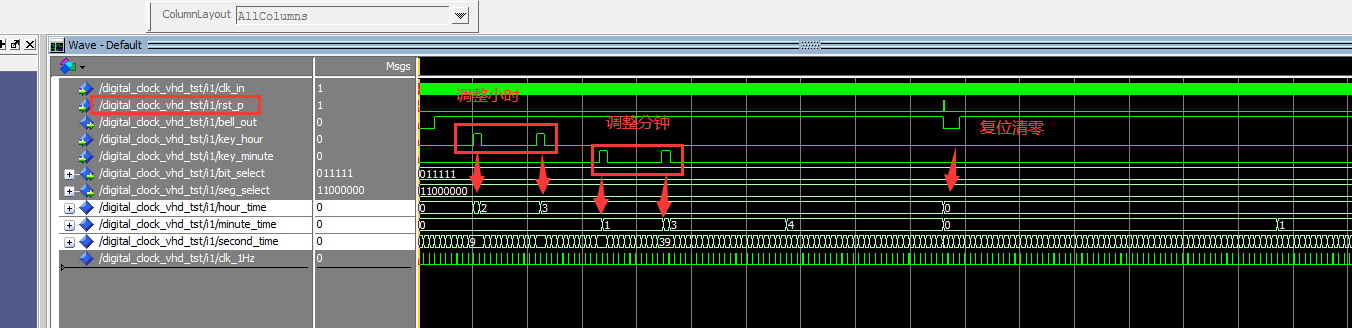

基本要求(必须完成):具有时、分、秒的计数和显示功能,以24小时循环计时;具有清零,整点报时(报时的形式不做要求,例如:几点就设置几个脉冲)功能

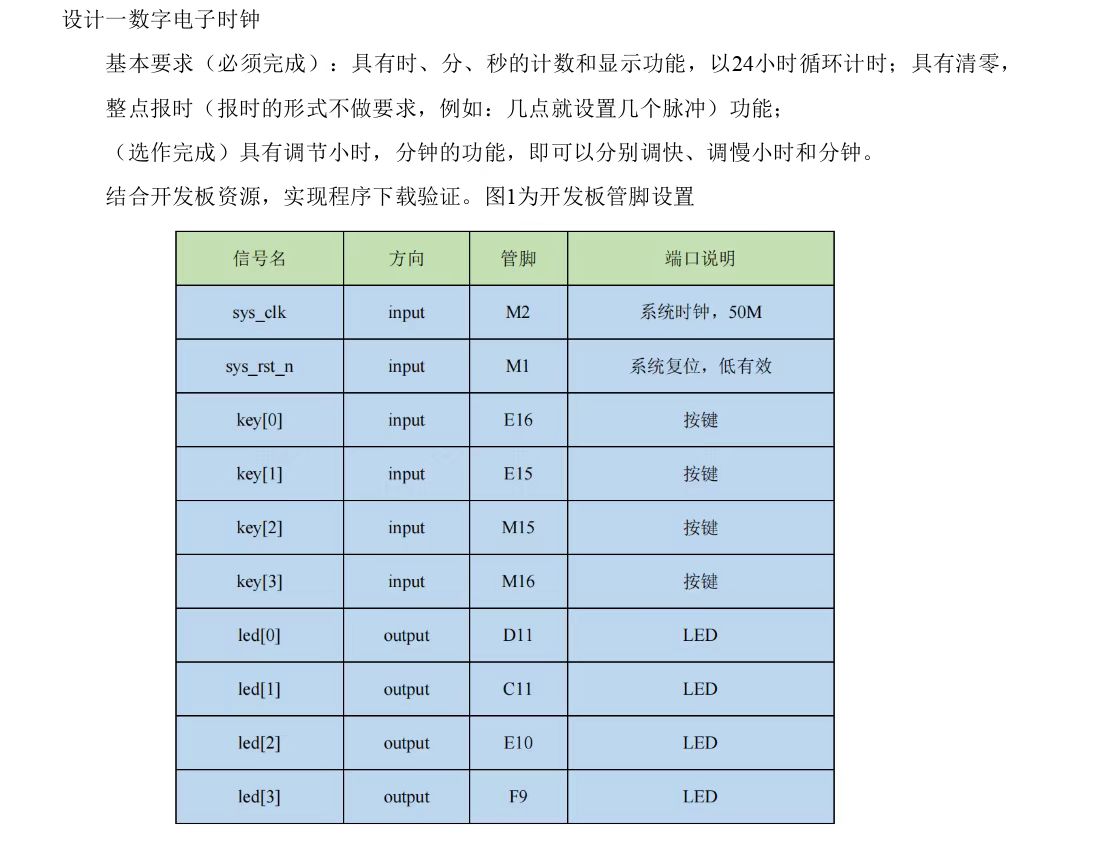

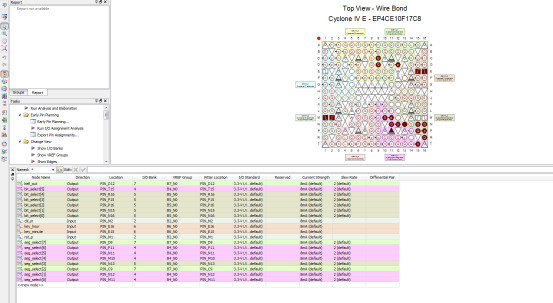

(选作完成)具有调节小时,分钟的功能,即可以分别调快、调慢小时和分钟。结合开发板资源,实现程序下载验证。图1为开发板管脚设置

本代码已在正点原子开拓者开发板验证,正点原子开拓者开发板如下,其他开发板可以修改管脚适配:

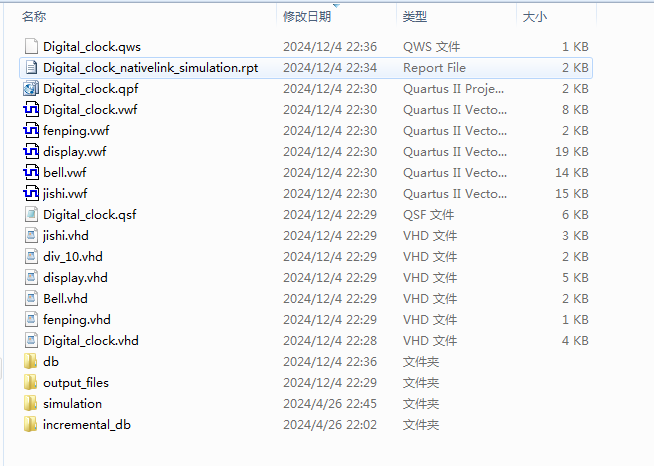

1. 工程文件

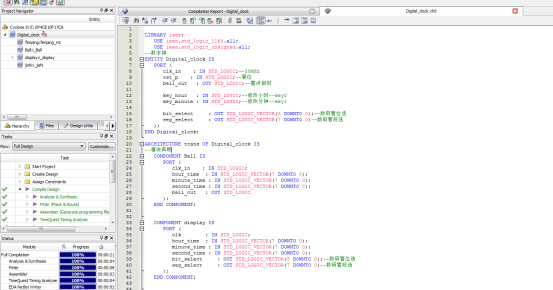

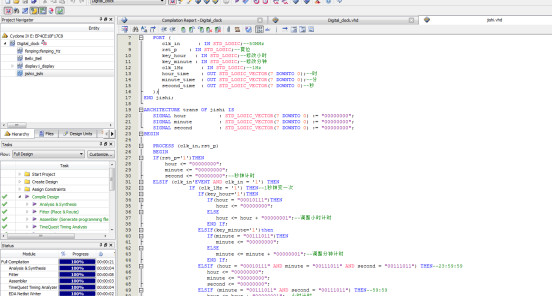

2. 程序文件

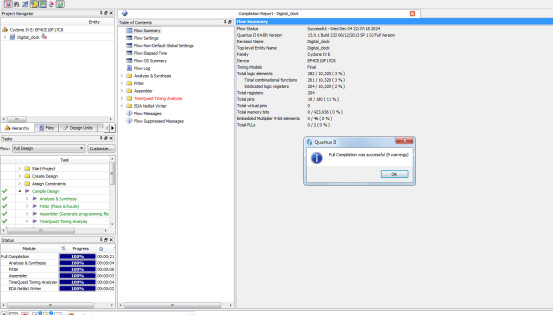

3. 程序编译

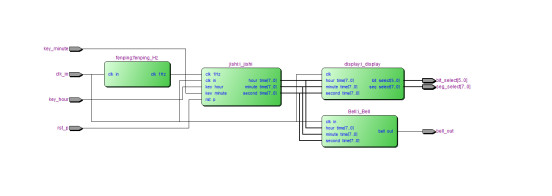

4. RTL图

5. 管脚分配

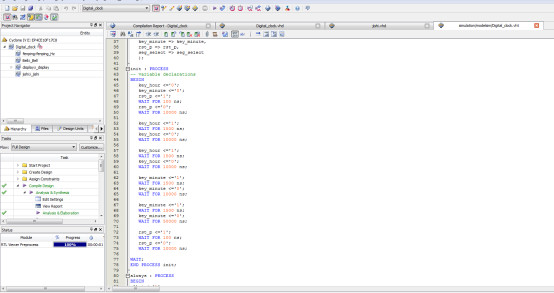

6. Testbench

7. 仿真图

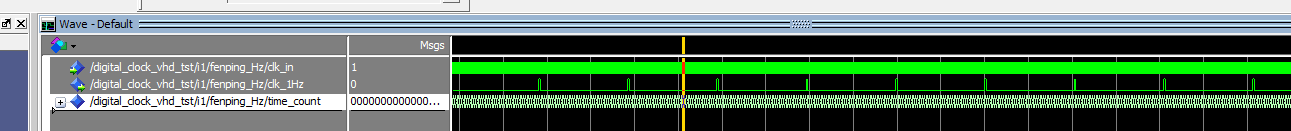

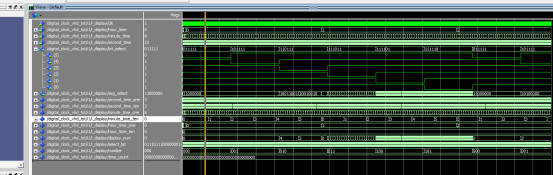

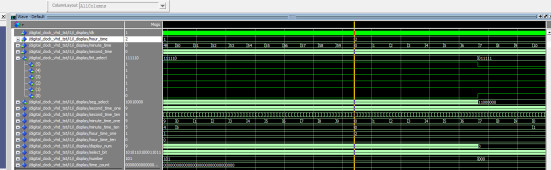

顶层仿真

分频模块

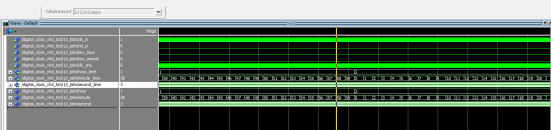

计时模块

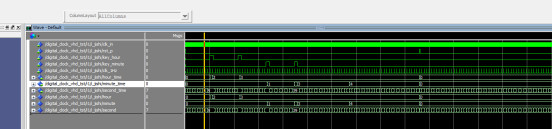

报时模块

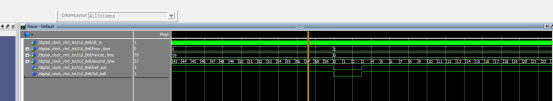

显示模块

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --数字钟 ENTITY Digital_clock IS PORT ( clk_in : IN STD_LOGIC;--50MHz rst_p : IN STD_LOGIC;--复位--reset bell_out : OUT STD_LOGIC;--整点报时 key_hour : IN STD_LOGIC;--修改小时--长按--Key0 key_minute : IN STD_LOGIC;--修改分钟--长按--Key1 bit_select : OUT STD_LOGIC_VECTOR(5 DOWNTO 0);--数码管位选 seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管段选 ); END Digital_clock; ARCHITECTURE trans OF Digital_clock IS --模块声明 COMPONENT Bell IS PORT ( clk_in : IN STD_LOGIC; hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); bell_out : OUT STD_LOGIC ); END COMPONENT; COMPONENT display IS PORT ( clk : IN STD_LOGIC; hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); bit_select : OUT STD_LOGIC_VECTOR(5 DOWNTO 0);--数码管位选 seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管段选 ); END COMPONENT; COMPONENT fenping IS PORT ( clk_in : IN STD_LOGIC; clk_1Hz : OUT STD_LOGIC ); END COMPONENT; COMPONENT jishi IS PORT ( clk_in : IN STD_LOGIC; rst_p : IN STD_LOGIC;--复位 key_hour : IN STD_LOGIC;--修改小时 key_minute : IN STD_LOGIC;--修改分钟 clk_1Hz : IN STD_LOGIC; hour_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); minute_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); second_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END COMPONENT; SIGNAL hour_time : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL minute_time : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL second_time : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL clk_1Hz : STD_LOGIC; BEGIN --分频到1Hz fenping_Hz : fenping PORT MAP ( clk_in => clk_in, clk_1Hz => clk_1Hz );

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?