UART、USART、I2C和SPI对比

| UART | USART | I2C | SPI | |

|---|---|---|---|---|

| 英文名 | Universal Asynchronous Receiver/Transmitter | Universal Synchronous/Asynchronous Receiver/Transmitter | Inter-Integrated Circuit | Serial Peripheral Interface |

| 中文名 | 通用异步收发传输器 | 通用同步/异步串行接收/发送器 | 集成电路总线 | 串行外设接口 |

| 发明公司 | DEC(Digital Equipment Corporation) | - | Philips | Motorola |

| I/O线 | TX - 数据发送接口 RX - 数据接受接口 | TX - 数据发送接口 RX - 数据接受接口 SW_RX - 数据接收引脚 nRTS - Request To Send nCTS - Clear to Send SCLK - 时钟 | SCL - 串行时钟线 SDA - 串行数据线接口 | MOSI - (主机输出/ 从机输入) MISO - (主机输入/ 从机输出) SCLK - 时钟信号 CS - 片选 |

| 速度 | 几百 - 1.152Mbps | 同UART | 100kbps(标准模式) 400kbps(快速模式) 3.4Mbps(高速模式) | 几Mbps,比I2C快 |

| 双工 | 全双工 | 全双工 | 半双工 | 全双工 |

| 同/异 | 异步 | 同步 or 异步 | 同步 | 同步 |

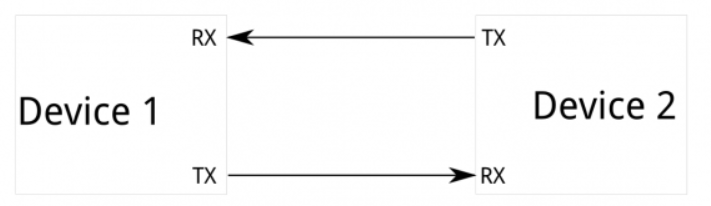

UART设备连接和时序

设备连接示意图

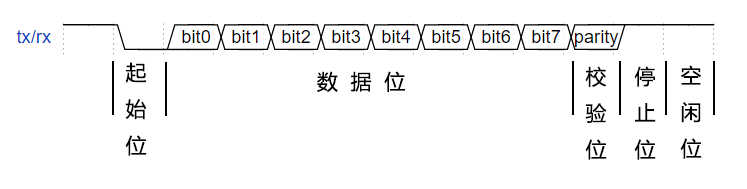

时序

- 空闲位:高电平1表示空闲位

- 数据位可以是4、5、6、7、8、9bit等,一般为8bit,先发送最低位,最后发送最高位

- 奇偶校验位:1bit

- 无校验(no parity)

- 奇校验(odd parity):如果数据中1的个数为偶数,则校验位为1,从而使1的总数为奇数;反之为0

- 偶校验(even parity):如果数据中1的个数为奇数,则校验位为1,从而使1的总数为偶数;反之为0

- mark parity:校验位时钟为1

- space parity:校验位始终为0

- 停止位:1、1.5、2为高电平

- 波特率:数据传输速率,单位bps(bits per second),常见有1200,2400,4800,19200等,假设波特率为9600,那么每一位(起始位,数据位的每一位)的时间宽度为1/9600s

USART

- UART加强版,带时钟

- 由时钟发生器、数据发送器和接收器组成,控制寄存器为所有的模块共享

- 同步操作时,可主机时钟同步,也可从机时钟同步

- 支持5、6、7、8和9位数据位,1或2位停止位的串行数据帧结构

- 三个完全独立的中断,TX发送完成、TX发送数据寄存器空、RX接收完成

- 支持多机通信模式

- 支持倍速异步通信模式

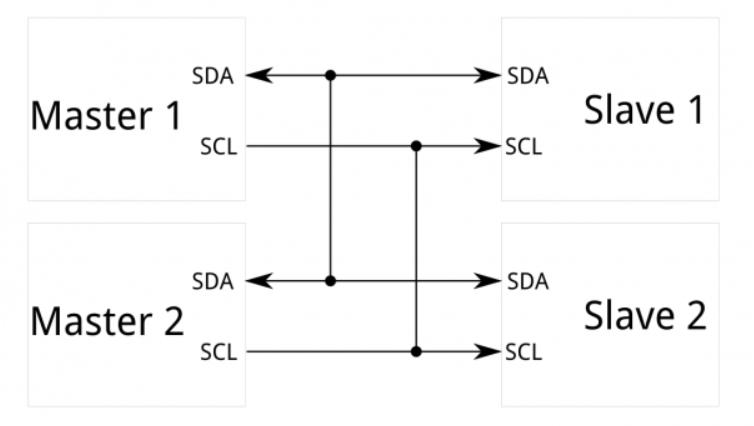

I2C设备连接和时序

设备连接示意图

Master

- This is the device that generates clock, starts communication, sends I2C commands and stops communication

Slave

- This is the device that listens to the bus and is addressed by the master

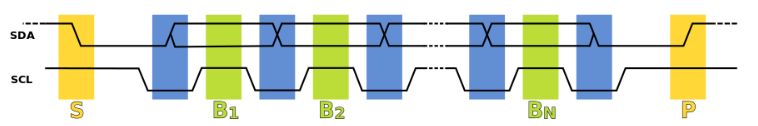

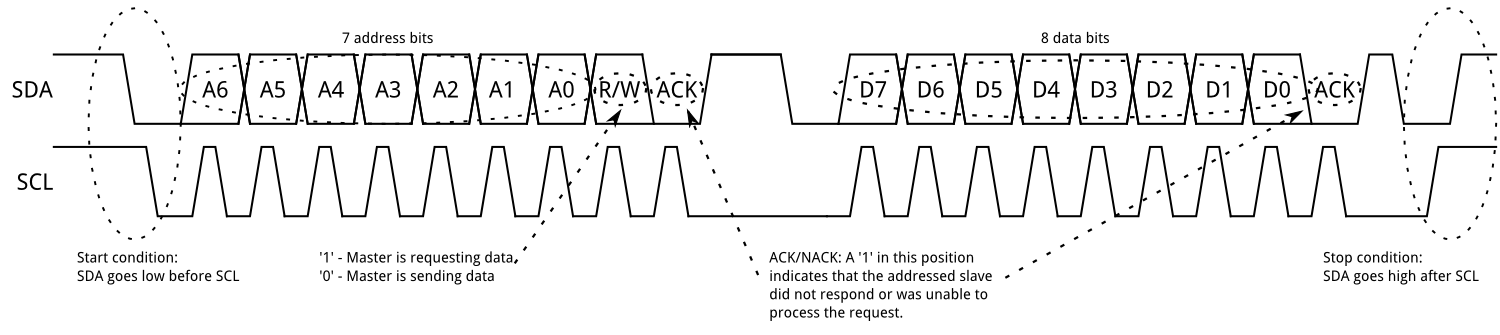

时序

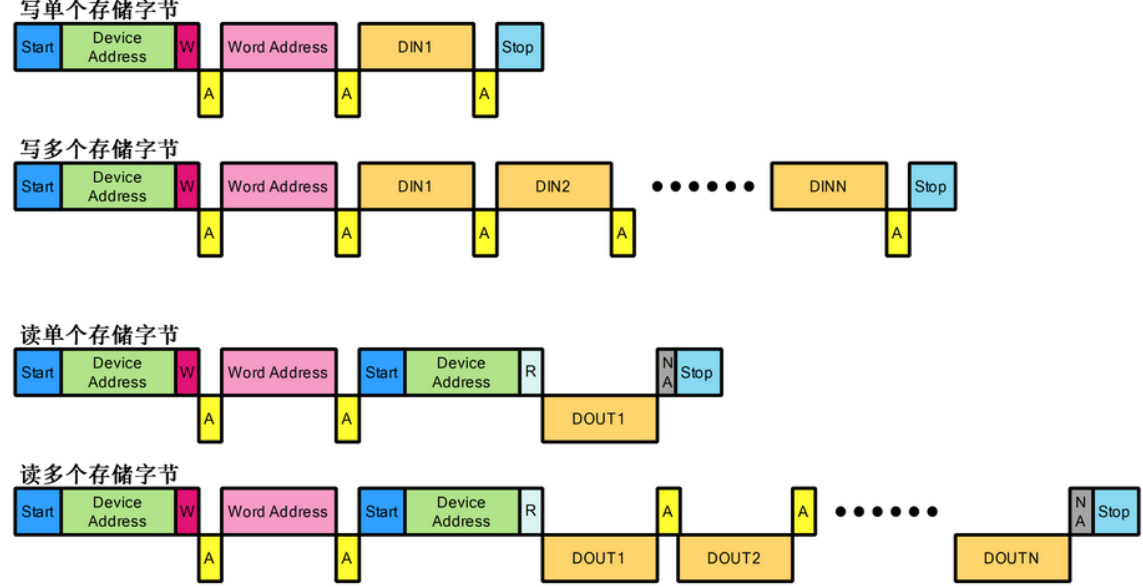

I2C 读写E2PROM

开始信号(S):SCL高时,SDA的下降沿

停止信号(P):SCL高时,SDA的上升沿

数据信号(B):在SCL低时变化,SCL高时保持稳定

应答信号(ACK):0, 接收者每接收到一个byte,回复一个ack表示自己成功接收到,master写slave时,由slave回给master,master读slave时,由master回给slave

应答信号(NACK)发生在以下几种情况:

- bus上没有receiver可以给发送者回复ACK

- receiver正在处理某些东西,不能对master进行回应

- receiver不能理解获取的命令或数据

- receiver不能再接收数据(内部fifo满了?)

- master从slave读数据时,通过回复NACK来结束传输

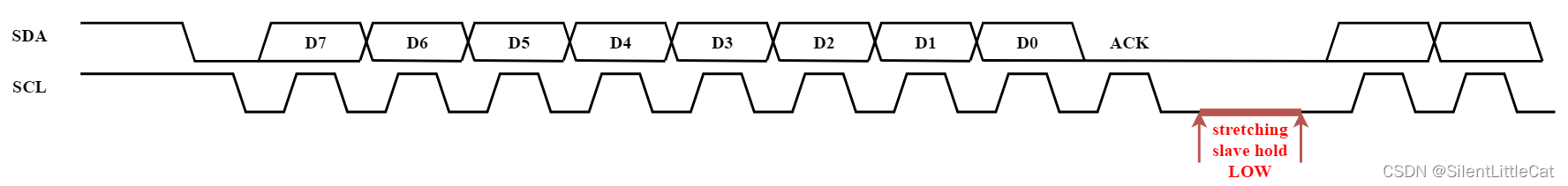

clock stretching

- 通过将SCL拉低来暂停传输,传输直到SCL被拉高才能继续进行

- 可选的,因为很多slave没有驱动SCL的能力

- byte level,设备接收数据的速度很快,但储存的速度较慢,slave可以在接收并回复ACK后继续将SCL拉低(表示自己仍在控制SCL),此时master不能控制SCL,传输暂停,等slave储存完数据后,释放SCL,传输继续

- bit level,设备可以通过clock stretching 延长SCL的低电平周期,降低bus的速度以适应设备内部的操作速率

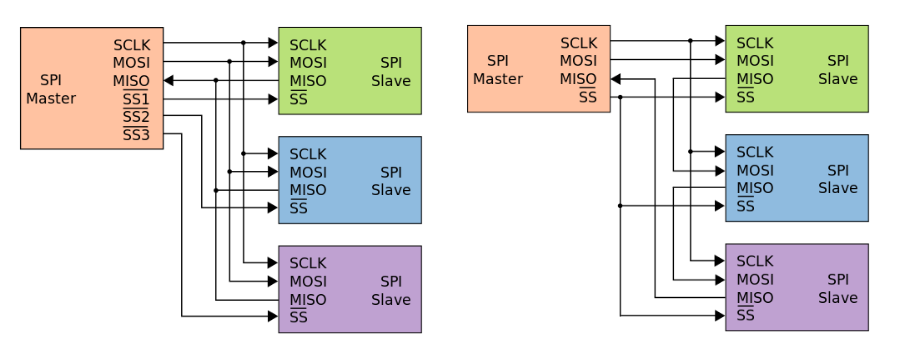

SPI设备连接和时序

SPI设备连接

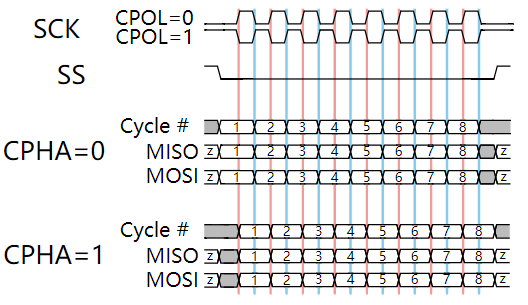

时序

CPOL(Clock Polarity)、CPHA(Clock Phase)决定数据的稳定、改变与时钟上升沿、下降沿的关系

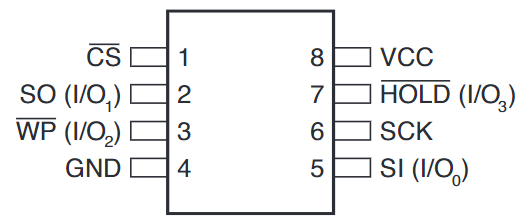

AT25DQ161

- 16Mb 2.7V Minimum SPI Serial Flash Memory with Dual-I/O and Quad-I/O Support

- CS: Chip Select

- SCK: Serial Clock

- SI: Serial Input or I/O0 in Quad-I/O mode

- SO: Serial Output or I/O1 in Quad-I/O mode

- WP: Write Protect or I/O2 in Quad-I/O mode

- HOLD: Hold(temporarily pause serial communication without deselecting or resetting the device) or I/O3 in Quad-I/O mode

- VCC、GND

STM32系统学习——USART(串口通信)

USART

AT25DQ161

I2C-bus specification and user manual

I2C Bus Specification

E2PROM

Introduction to SPI Interface

8444

8444

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?