目录

(摘抄自《FPGA那些事儿–TimeQuest静态时序分析REV7.0》)

前言

首先得有建立时间Tsetup和保持时间Thold的概念

还要有两者和Clock Skew(时钟偏移)

Tco(寄存器发送数据时需要的“最小持续(更新)时间”,个人理解为寄存器入口到出口的连线和逻辑延时)

Tdata(两级寄存器之间的逻辑延时)的关系

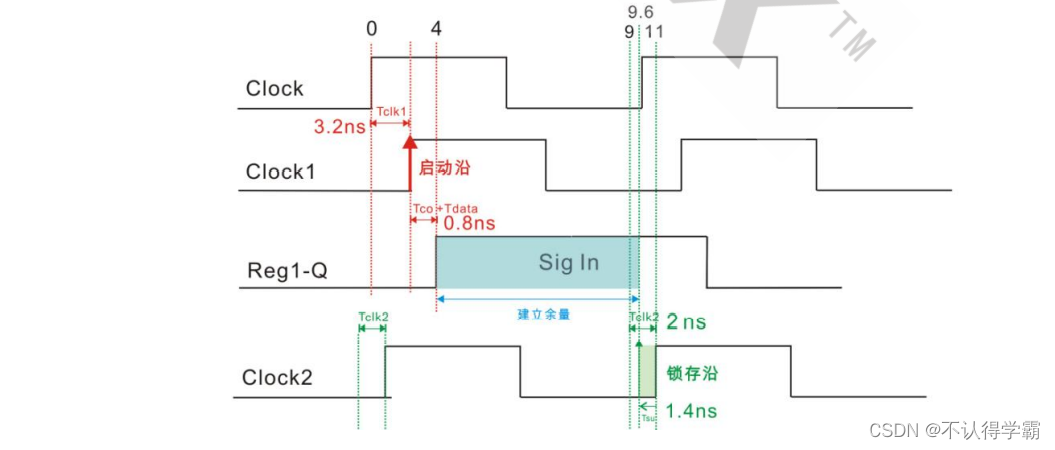

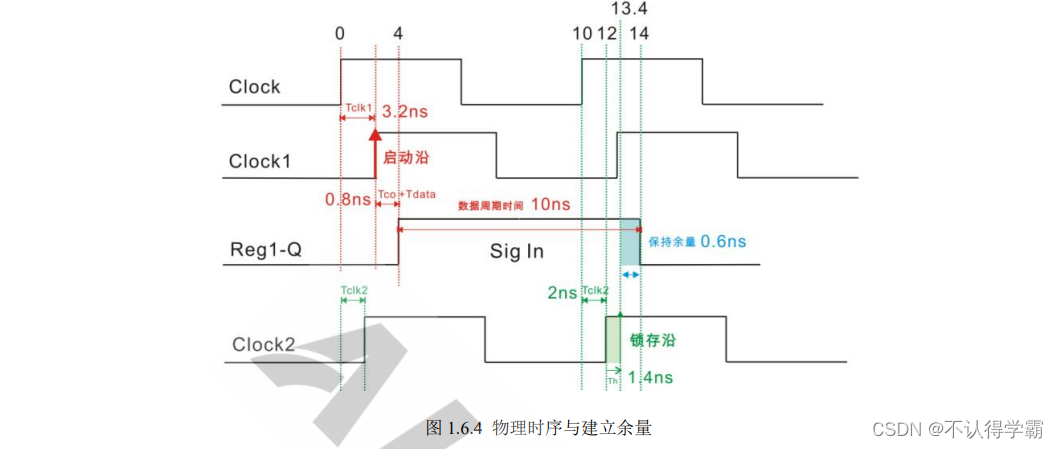

借用大神的图(两级寄存器余量示意图)

建立余量

保持余量

实际就是几个时间的组成和逻辑关系式,细看还是容易看懂的,就是有时候可能会忘,但看一次明白一次。

正题

Timing Analyzer基础知识

时序约束的实质就是满足每一个触发器的建立时间和保持时间。

网表:个人理解,就是

本文介绍了Quartus Timing Analyzer的基础知识和使用方法,包括时序约束的实质、网表概念、SDC网表及其基本单位。通过创建sdc文件进行时钟约束,并查看时序报告来确保建立时间和保持时间的合规性。虽然作者对工具的全面理解仍有待深入,但已能进行简单的时序分析操作。

本文介绍了Quartus Timing Analyzer的基础知识和使用方法,包括时序约束的实质、网表概念、SDC网表及其基本单位。通过创建sdc文件进行时钟约束,并查看时序报告来确保建立时间和保持时间的合规性。虽然作者对工具的全面理解仍有待深入,但已能进行简单的时序分析操作。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?