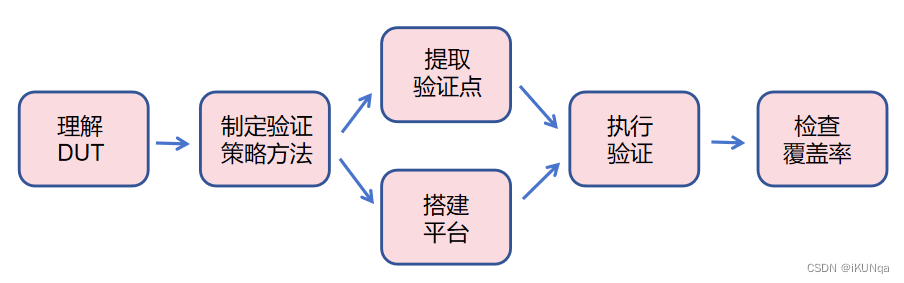

DUT理解

功能验证DUT(待测试的设计代码)

设计人员介绍DUT→验证人员讲述对DUT的理解

验证策略

按照透明度划分:

黑盒/灰盒/白盒验证

黑盒:规避看过DUT后,功能实现方法造成的错误;操作容易,但出错定位麻烦

按照层次化划分:

模块/子系统/系统验证

验证方法

动态仿真:利用EDA工具加激励(验证工作)

- 定向测试

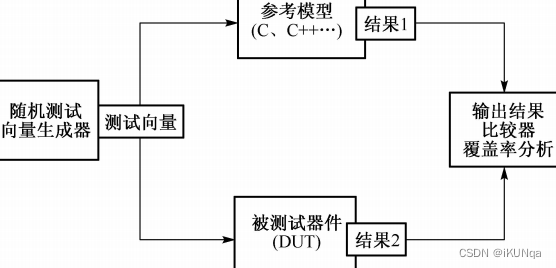

- 随机测试(CRT约束随机测试)

- 基于事物级的验证(TLM Transaction level model)

- 基于coverage的验证(case pass后,最后收集vdb文件,会耗时)

- 断言检查(主要用于设计时序的检查,握手信号)

静态检查

- Linting语义检查(工具:Spyglass)

- 跨时钟域检查(工具:Spyglass)

- 形式验证(后端工作,等价和属性检查,一种形式转换为另一种形式)

硬件加速

- FPGA验证

- emulator专用模拟器(速度快,价格高)

基于事物级的验证TLM

BFM:将高抽象级的TLM命令转换为低抽象级的硬件接口时序

验证点提取

读Spec重点关注点:协议/系统框架图/接口信号/寄存器文件

验证点分类:

- 功能类(时钟,复位,power,寄存器访问,基本功能等)

- 白盒测试点

- 接口类

- 场景类

- 性能类

- 异常类

验证平台

验证执行

冒烟测试(smoke test)

根据验证计划,写测试用例(Testcase)

调试debug

- 验证环境/Case的问题

- 设计的问题

回归测试(regression):重复以前的全部或部分的相同功能测试用例

需要考虑的因素:回归流程、回归质量、回归效率

覆盖率检查

后仿真

前仿真:RTL级

后仿真:Netlist级+SDF(standard delay format)

SDF文件中包含延迟信息、时序检查、时序约束

动态时序分析:时间、占用资源很大

静态时序分析:STA,后端实现

综合后网表仿真:零时延仿真

布局布线后仿真:有延迟信息

异步fifo

fifo基本概念

宽度/深度;写指针/读指针;写数据端口/读数据端口;FIFO空/FIFO满;

同步FIFO/异步FIFO

写指针:指向下一次将要写入的数据的位置

读指针:指向当前要读出的数据的位置

空标志:当读指针和写指针相等时,空标志=1(读指针追上写指针)

满标志:当写指针和读指针相等时,满标志=1(写指针追上读指针)

异步复位,同步释放:是否和clk上升沿同步

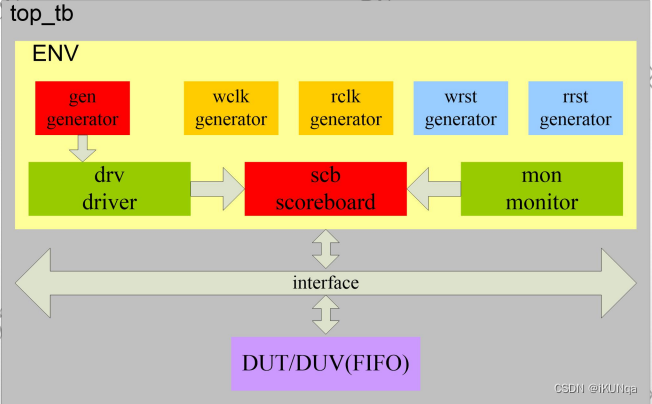

验证环境搭建

① 建立项目目录:rtl,sim,svtb

② rtl下是设计人员的dut代码

③ svtb下

-

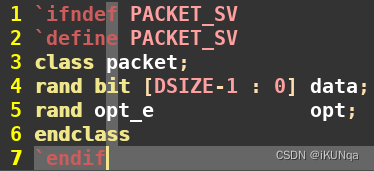

建立packet.sv

-

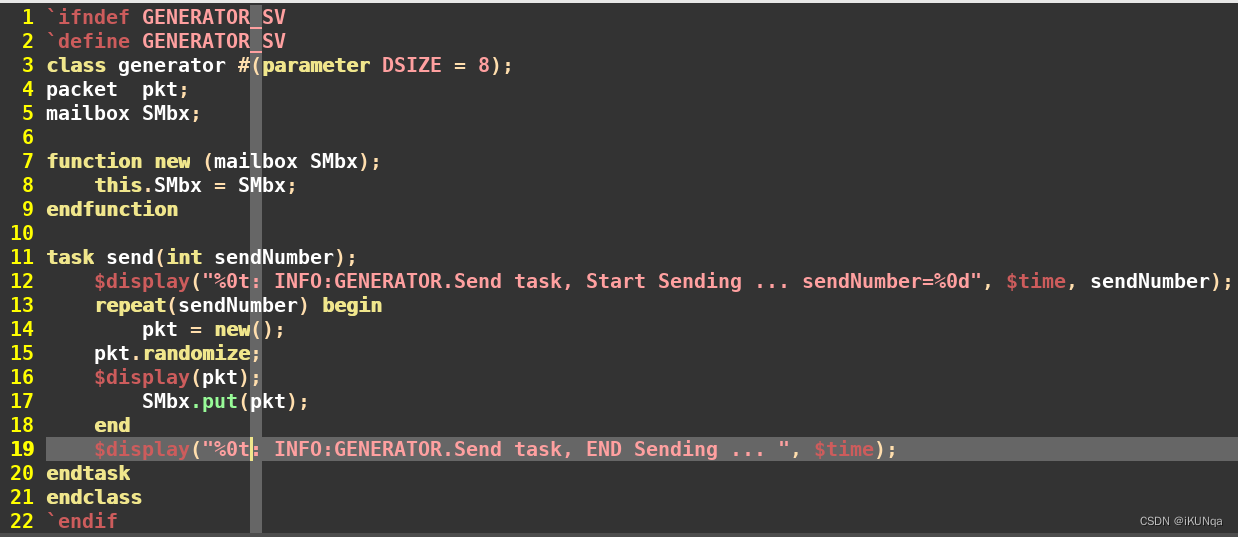

建立generator.sv

-

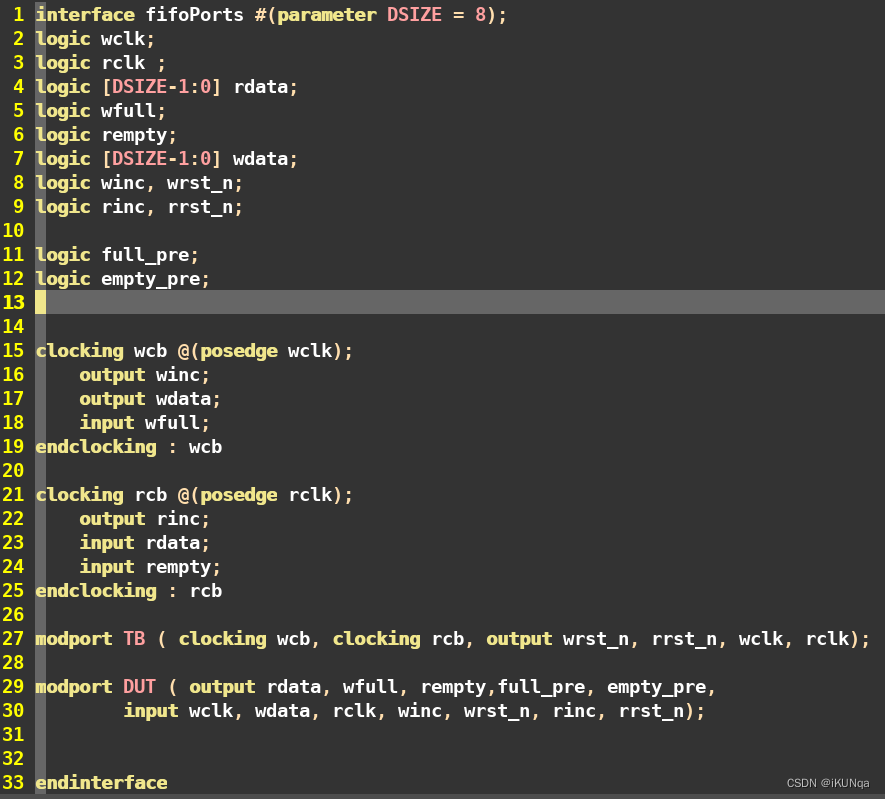

建立interface.sv(interface)

-

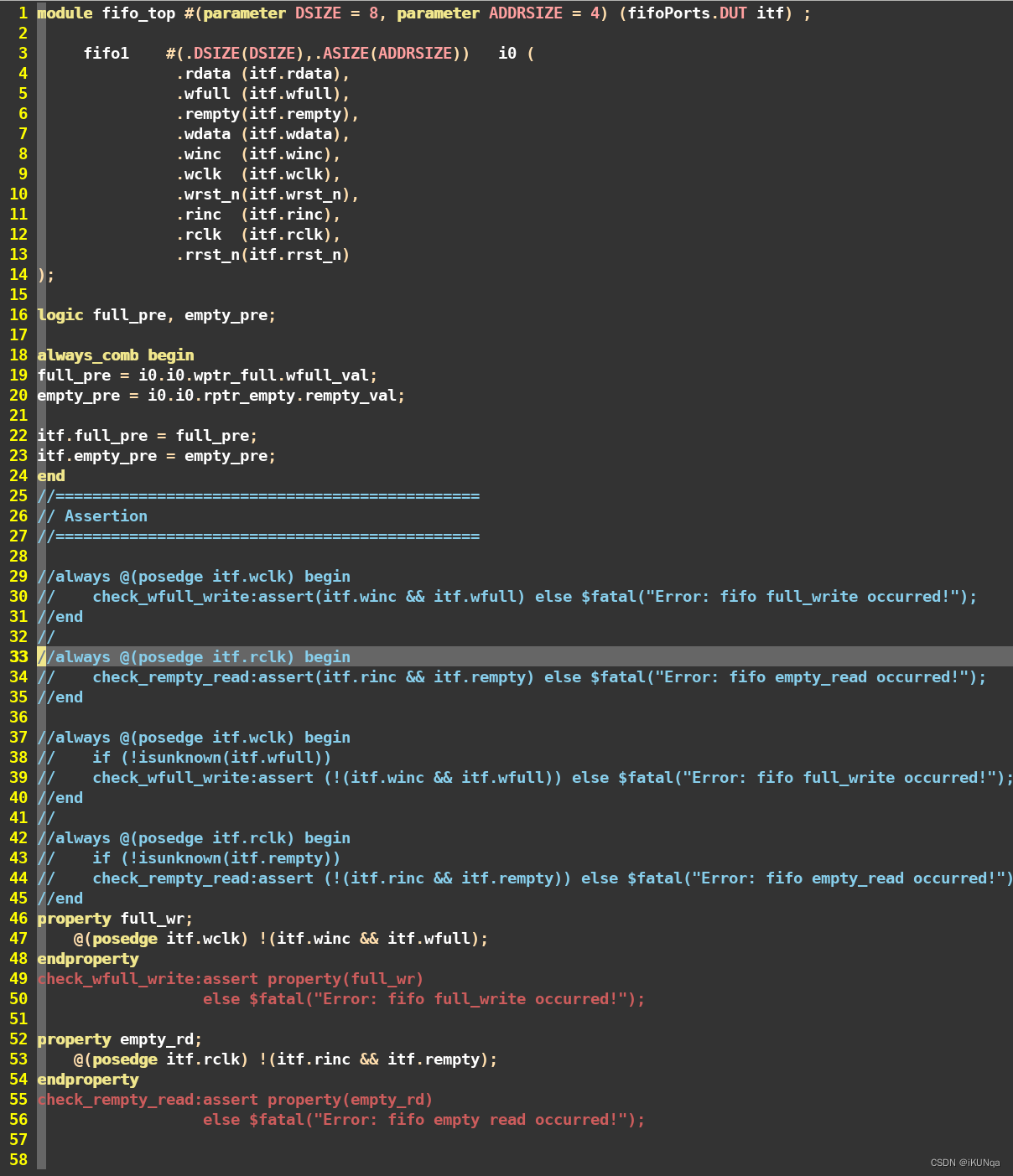

建立fifo_top:使用interface连接DUT(module)

-

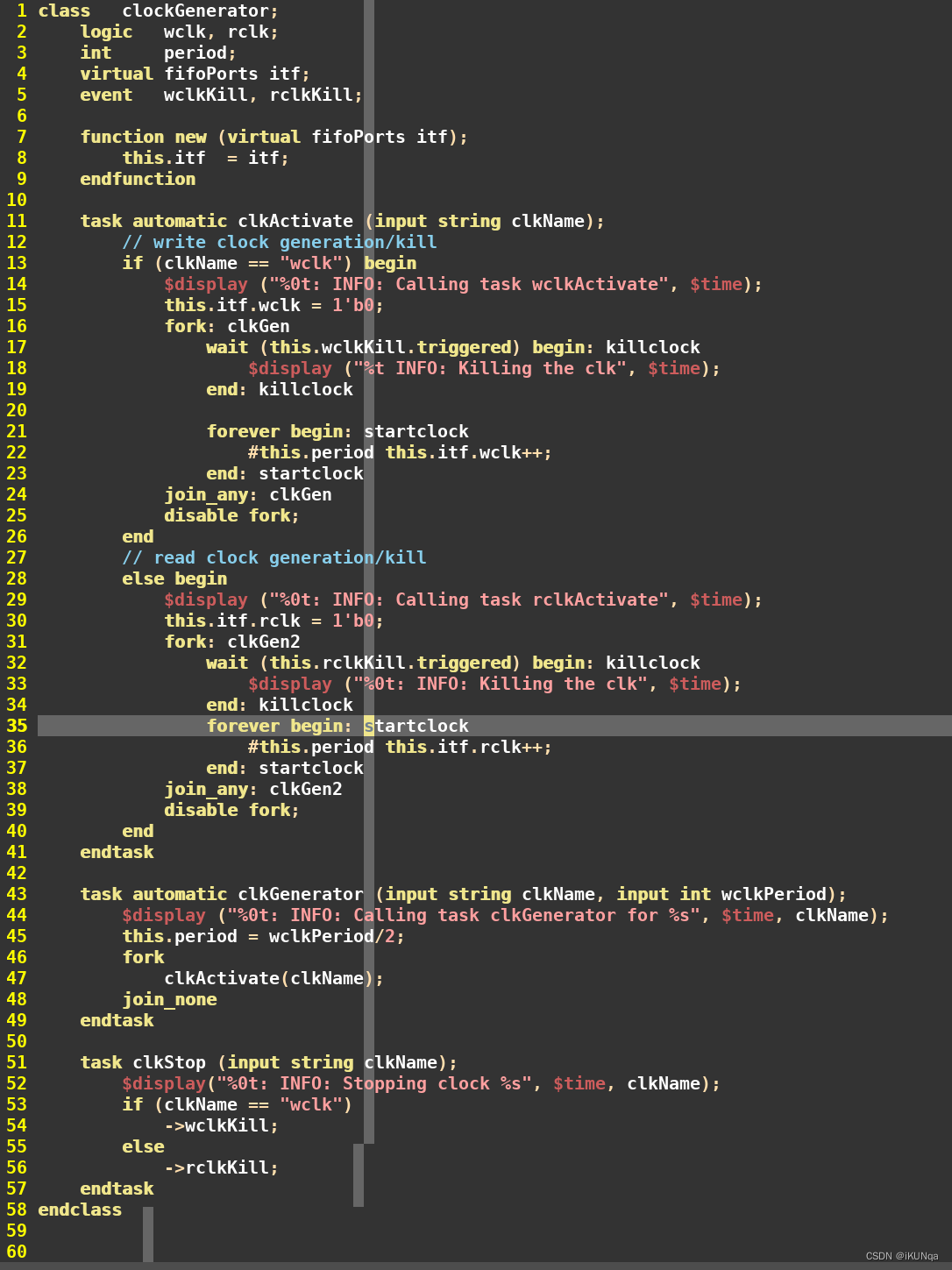

建立clockGener(class)(最好放在module中,便于debug)

-

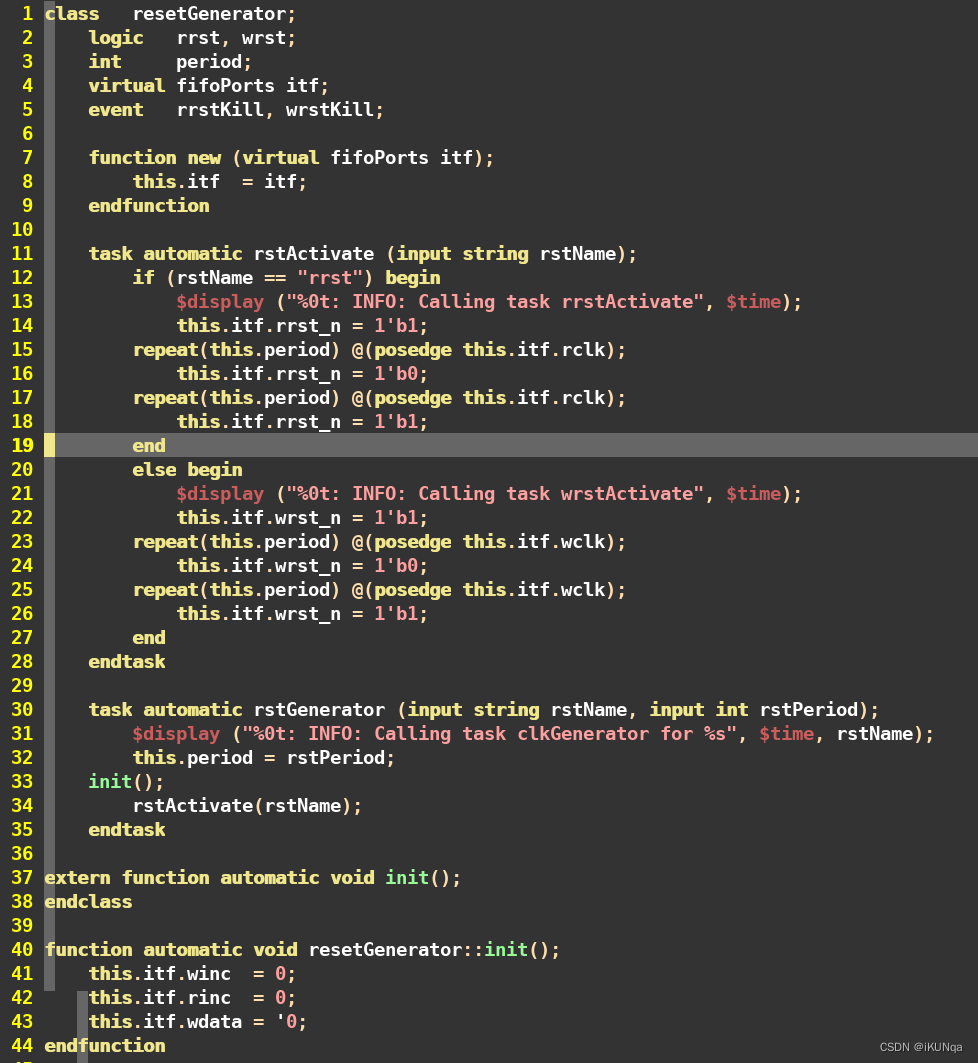

建立resetGenerator(class)

-

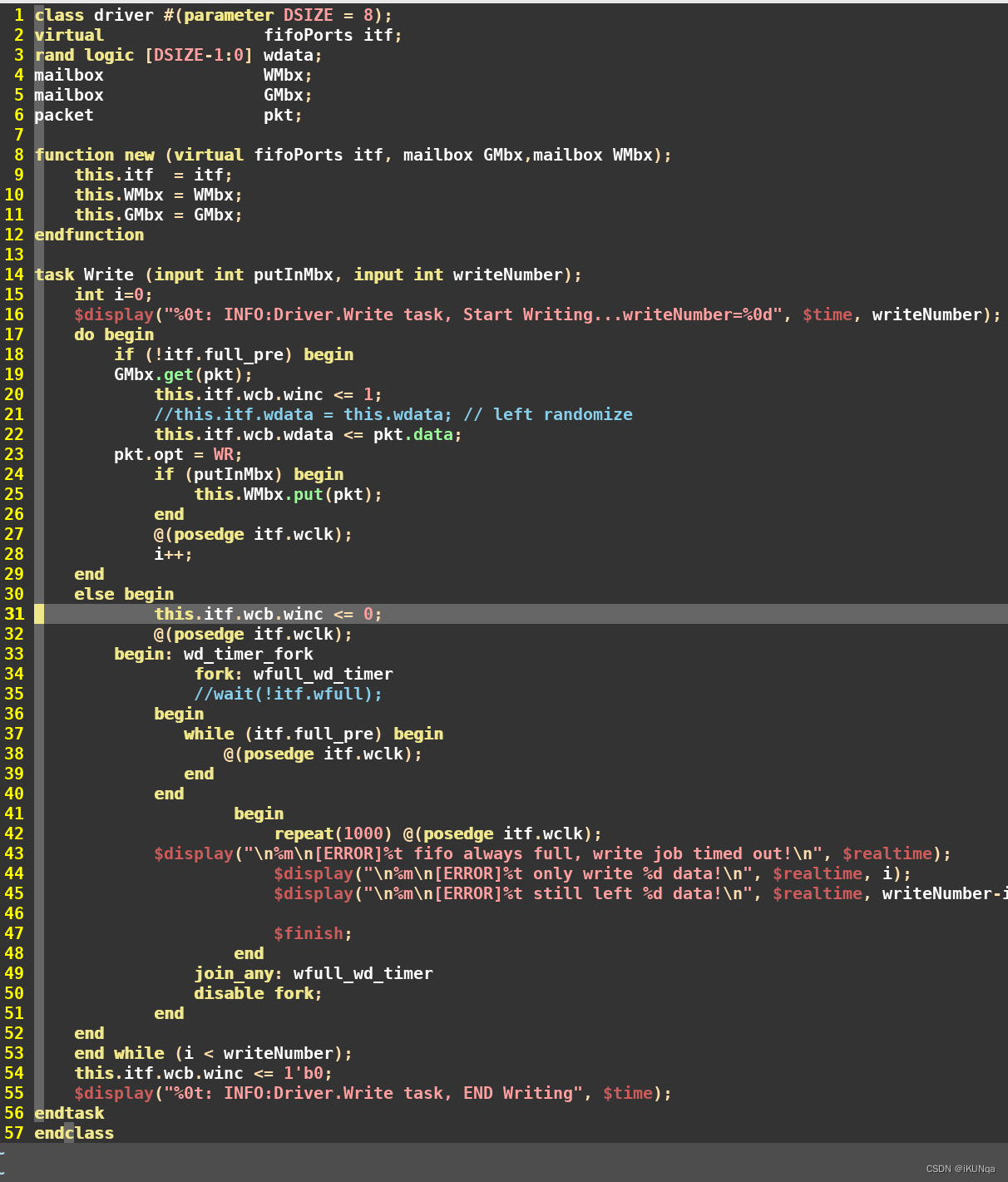

建立driver:给dut灌激励(class)

驱动一定要用非阻塞赋值,驱动给DUT,DUT使用非阻塞赋值

类中不能定义实接口,定义虚接口

-

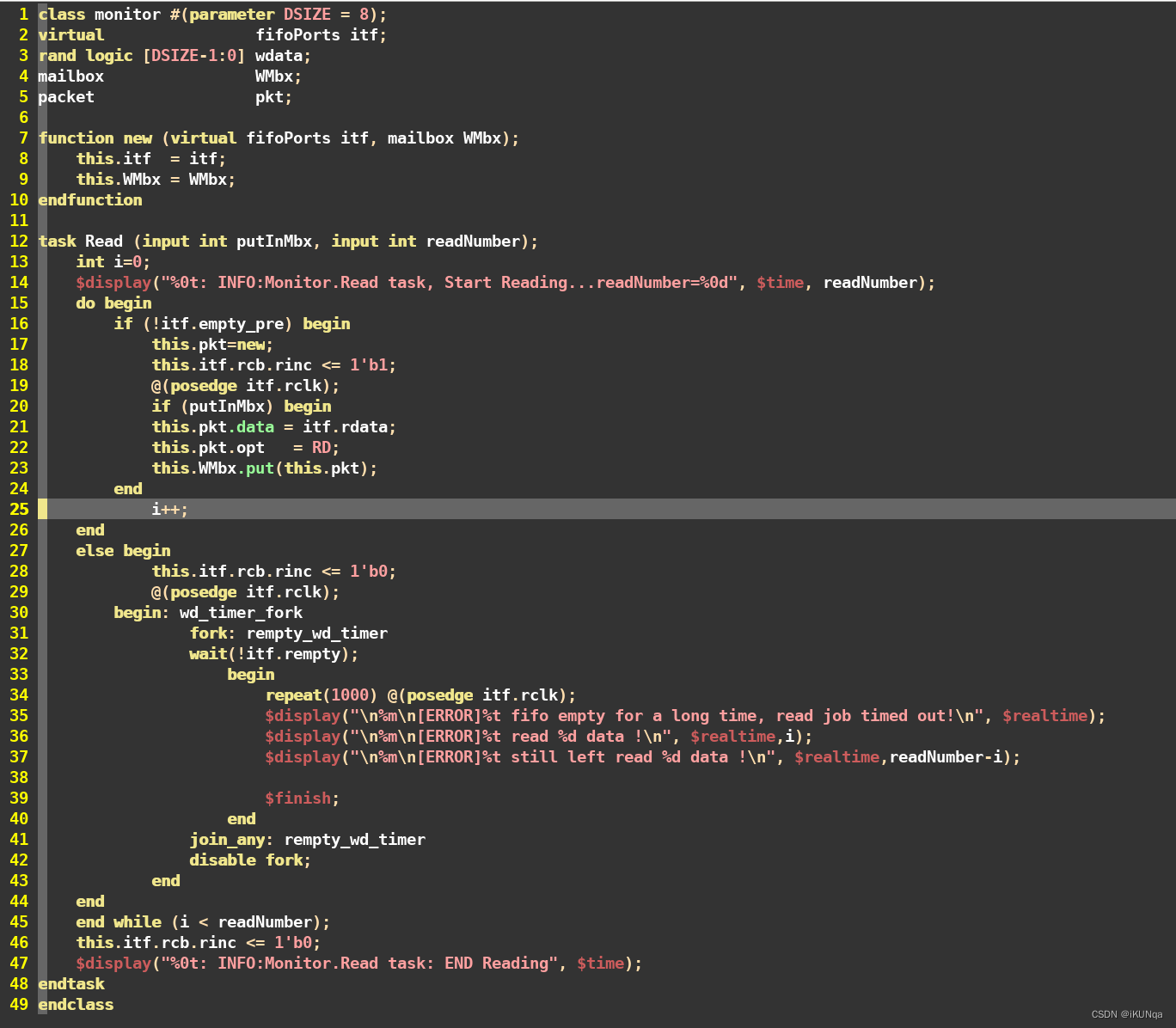

建立monitor:抓输出数据(class)

monitor只是拿数据,阻塞赋值

-

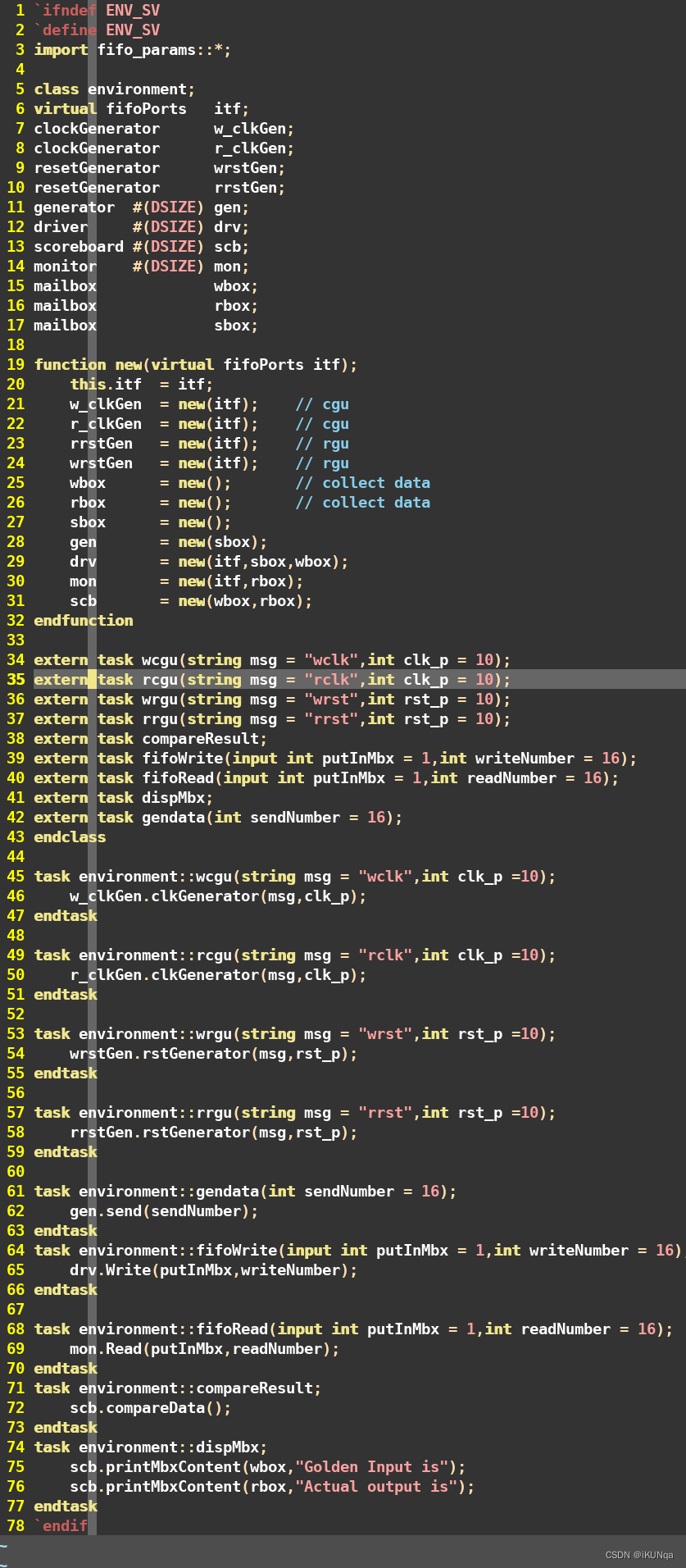

建立environment(class)

例化clockGener、resetGenerator、driver、monitor

-

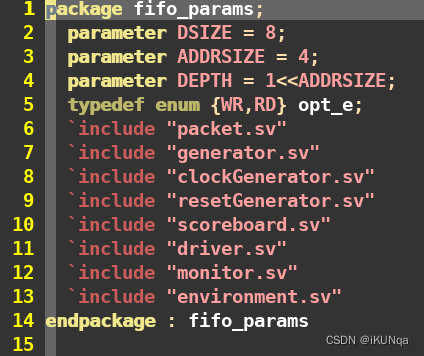

建立fifo_params(package)

-

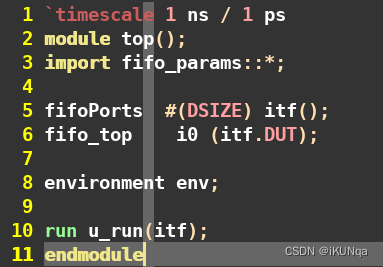

建立top.sv

例化接口,environment,调用environment中例化类的方法

-

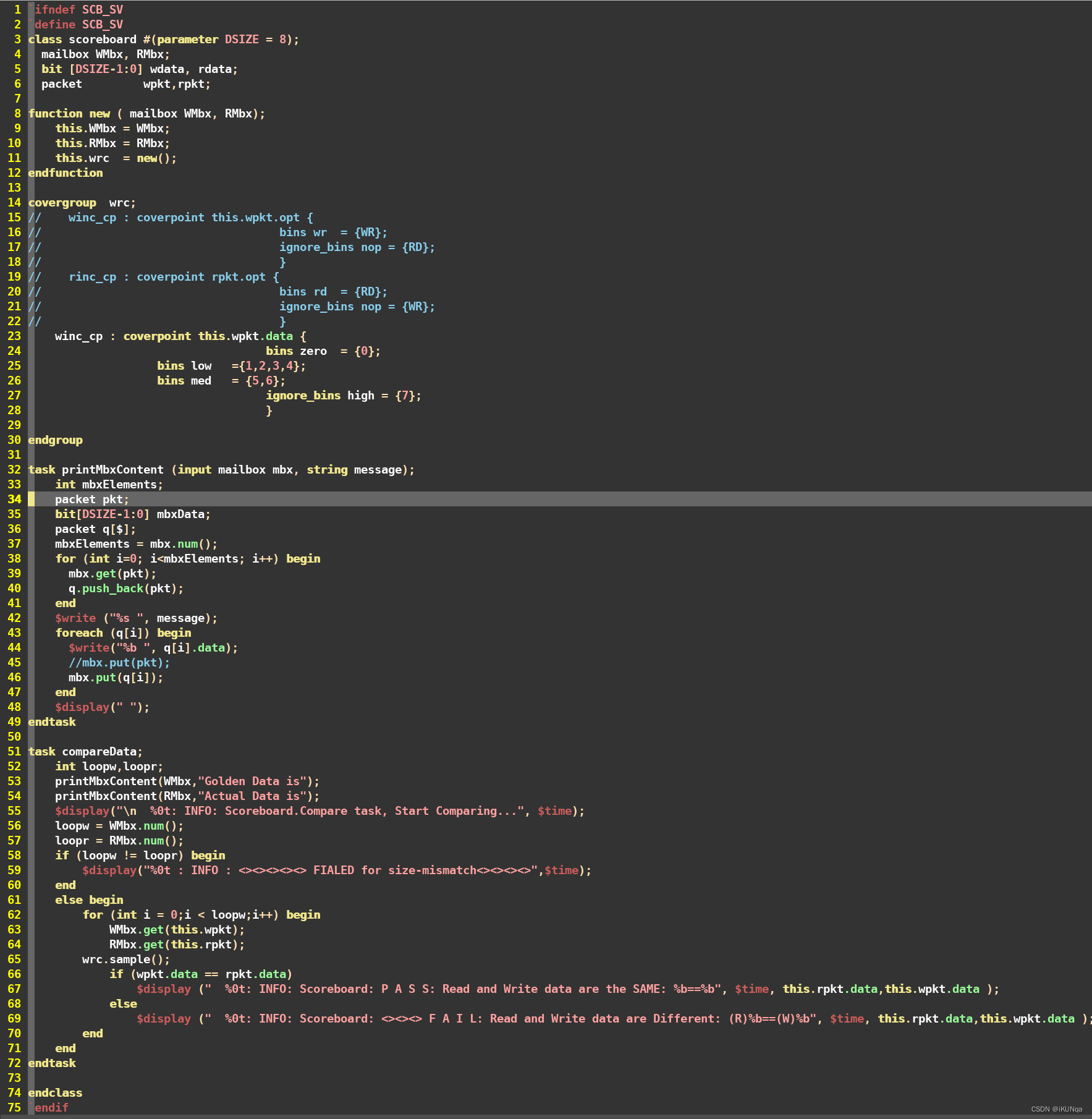

建立scoreboard.sv

队列放package

scoreboard中建立covergroup

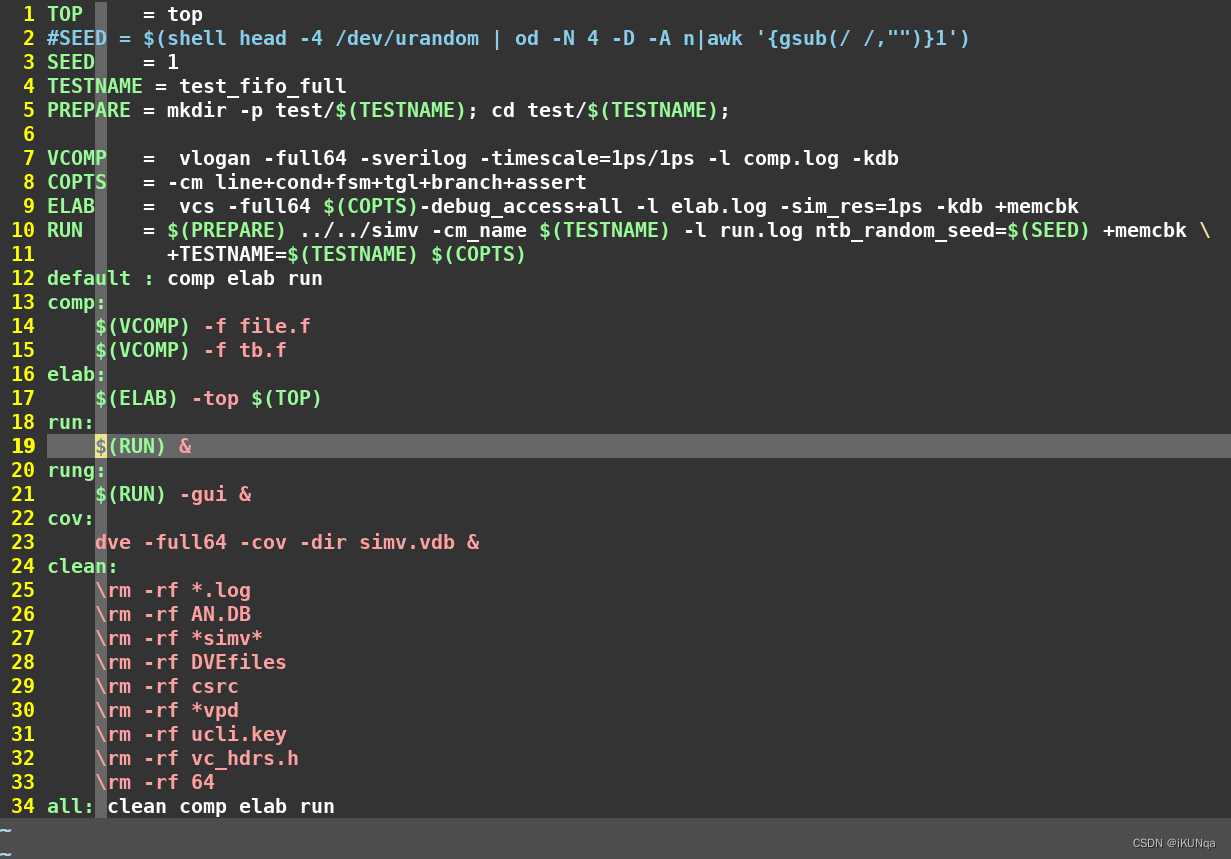

④ sim下Makefile中说明顶层文件的名称

TOP = top

2113

2113

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?