event pool

uvm_event

用于同步或者通信,由object派生

->:trigger event

@:wait event

wait_trigger();//相同时间触发与等待,不一定能等到该事件

wait_ptrigger();//一定能等到该事件,在while循环中会造成一直触发

uvm_pool

共享的内存空间,单例模式,由object派生,少用

class apb_driver extends uvm_driver#(apb_trans);

……

uvm_pool #(string,int) drv_pool;

virtual protected task run_phase(uvm_phase phase);

super.run_phase(phase);

drv_pool=drv_pool.get_global_pool();

drv_pool.add("aa",10);

drv_pool.add("bb",01);

……

endclass

class vseq_0 extends base_v_sequence;

uvm_pool #(string,int) seq_pool;

virtual task body();

string s_key;

seq_pool=seq_pool.get_global_pool(); `uvm_info("seq",$sformatf("seq_pool.aa=%d",seq_pool.get("aa")),UVM_LOW);//seq_pool.aa=10

seq_pool_delete("bb");

seq_pool_add("cc");

seq_pool_first(s_key);

`uvm_info("seq",$sformatf("seq_pool.first_key=%s",s_key),UVM_LOW);//seq_pool.first_key=aa

seq_pool_last(s_key);

`uvm_info("seq",$sformatf("seq_pool.last_key=%s",s_key),UVM_LOW);seq_pool.first_key=cc

s_key="aa";

seq_pool_next(s_key);

`uvm_info("seq",$sformatf("seq_pool.next_key=%s",s_key),UVM_LOW);//seq_pool.next_key=cc

endclass

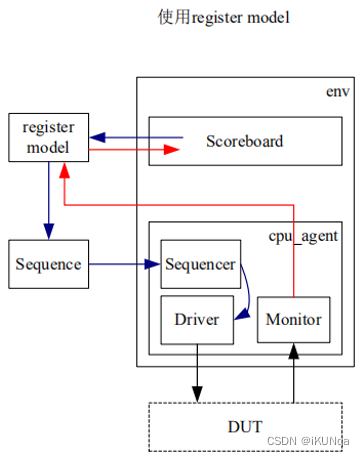

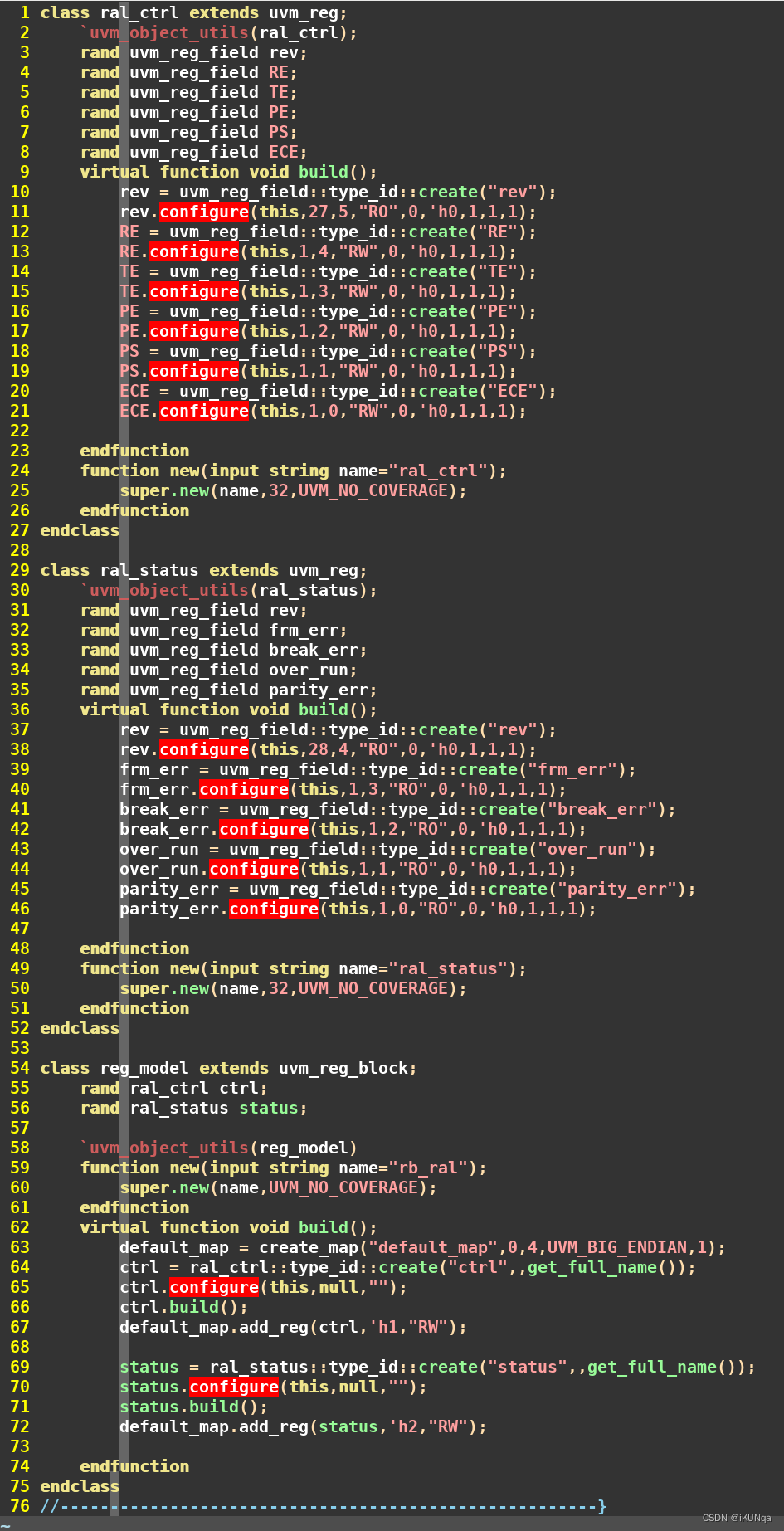

RAL

register abstraction layer:DUT里的配置模式

UVM寄存器的本质:重新定义了验证平台与DUT的寄存器接口

uvm_reg_field<uvm_reg<uvm_reg_block,一个register model至少包含一个uvm_reg_block

寄存器地址:uvm_reg_map

前门访问(FRONTDOOR):通过总线上发出的读写操作访问DUT的寄存器,消耗仿真时间

后门访问(BACKDOOR):直接通过hdl_path层次化的引用来改变寄存器的值或获取寄存器的值,不消耗仿真时间

可在任何耗费时间的phase中使用寄存器模型以前门访问(FRONTDOOR)或后门访问(BACKDOOR)的方式来读取寄存器的值

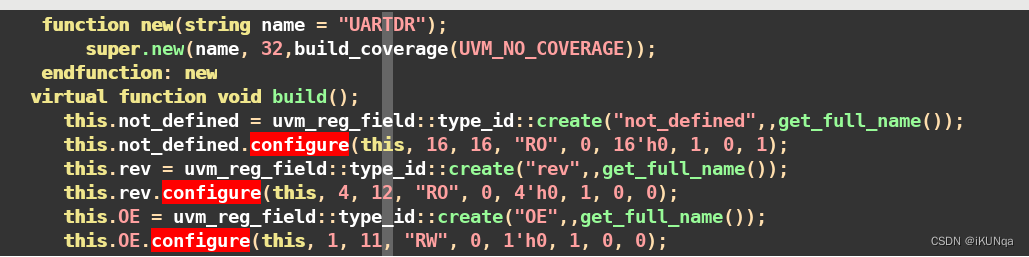

configure(此域的parent,宽度,此域最低位在整个寄存器中的位置,此域的访问方式,是否易失一般不用,上电复位后的默认值,是否有复位,是否可以随机化,是否可以单独访问)

寄存器的实现

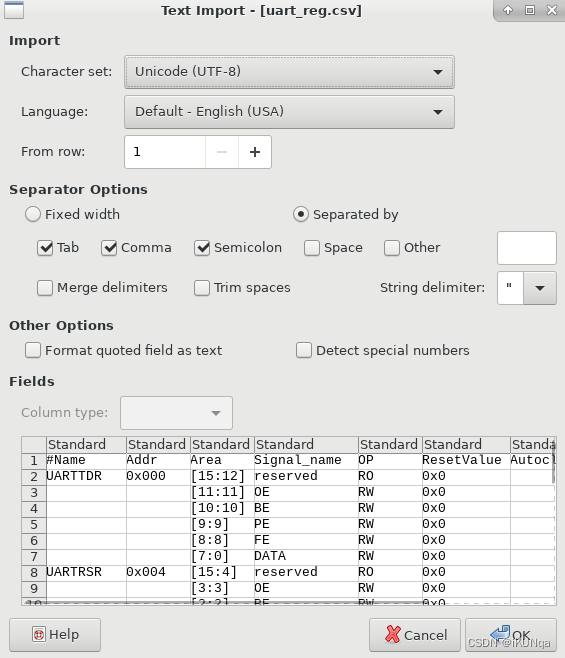

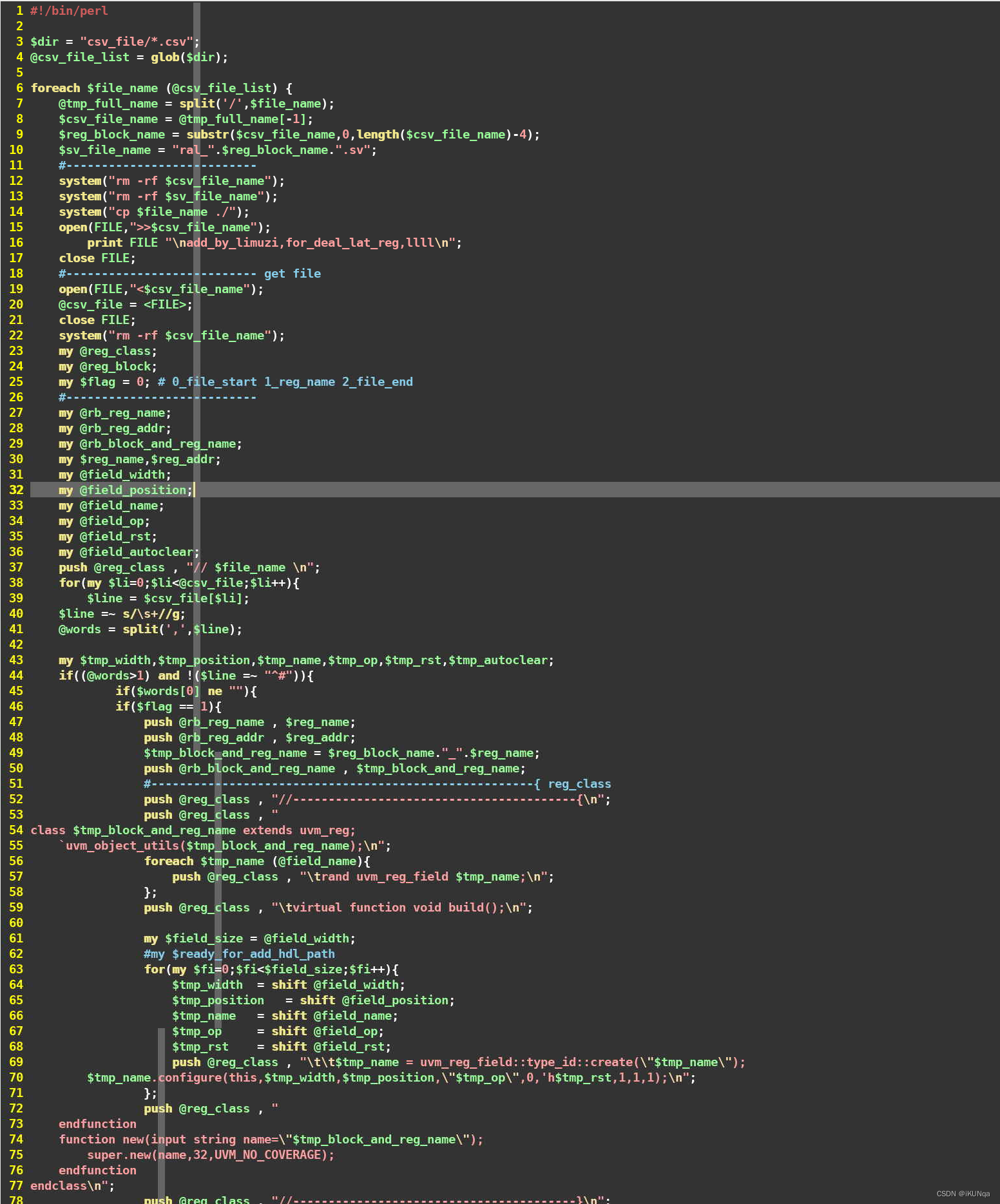

文件夹里mkdir csv_file和gen_ral.pl,csv_file文件夹里存放.csv文件

soffice uart_reg.csv可打开如下界面

perl gen_ral.pl命令生成寄存器,复制到reg_model中,把主class类名改为reg_model:

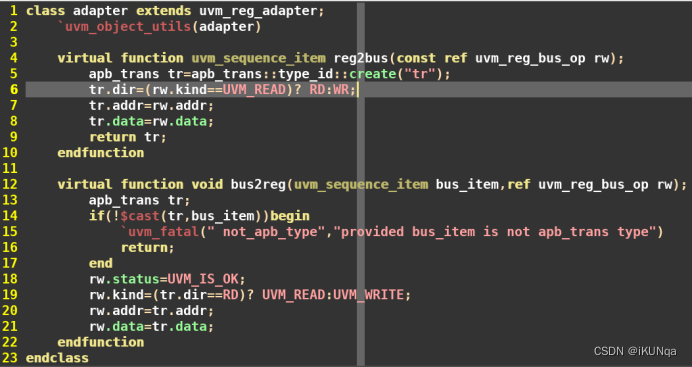

REG2BUS: 把reg model通过sequence发出的uvm_reg_bus_op型的变量转换为cpu_sequencer能够接受的形式。

BUS2REG:当监测到总线上有操作的时候,把收集来的transaction转换成reg model能够接受的形式,以便reg model能够更新相应的寄存器的值:

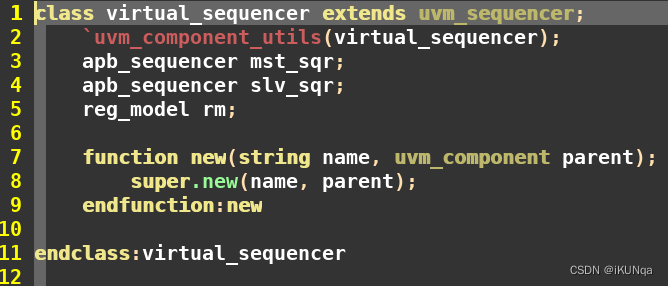

vqr中实例化reg_model:

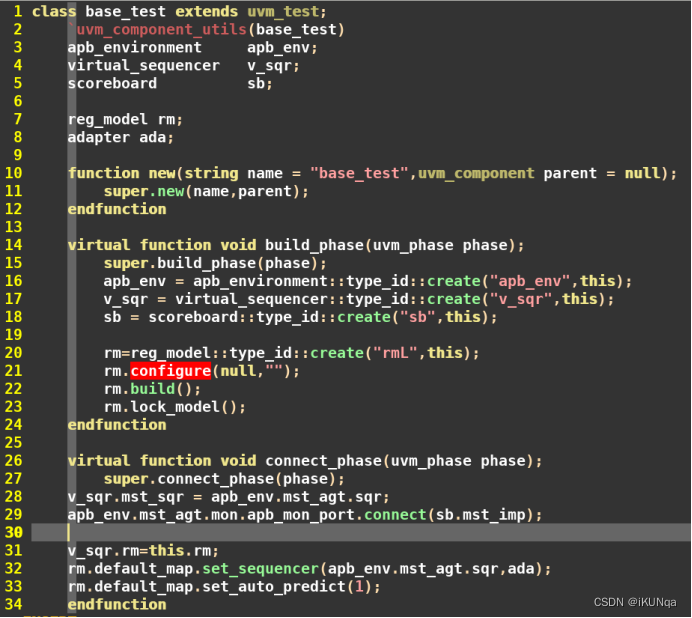

base_test中创建与连接:

TLM(事物级建模)

UVM提供的一组事务级别的通信接口和通道。可用于在事物级连接组件,如monitor和scoreboard的连接

initiator:通信请求的发起方

target:通信请求的响应方

producer、consumer(数据流)

producer:生产数据方

consumer:接收数据方

通信端口——port、export、imp

port:通信请求方initiator的发起端,initiator凭借port端口才可以访问target

export:作为initiator和target中间层次的端口(可有可无)

imp:只能作为target接收请求的响应端,它无法作为中间层次的端口,所以imp的连接无法再次延伸

优先级:port > export > imp,使用connect()建立连接关系时,只有优先级高的才能调用connect()做连接,即port可以连接port、export或者imp;export可以连接export或者imp

imp只能作为数据传送的终点,无法扩展连接。若port、export作为终点会报错

sequence_item_export源码类型为imp

三种端口不是uvm_component的子类,应该使用new()函数在build_phase中创建。(注意:不能用create创建,端口不属于UVM树的一部分)

put/get //单向传输

trans_port //双向传输,相当于一次put加一次get

uvm_analysis_port(export) //跨层次传输,广播通信,可与多个imp相连,有write方法,用的少

通信管道——TLM FIFO

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?