7.随机的时间间隔

前面介绍了如何应用系统任务$random产生随机数据。本节讨论在测试平台中采用随机时间作为输入x赋值语句中的延迟。

如下面描述的测试平台,其中用到$random产生延迟控制,对前面的1101序列检测器进行测试。测试平台中,命名为running的initial语句为电路产生适当的reset和start信号。在这个过程块中,由非阻塞赋值语句生成的时间延迟被作为绝对的时刻值。

/*************************************************************************/

//采用随机时间间隔的测试平台

module test_moore_detector;

reg x,start,reset,clock;

wire z;

reg [3:0] t;

Moore_detector MUT(x,start,reset,clock,z);

initial

begin:running

clock <= 1'b0; x <=1'b0;

reset <= 1'b1; reset <= #17 1'b0;

start <= 1'b0; start <= #17 1'b1;

repeat(13)

begin

@(posedge clock);

@(negedge clock);

end

start = 1'b0;

#5;

$stop;

end

always #5 clock=~clock;

always

begin

t=$random;

#(t) x=$random;

end

endmodule

/*************************************************************************/

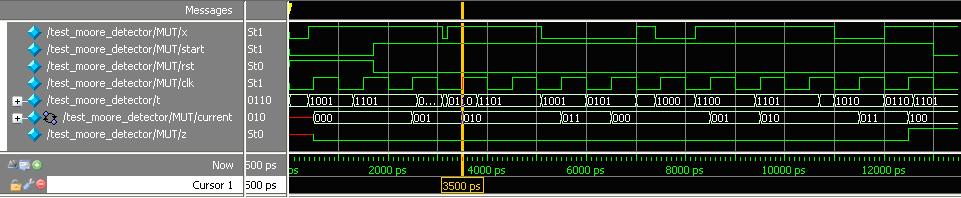

状态机开始工作后,测试平台等待13个完整的时钟周期,然后对输入start信号赋0值,停止仿真。和running语句块并发的一个always块生成周期为10ns的时钟信号,另一个always块生成随机的时间t,并把t作为向x赋随机值时的延迟,这个always块不停地为输入x信号产生数据,直到running块中执行到$finish才停止。仿真波形如下图所示。

8.数据缓存的应用

迄今为止我们讨论的测试平台都不是送给电路的特定激励数据。下面要讨论一种利用缓存器保存数据并将其送给待测模块的测试平台。我们采用一组预先定义的比特序列,并将其作为moore_detector的输入信号x。

在测试平台里,一个19比特的寄存器变量buffer储存了对moore_detector模块的测试数据。用一个always语句在每个时钟(clk)上升沿的1ns后,把这个缓存里的数据逐位移进moore_detector的输入信号x。移位时,buffer是循环移位的,这样就保证缓存的数据可以重复使用。另一个initial块用于产生状态机的开始和结束控制信号。测试平台描述如下。

/*************************************************************************/

//使用缓存数据的测试平台

module test_moore_detector;

reg x=0,rst,start,clk=0;

wire z;

reg [18:0] buffer;

Moore_detector MUT(x,start,rst,clk,z);

initial buffer = 19'b0001101101111001001;

initial

begin

rst=1'b1;start=1'b0;

#29 rst=1'b0;

#29 start=1'b1;

#500 $stop;

end

always @(posedge clk) #1 {x,buffer}={buffer,x};

always #5 clk=~clk;

endmodule

/*************************************************************************/

采用这种测试平台能确保为待测模块输入一个正确的序列,这样就能很容易地检查预期的输出结果。一般来说,如果花费较多的精力来产生测试数据,分析结果就会比较容易。如果能容易地生成随机或者伪随机的测试数据,其后果则是需要花费大量的时间分析输出结果。

886

886

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?