一 、 实 验 目 的

掌 握 静 态 随 机 存 取 存 储 器 RAM工 作 特 性 及 数 据 的 读 写 方 法 。

二 、 实 验 内 容

1 、 实 验 原 理

主存储器单元电路主要用于存放实验机的机器指令,如图3—5所示,它的数据总线挂在外 部数据总线EXD0~EXD7上; 它的地址总线由地址寄存器单元电路中的地址寄存器74LS273(U37) 给出,地址值由8个LED灯LAD0~LAD7显示,高电平亮,低电平灭; 在 手 动 方 式 下 ,输 入 数 据 由 8位 数 据 开 关 KD0 ~ KD 7 提 供 ,并 经 一 三 态 门 74LS245( U5 1 )连 至 外 部 数 据 总 线 EXD0 ~ EXD 7,实 验 时 将 外 部 数 据 总 线 EXD0 ~ EXD 7 用 8芯 排 线 连 到 内 部 数 据 总 线 BUSD0 ~ BUSD7 , 分 时 给 出 地 址 和 数 据 。 它的读信号直接接地; 它的写信 号和片选信号由写入方式确定。该存储器中机器指令的读写分手动和自动两种方式。手动方式 下 ,写信号由W/R` 提供,片选信号由CE`提供; 自动方式下,写信号由控制CPU的P1.2提供, 片选信号由控制CPU的P1.1提供。

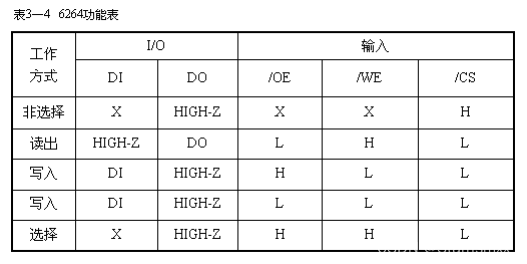

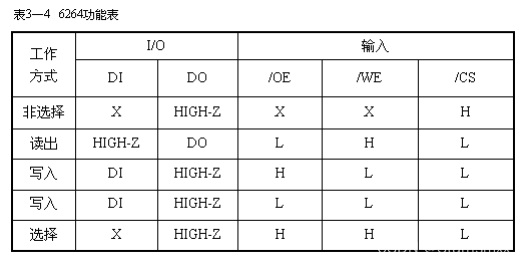

由 于 地 址 寄 存 器 为 8位 , 故 接 入 6264 的 地 址 为 A0 ~ A7 , 而 高 4位 A8 ~ A 12

接 地 , 所 以 其 实 际 使 用 容 量 为 256字 节 。 6264有 四 个 控 制 线 : CS 1 第 一

片 选 线 、 CS2第 二 片 选 线 、 OE读 线 、 WE 写 线 。 其 功 能 如 表 3 — 4所 示 。 CS 1 片 选 线 由 CE `控 制 ( 对 应 开 关 CE ) 、 OE读 线 直 接 接 地 、 WE 写 线 由W/R `控 制 ( 对 应 开 关 WE ) 、 CS2 直 接 接 +5V。

图 中 信 号 线 LDAR 由 开 关 LDAR提 供 ,手 动 方 式 实 验 时 ,跳 线 器 LDAR 拨 在 左 边 , 脉 冲 信 号 T3 由 实 验 机 上 时 序 电 路 模 块 TS 3提 供 , 实 验 时 只 需 将 J22 跳 线 器 连 上 即 可 , T3 的 脉 冲 宽 度 可 调 。

2 、 实 验 接 线

1 、J20,J21,J22,接上短路片,

2 、J23,J24 ,J25 ,J26 接左边;

3 、J27,J28 右边;

4 、JA5 置“接通”;

5 、JA6 置“手动”;

6 、JA1,JA2,JA3,JA4 置“高阻”;

7 、JA8 置上面“微地址”

8 、EXJ1 接 BUS3

3 、 实 验 步 骤

⑴ 连 接 实 验 线 路 , 仔 细 查 线 无 误 后 接 通 电 源 。

⑵ 形 成 时 钟 脉 冲 信 号 T3 , 方 法 如 下 : 总 清 开 关 置 “ 1 ” , 在 时 序 电 路

模 块 中 有 两 个 二 进 制 开 关 “ 运 行 控 制 ” 和 “ 运 行 方 式 ” 。 将 “ 运 行 控 制 ”

开 关 置 为 “ 运 行 ”状 态 、 “ 运 行 方 式 ”开 关 置 为 “ 连 续 ”状 态 时 , 按 动 “ 运

行 启 动 ” 开 关 , 则 T3有 连 续 的 方 波 信 号 输 出 , 此 时 调 节 电 位 器 W 1 , 用 示 波

器 观 察 , 使 T3输 出 实 验 要 求 的 脉 冲 信 号 ; 本 实 验 中 , “ 总 清 ”开 关 置 “ 1 ”,

“ 运 行 方 式 ” 开 关 置 为 “ 单 步 ” 状 态 , 每 按 动 一 次 “ 启 动 运 行 ” 开 关 , 则

T3输 出 一 个 正 单 脉 冲 , 其 脉 冲 宽 度 与 连 续 方 式 相 同 。

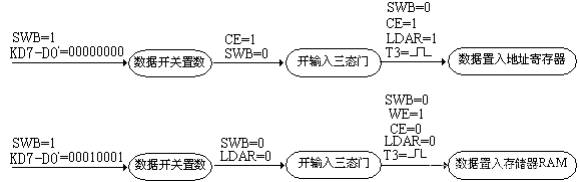

⑷ 给 存 储 器 的 00地 址 单 元 中 写 入 数 据 1 1 , 具 体 操 作 步 骤 如 下 :

如 果 要 对 其 它 地 址 单 元 写 入 内 容 , 方 法 同 上 , 只 是 输 入 的 地 址 和 内 容 不 同 。

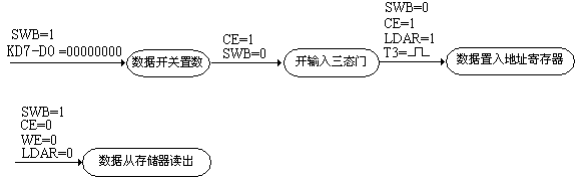

⑸ 读 出 刚 才 写 入 00地 址 单 元 的 内 容 , 观 察 内 容 是 否 与 写 入 的 一 致 。

具 体 操 作 步 骤 如 下 :

接线:

1 、J20,J21,J22,接上短路片,

2 、J23,J24 ,J25 ,J26 接左边;

3 、J27,J28 右边;

4 、JA5 置“接通”;

5 、JA6 置“手动”;

6 、JA1,JA2,JA3,JA4 置“高阻”;

7 、JA8 置上面“微地址”

8 、EXJ1 接 BUS3

实验一:33H存入地址22H

- 连接实验线路。

- “总清"开关置“1",“运行方式"开关置为“单步”状态,每按动一次“启动运行”开关。(形成时钟脉冲信号T3)

3、数据置入地址RAM

(1)数据开关置数:SWB=1,KD7-KD0=00100010

- 开输入三态门:CE=1,SWB=0

- 数据置入地址寄存器:SWB=0,CE=1,LDAR=1,按T3

(数据已经置入地址寄存器)

(4)数据开关置数:LDAR=0,SWB=1,KD0-KD7=00110011

(5)开输入三态门:SWB=0,LDAR=0

(6)数据置入存储器:RAM:SWB=0,WE=0,CE=0,LDAR=0,按T3

4、验证

- 数据开关置数:SWB=1,KD7-KD0=00100010

- 开输入三态门:CE=1,SWB=0

- 数据置入地址寄存器:SWB=0,CE=1,LDAR=1,按T3

- 数据从存储器读出:SWB=1,CE=0,WE=0,LDAR=0

实验一结果:总线数据显示是00110011,总线地址显示是00100010,即存入地址为22H的数据为33H,与预期相同。

实验二:00H数据读出,存入44H,并检验(数据为88H)

- 存数:方法同实验一的3步,存入88H(10001000)

- 读出来:

(1)数据开关置数:SWB=1,KD7-KD0=00000000

(2)开输入三态门:CE=1,SWB=0

(3)数据置入地址寄存器:SWB=0,CE=1,LDAR=1,按T3

(4)数据从存储器读出:SWB=1,CE=0,WE=0,LDAR=0

- 存DR1:

- 存入DR1:ALUB=1,LDDR1=1,LDDR2=0,按T4

- 存地址:方法同实验一的1,2和3中的(1)(2)(3)步,

- 存数入44H

- 数据读入总线:LDAR=0,SWB=1,ALUB=0,S1 S2 S3 S4 =11111

- 数据存入存储器:SWB=0,WE=0,CE=0,LDAR=0,按T3

- 验证:同。

实验二结果:

总线地址显示是01000100,而总线数据显示是10001000,即存入地址为44H的数据为22H,与预期相同。

结论:

数据需要一个中介从一个存储器转另一个存储器。

本文详细描述了一个实验,旨在了解静态RAM的工作原理,包括实验原理、接线、步骤,以及手动和自动数据读写的操作过程。通过实际操作演示了如何在6264存储器中进行数据的存取,强调了数据在存储器间转移的必要性。

本文详细描述了一个实验,旨在了解静态RAM的工作原理,包括实验原理、接线、步骤,以及手动和自动数据读写的操作过程。通过实际操作演示了如何在6264存储器中进行数据的存取,强调了数据在存储器间转移的必要性。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?