SSD主要由两大模块构成---主控和闪存介质。另外可选的还有Cache缓存单元。主控是SSD的大脑,承担着指挥、运算和协调的作用,具体表现在:

- 前端实现标准主机接口与主机通信,接口包括SATA、SAS、PCIe等。

- 中间层SSD固件运行FTL(Flash Translation Layer)算法。

- 后端实现与闪存的通信,主要包含数据编解码和ECC。

一款主控芯片的好坏直接决定了SSD的性能、寿命和可靠性。

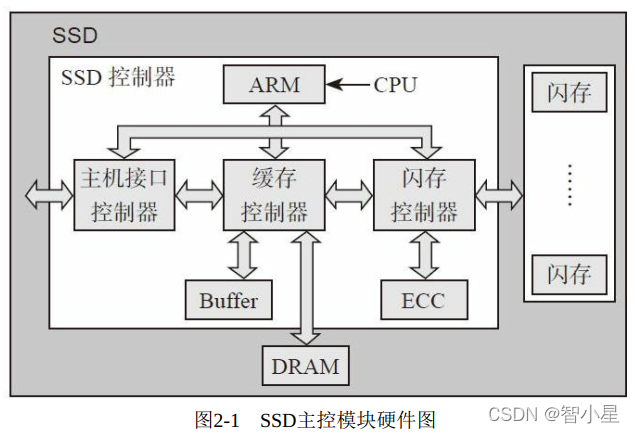

SSD作为数据存储设备, 其实是一种典型的(System on Chip) 单机系统, 有主控CPU、 RAM、 操作加速器、 总线、 数据编码译码等模块(见图2-1) , 操作对象为协议、 数据命令、 介质, 操作目的是写入和读取用户数据。

1.前端

前端是负责主机和SSD设备通信的接口, 命令和数据传输通过前端总线流向或流出SSD设备。

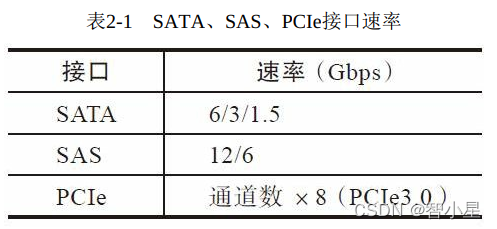

主机接口:与主机进行通信(数据交互)的标准协议接口,当前主流的接口为SATA、SAS和PCIe等。三者的接口速率如下。

SATA的全称是Serial Advanced Technology Attachment(串行高级技术附件),是一种基于行业标准的串行硬件驱动接口,是由Intel、IBM、Dell、APT、Maxtor和Seagate公司共同提出的硬盘接口规范 。

SAS(Serial Attached SCSI)即串行连接 SCSI,是新一代的SCSI技术,和现在流行的SATA硬盘相同,都是采用串行技术以获得更高的传输速度,并通过缩短连接线改善内部空间等。SAS是并行SCSI接口之后开发出的全新接口,此接口的设计是为了改善存储系统的效能、可用性和扩充性,并且提供与SATA硬盘的兼容性。SAS接口技术可以向下兼容SATA。

具体来说, 二者的兼容性主要体现在物理层和协议层。 在物理层, SAS接口和SATA接口完全兼容, SATA硬盘可以直接用在SAS的环境中; 从接口标准上而言, SATA是SAS的一个子标准, 因此SAS控制器可以直接操控SATA硬盘, 但是SAS却不能直接用在SATA的环境中, 因为SATA控制器并不能对SAS硬盘进行控制。

PCIe(Peripheral Component Interconnect Express)是一种高速串行计算机扩展总线标准,它原来的名称为3GIO,是由英特尔在2001年提出来的,旨在替代旧的PCI、PCI-X和AGP总线标准。PCIe属于高速串行点对点多通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽。

主要支持主动电源管理、 错误报告、 端对端的可靠性传输、 热插拔以及服务质量(QoS, Quality of Service) 等功能。 它的主要优势就是数据传输速率高, 目前最高的4.0版本可达到2GB/s(单向单通道速率) , 而且还有相当大的发展潜力。 PCI Express也有多种规格, 从PCI

Express 1X到PCI Express 32X, 意思就是1个通道到32个通道, 能满足将来一段时间内出现的低速设备和高速设备的需求。 PCI-Express最新的接口是PCIe 4.0接口。

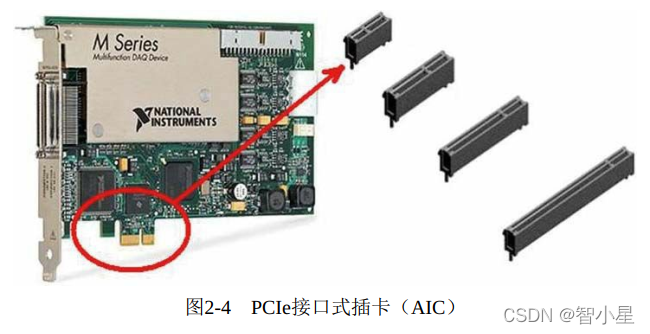

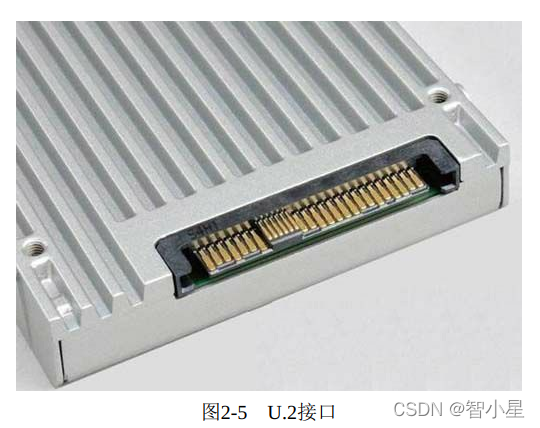

图2-4和图2-5展示的是PCIe接口, 分别为卡式和U.2。

2.主控CPU

SSD控制器SoC模块和其他嵌入式系统SoC模块并没有本质的不同,一般由一颗或多颗CPU核组成,同时片上有I-RAM、D-RAM、PLL、IO、UART、高低速总线等外围电路模块。CPU负责运算、系统调度,IO完成必要的输入输出,总线连接前后端模块。

SSD所说的固件就运行在CPU核上。如果是多核CPU,软件开发分为2类多核处理:

对称多核处理(SMP):

对称多处理多核共享OS和同一份执行代码,共享一份I-RAM和D-RAM,资源共享。

非对称多核处理(AMP):

非对称多处理多核分别执行不同的代码,没核对应一份I-RAM和D-RAM独立运行,没有内存抢占导致代码速度执行变慢的问题。

当SSD的CPU要求计算能力更高时,除了增加核数和单核CPU频率外,AMP的设计方式更加适应计算和任务独立的要求,消除了代码和数据资源抢占导致执行速度过慢的问题。

固件会根据CPU的核数进行设计,充分发挥多核CPU的计算能力是固件设计考虑的一方面。另外固件会考虑任务划分,会将任务分别加载到不同CPU上执行,在达到并行处理的同时让所有CPU有着合理且均衡的负载,目标是让SSD输出最大的读写性能。

SSD的CPU外围模块还包括UART、GPIO、JTAG这些都是程序必不可少的调试端口,其内部资源和我们了解的MCU差不多。

- 国外主流的主控厂商:Marvell、三星

- 国内主流的主控厂商:智微(JMicron)、慧荣(Silicon Motion)、群联(Phison)、联芸(Maxio)。

3.后端

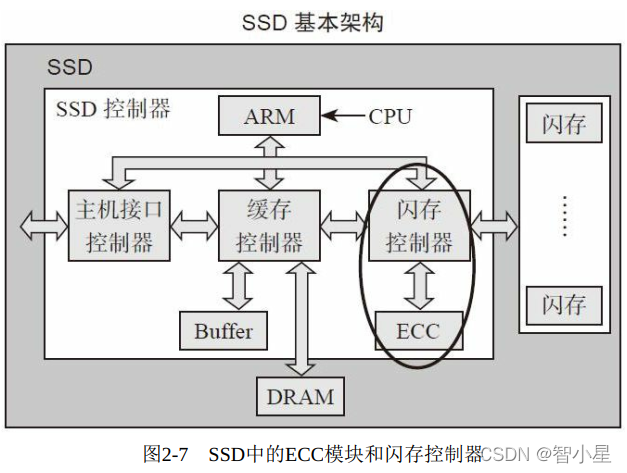

后端两大模块分别为ECC模块和闪存控制器。

ECC模块是数据编解码单元,由于闪存存储天生存在误码率,为了数据的正确性,在数据写入操作时应给原数据加入ECC校验保护,这是一个编码过程。读取数据时,同样需要通过解码来检错和纠错,如果错误的比特数超过ECC纠错能力,数据会以“不可纠错”的形式上传给主机。 这里的ECC编码和解码的过程就是由ECC模块单元来完成的,SSD内的ECC算法主要有BCH和LDPC,其中LDPC正逐渐成为主流。

闪存控制器使用符合闪存ONFI、 Toggle标准的闪存命令, 负责管理数据从缓存到闪存的读取和写入。

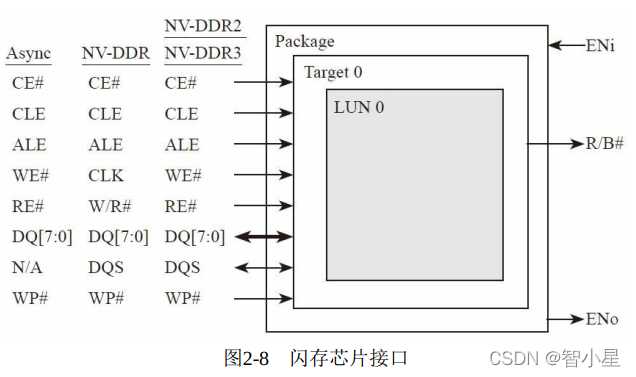

闪存控制器如何实现与闪存连接和通信?从单个闪存角度看,一个Die/LUN是一个闪存命令执行的基本单元,闪存控制器和闪存连接引脚如下图所示:

从闪存控制器角度看,为了性能需求需要并发多个闪存Die/LUN,通常配置有多个通道。一个通道挂多少个Die/LUN,取决于性能需求,个数越多并发性能越好。一个通道上的Die/LUN共用一套总线,通过CE#引脚来进行片选通信。一个通道上可以有多个CE,SSD主控一般设计4~8个,对于容量而言有一定的灵活度。

985

985

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?