| 信号名 | 方向 | 功能描述 |

|---|---|---|

| CK_t,CK_c | Input | 差分时钟输入。所有的地址、控制信号都是通过CK_t的上升沿与CK_c的下降沿进行采样的 |

| CKE | Input | 时钟使能:CKE为高电平时,启动内部时钟信号、设备输入缓冲以及输出驱动单元。CKE低电平时则关闭上述单元。当CKE为低电平时,可使设备进入PRECHARGE POWER DOWN、SELF-REFRESH以及ACTIVE POWER DOWN模式。CKE与SELF REFRESH退出命令是同步的。在上电以及初始化序列过程中,VREFCA与VREF将变得稳定,并且在后续所有的操作过程中都要保持稳定,包括SELF REFRESH过程中。CKE必须在读写操作中保持稳定的高电平。在POWER DOWN过程中,除CK_t,CK_c,ODT以及CKE以外的所有输入缓冲都是关闭的。在SELF REFRESH过程中,除CKE以外的所有输入缓冲都是关闭的。在正时钟上升边沿采样。 |

| CS_n | Input | 片选信号:当CS_n锁存为高电平时,所有的命令都被忽略。在正时钟上升边沿采样。 |

| CA_n | Input | 命令/地址输入信号。可作为地址线使用,也可作为命令代码使用,是命令代码的一部分。 |

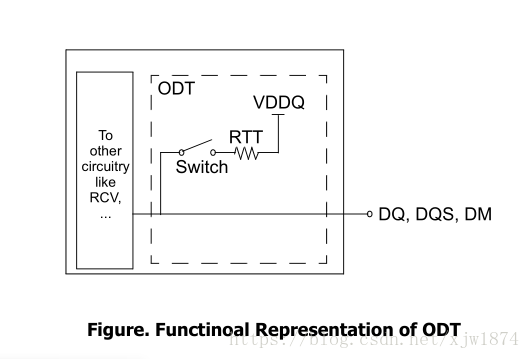

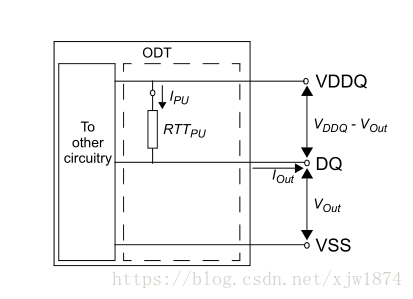

| ODT | Input | On-Die Termination,片上终端电阻:ODT信号可使能DDR SDRAM内部的RTT_NOM终端电阻。该设计通过允许DRAM控制器独立地打开/关闭任一或所有DRAM设备的终端电阻来改善存储器通道的信号完整性。 DRAM通过ODT控制引脚为每个DQ,DQS_t及DQS_c和DM开启/关闭终端电阻。与其他输入命令不同,ODT引脚直接控制ODT动作,不对其进行时钟采样。 请注意,如果在掉电模式下启用ODT,则在掉电期间可能无法关闭VDDQ(I/O供电),同时DRAM也会在读操作期间无法关闭。 基本结构见表下图。 |

| DM_n | Input | 输入数据掩码:DM_n信号是作为写数据的掩码信号,当DM_n信号为低电平时,写命令的输入数据对应的位将被丢弃。DM_n在DQS的两个条边沿都采样。 |

| DQ | Input\Output | 数据输入、输出:双向数据总线。若模式寄存器中使能了CRC功能,那么在数据burst结束时就会附加一段CRC码。 |

| DQS_t,DQS_c | Input\Output | 差分数据选通信号:差分信号对,作输入时与写数据同时有效,作输出时与读数据同时有效。读数据时与边沿对齐,但是跳变沿位于写数据的中心。DDR4 SDRAM仅支持选通信号为差分信号,不支持单根信号的数据选通信号。 |

| NC | 无电气连接。 | |

| VDDQ | Supply | I/O供电:1.2V +/- 0.06V |

| VSSQ | Supply | I/O地 |

| VDD | Supply | Core供电:1.2V +/- 0.06V |

| VDDCA | Supply | CA供电 |

| VSSCA | Supply | CA地 |

| VSS | Supply | Core地 |

| VPP | Supply | DRAM激活供电:2.5V(最小2.375V,最大2.75V) |

| VREF | Supply | 参考电压 |

| ZQ | Supply | Drive Strength Calibration校准参考电阻 |

(1)ODT结构

6021

6021

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?