一、SPI简介

1.1SPI总线

SPl(Serial Peripheral lnterface)是串行外设接口的缩写,SPI是一种高速的、全双工、同步的串行通信总线。

速度比IIC和串口快,但是比USB和网口慢。

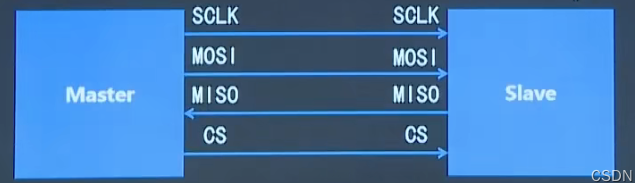

SPI采用主从方式工作,一般有一个主设备和一个或多个从设备。

SPI需要至少4根线,分别是MIS0(主设备输入|从设备输出)、MOSI(主设备输出|从设备输入)、SCLK(时钟)、CS(片选)。

SPI使用引脚较少且布线方便,所以越来越多的芯片集成了这种通信协议。

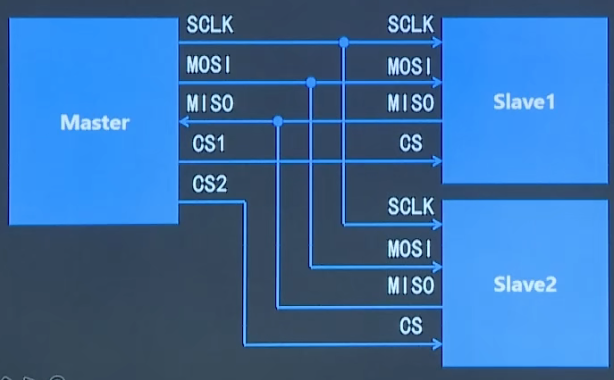

SPI和IIC都允许一条总线上挂跟多设备,一般从机是四根线,主机最少四根线(因为可能有多个从机),每个从机都要对应一个片选线。

IIC允许有多个主机,有仲裁机制,SPI一般只有一个主机,仲裁机制差一些。

1.2寻址方式

当主设备要和某个从设备进行通信时,主设备需要先向对应从设备的片选线上发送使能信号(高电平或者低电平,根据从机而定)表示选中该从设备。

cs表示高电平有效,是低电平有效。

例如:主机要和Slave2通信,片选线低电平有效。

则:cs1=1,cs2=0。

1.3通信过程

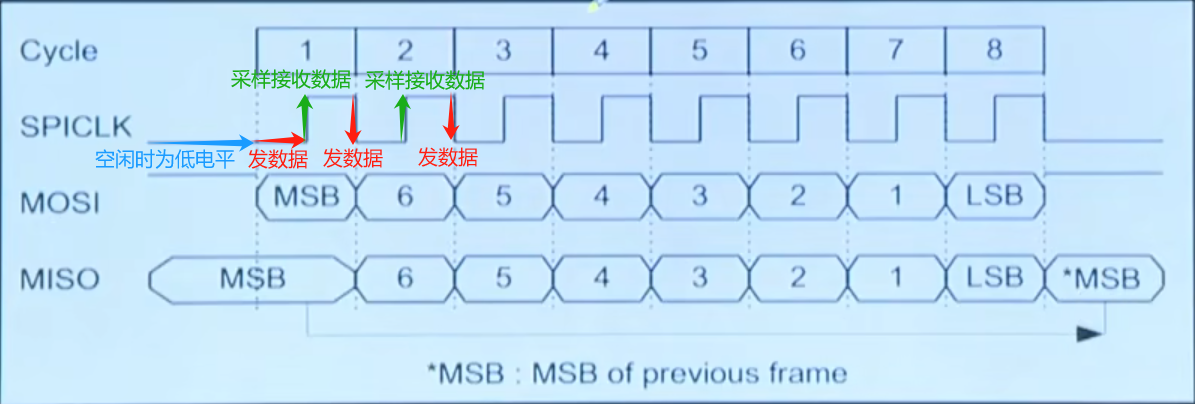

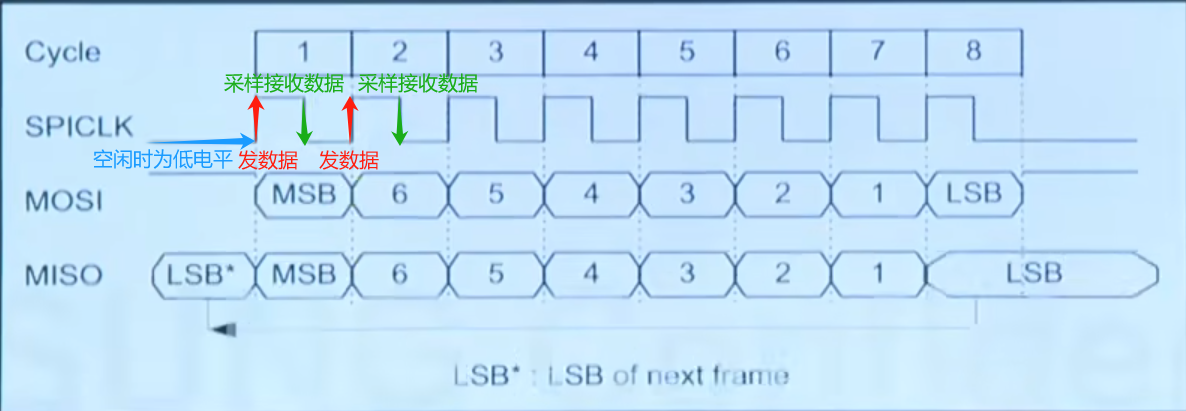

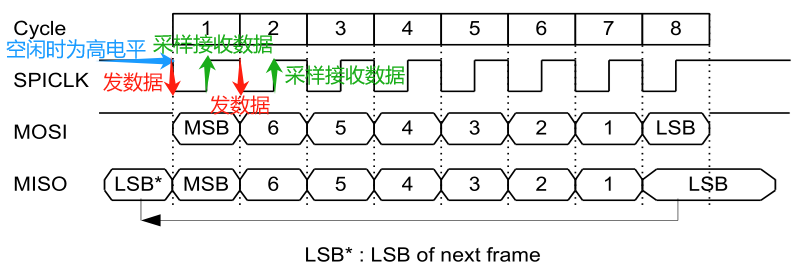

SPI总线在进行数据传送时,先传送高位,后传送低位(和IIC一样),如下图MSB表示最高位,LSB表示最低位;

数据线为高电平表示逻辑'1’,低电平表示逻辑'0’;

一个字节传送完成后无需应答即可开始下一个字节的传送;

SPI没有开始信号,没有结束信号,没有应答,直接发完一个字节发下一个字节;

SPI总线采用同步方式工作,时钟线在下降沿(或上升沿)时发送器向数据线上发送数据,在紧接着的上升沿时(或下降沿)接收器从数据线上读取数据(第一位数据有细微差别),完成一位数据传送,八个时钟周期即可完成一个字节数据的传送.

1.4极性和相位

SPI总线有四种不同的工作模式,取决于极性(CPOL)和相位(CPHL)。

CPOL表示SCLK空闲时的状态

- CPOL=0,空闲时SCLK为低电平

- CPOL=1,空闲时SCLK为高电平

CPHA表示采样时刻

- CPHA=0,每个周期的第一个时钟沿采样

- CPHA=1,每个周期的第二个时钟沿采样

1.4.1CPOL=0,CPHA=0

空闲时SCLK为低电平,(低→高)每个周期的第一个时钟沿采样(采样就是接收数据)。

1.4.2CPOL=0,CPHA=1

空闲时SCLK为低电平,(低→高→低)每个周期的第二个时钟沿采样(采样就是接收数据)。

1.4.3CPOL=1,CPHA=0

空闲时SCLK为高电平,(高→低)每个周期的第一个时钟沿采样(采样就是接收数据)。

1.4.4CPOL=1,CPHA=1

空闲时SCLK为高电平,(高→低→高)每个周期的第二个时钟沿采样(采样就是接收数据)。

1.4.5其他说明

对于一个特定的从设备来说,一般在出厂时就会将其设计为某种特定的工作模式。在使用该设备时就必须保证主设备的工作模式和该从设备保持一致,否是无法进行通信的则。

所以一般是根据从设备的数据手册对主设备的CPOL和CPHA进行配置。

二、IIC与SPI的对比

| IIC | SPI | |

| 相同点 | 均采用串行、同步的方式 均采用TTL电平,所以传输距离不会太长和应用场景类似 均采用主从方式工作 | |

| 不同点 | IIC半双工 | SPI全双工 |

| IIC有应答机制 | SPI无应答机制 | |

| IIC较低速 | SPI较高速 | |

| IIC通过向总线广播从机地址来寻址(通信慢但是主机占用引脚少) | SPI通过向对应从机发送使能信号来寻址(通信快但是主机占用引脚多) | |

| IIC的时钟极性和时钟相位固定 | SPI的时钟极性和时钟相位可调 | |

其中,TTL电平:简单用高电平表示1,低电平表示0。

IIC节省硬件资源,SPI节省时间。

4647

4647

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?