- 新建SSC文件,参考EtherCAT Slave Desi Quick Guide 和 《ETG2000_S_R_V1i0i6_EtherCATSlaveInformationSpecification.pdf》

- SSC配置参考博主博文SSC从站

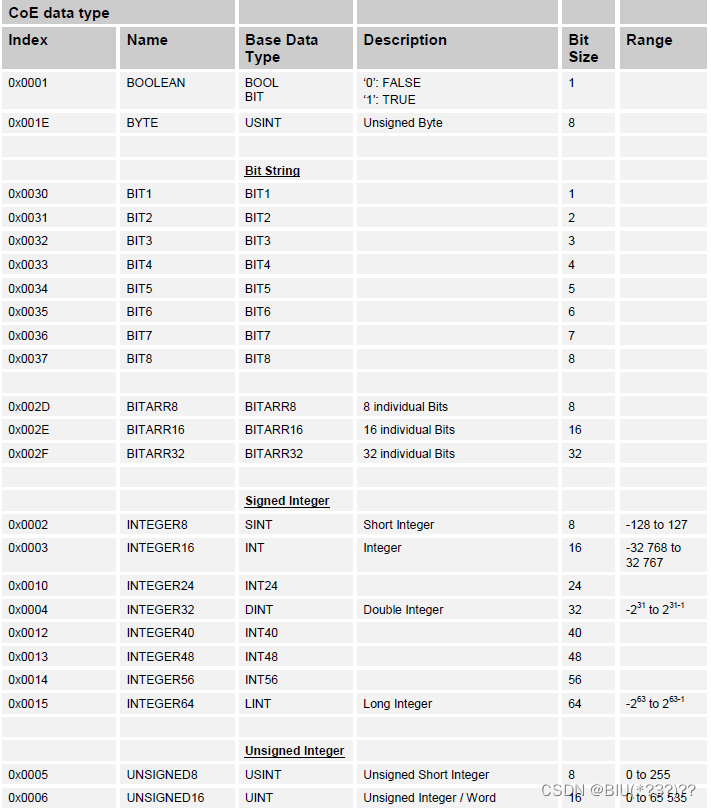

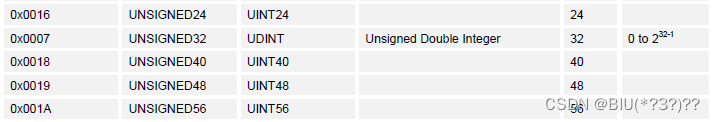

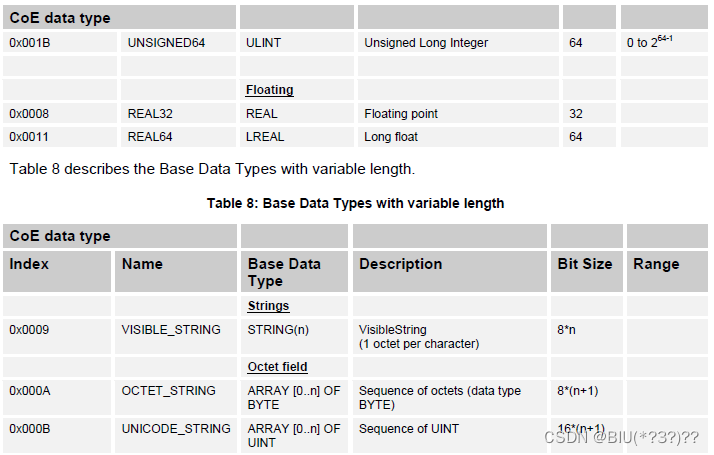

- EtherCAT基本数据类型

SSC生成代码

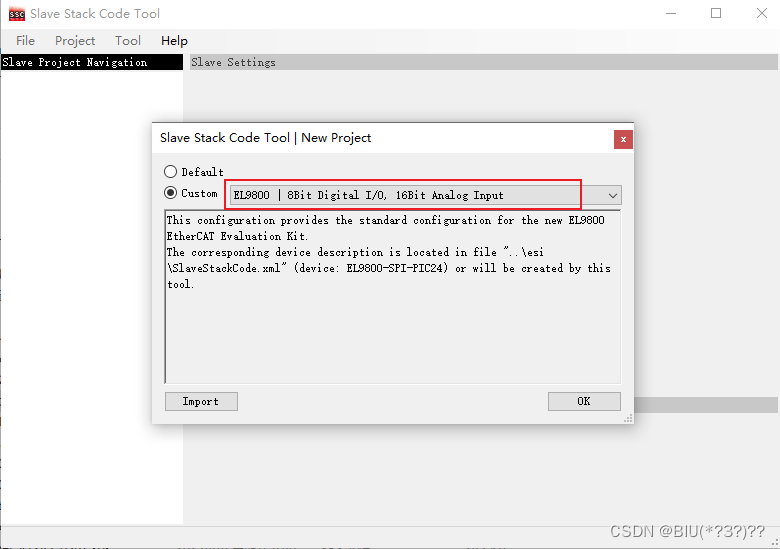

- 新建SSC文件(建议使用SSC 5.12版本,相对5.11版本需要修改内容更少一点)

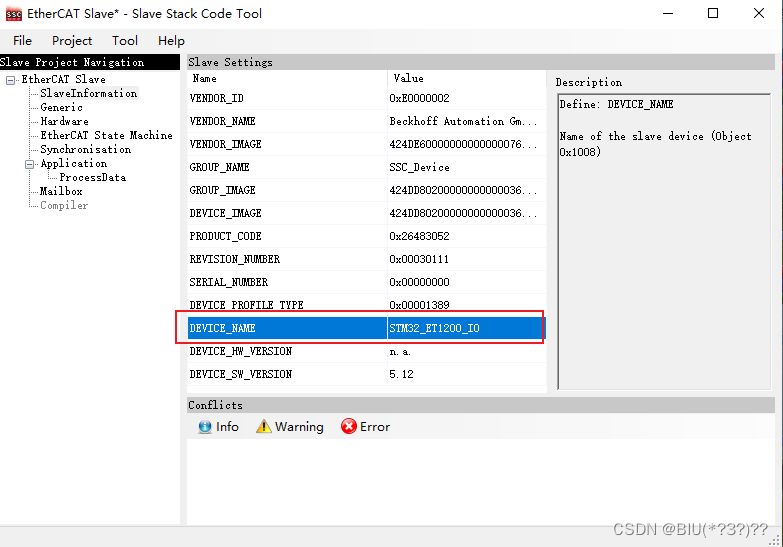

- SlaveInformation 修改

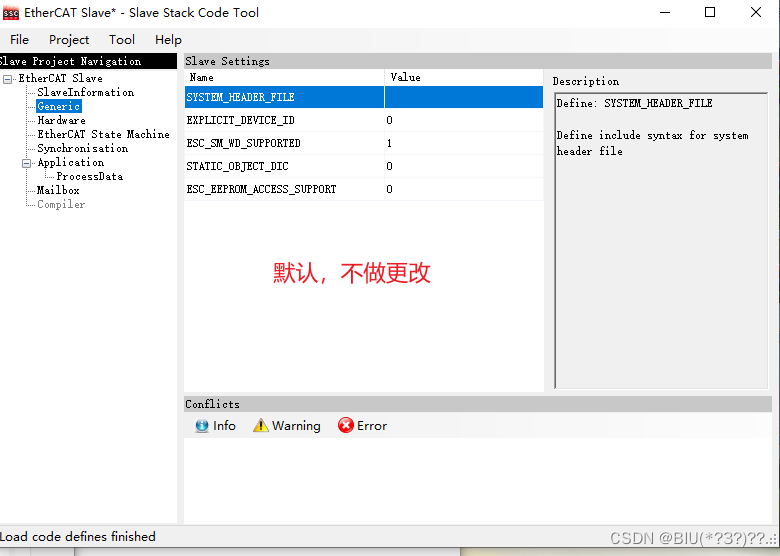

- Generic保持不变

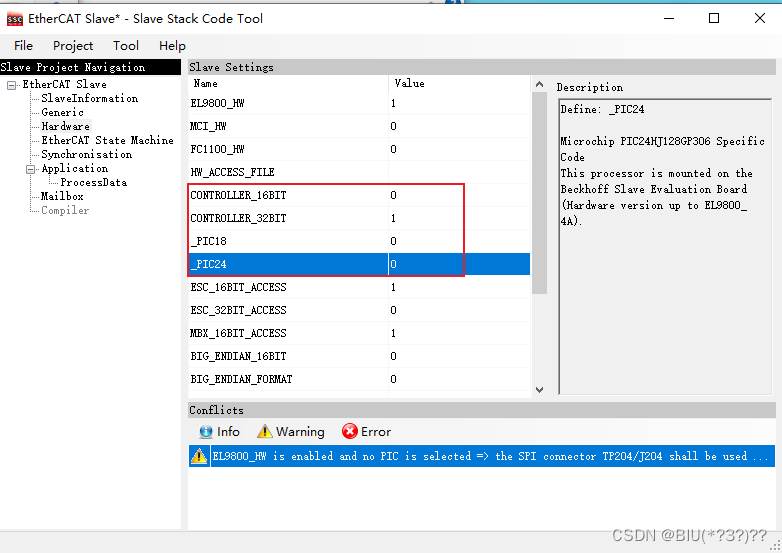

- HardWare修改,适配STM32

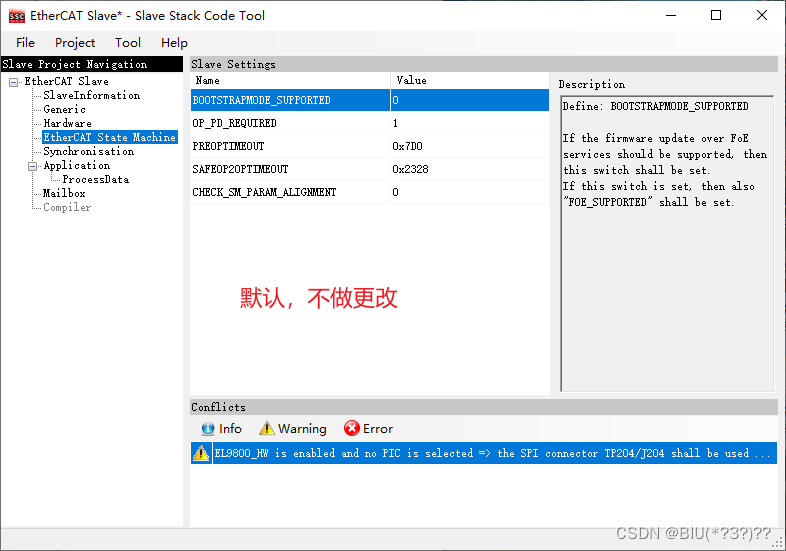

- EtherCAT State Machine 保持不变

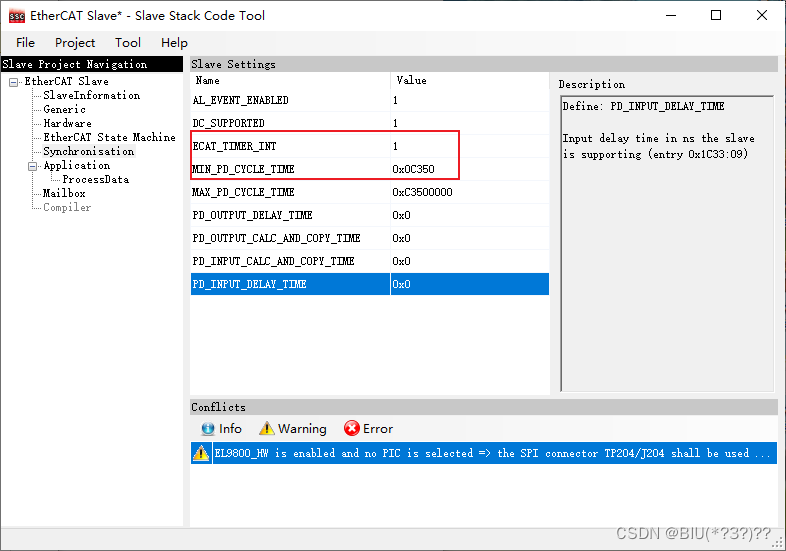

- Synchronisation 修改:增加1ms定时器,用于EtherCAT看门狗

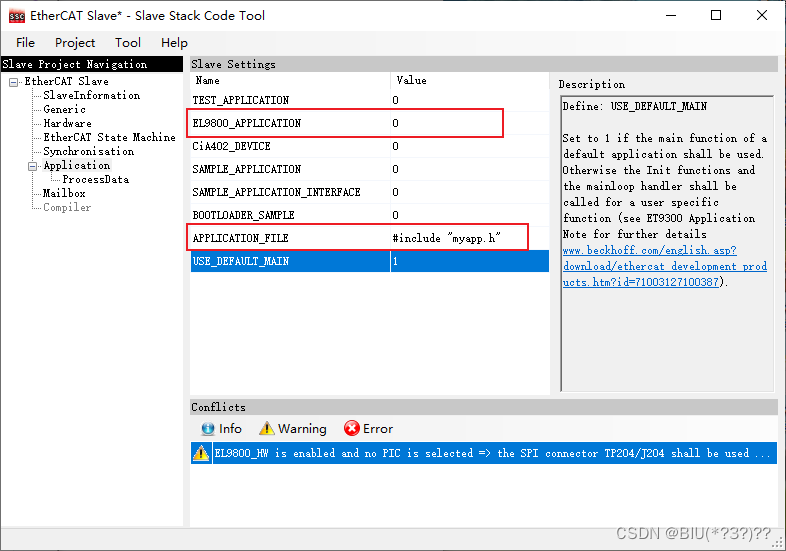

- Application 修改:不使用el9800app,c,增加头文件包含。(保存后再打开该项会变少)

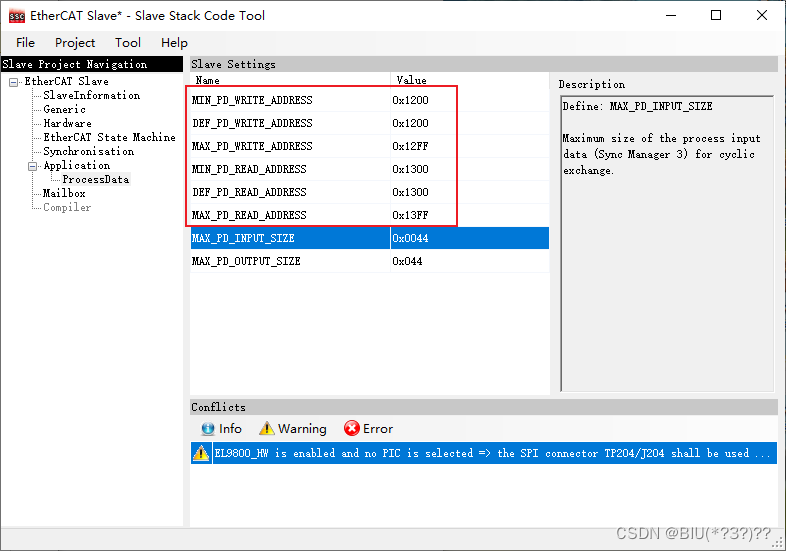

- ProcessData 修改:修改PDO数据传输地址

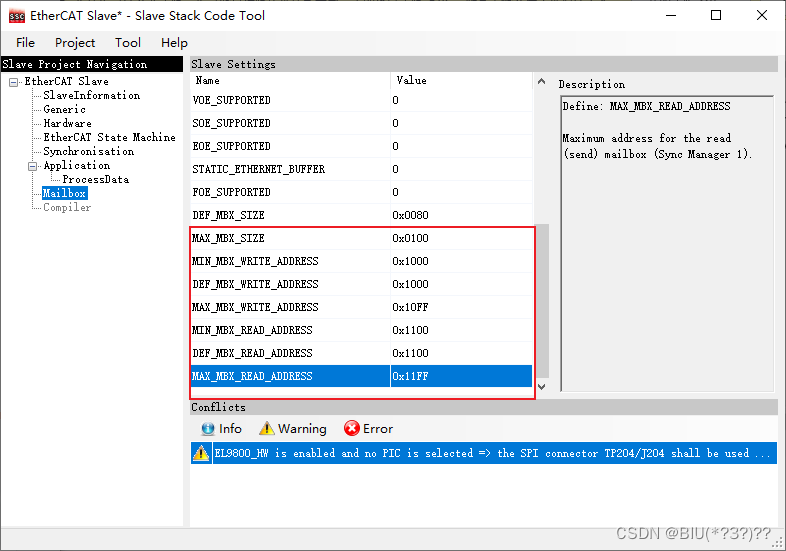

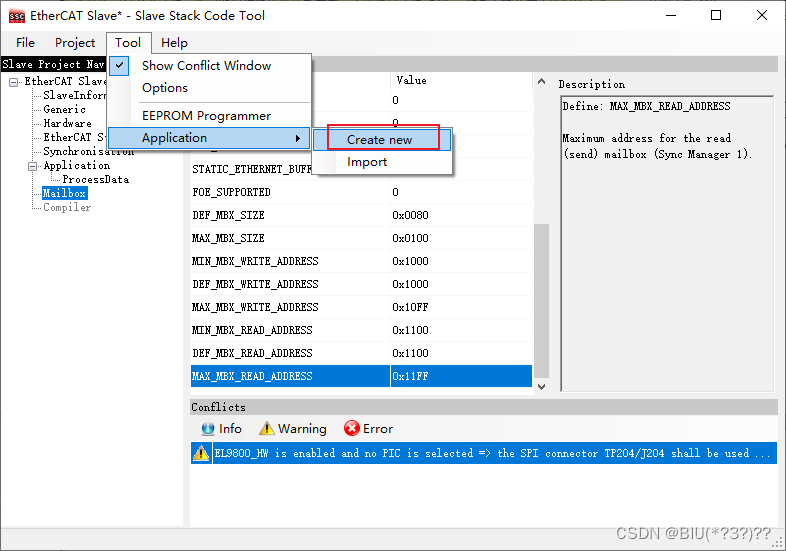

- MailBox 修改:修改SM传输地址

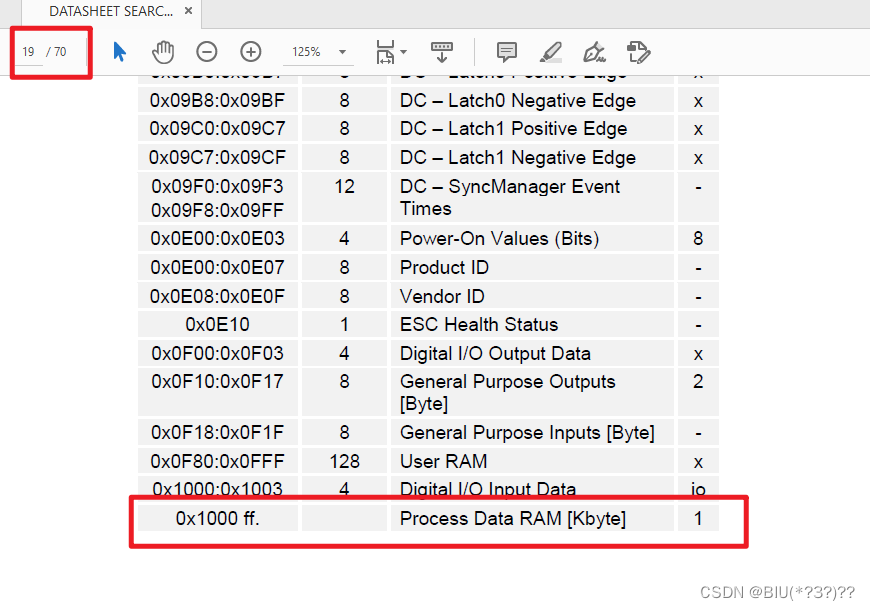

ET1200只有1K内存,范围0x1000~0x1400;0x1000~0x11FF 分配给邮箱,0x1200~0x13FF分配给PDO

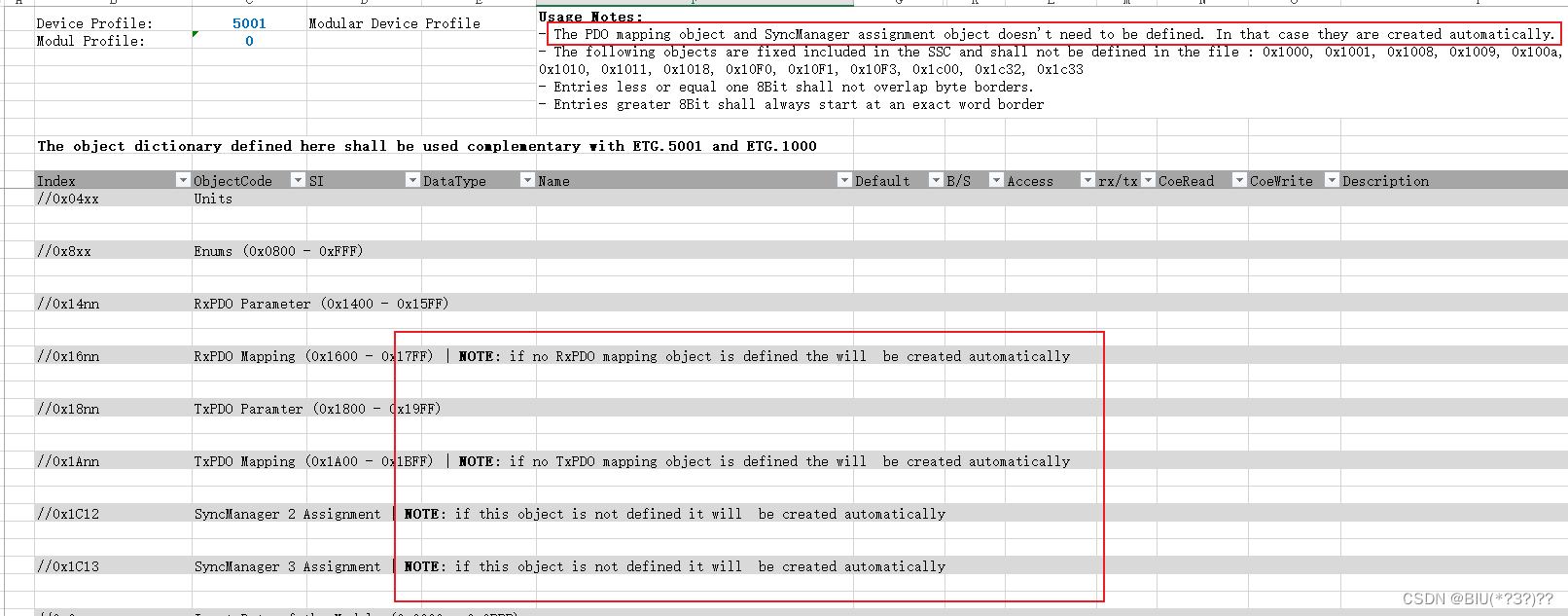

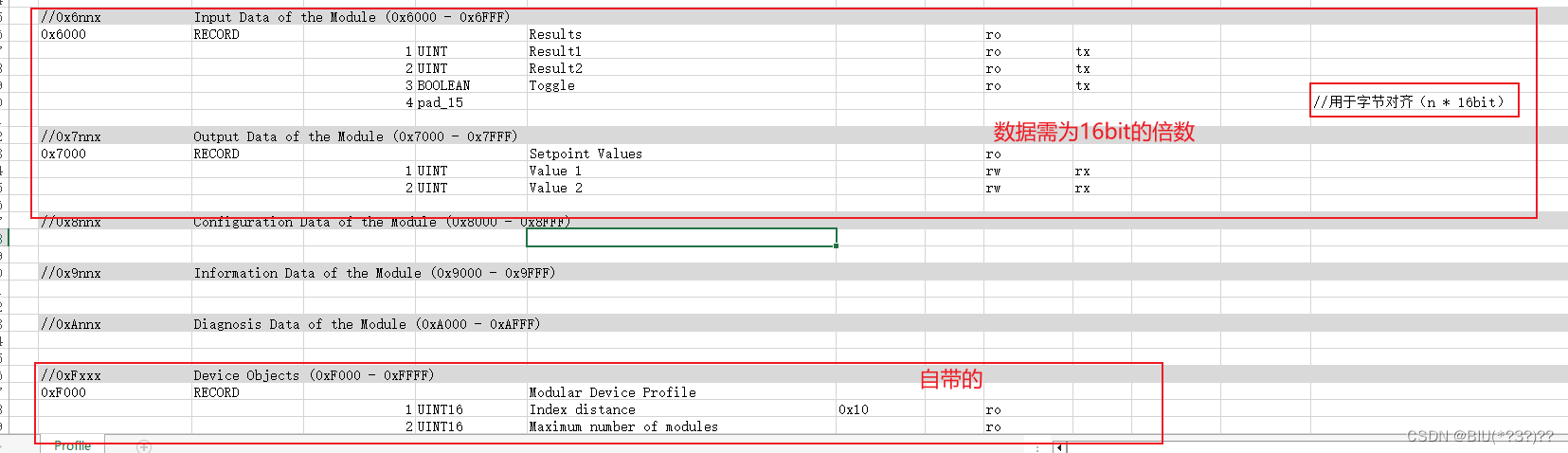

- 添加PDO变量

- 在打开的Excel表格中添加要传输的PDO变量

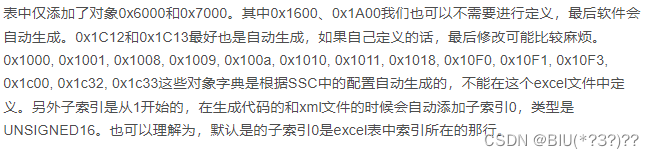

- 映射部分地址会自动生成,无需添加,只需要添加0x6000和0x7000的PDO就行

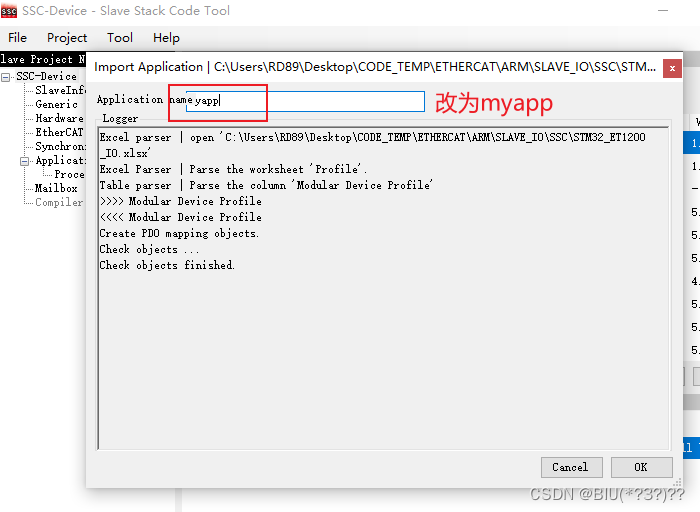

- 保存并改名为myapp

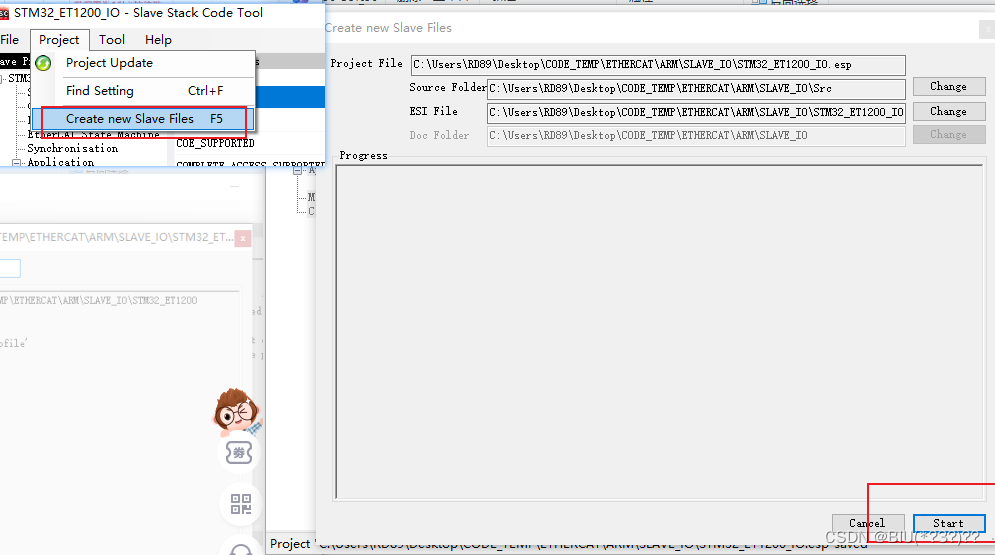

- 生成EtherCAT代码

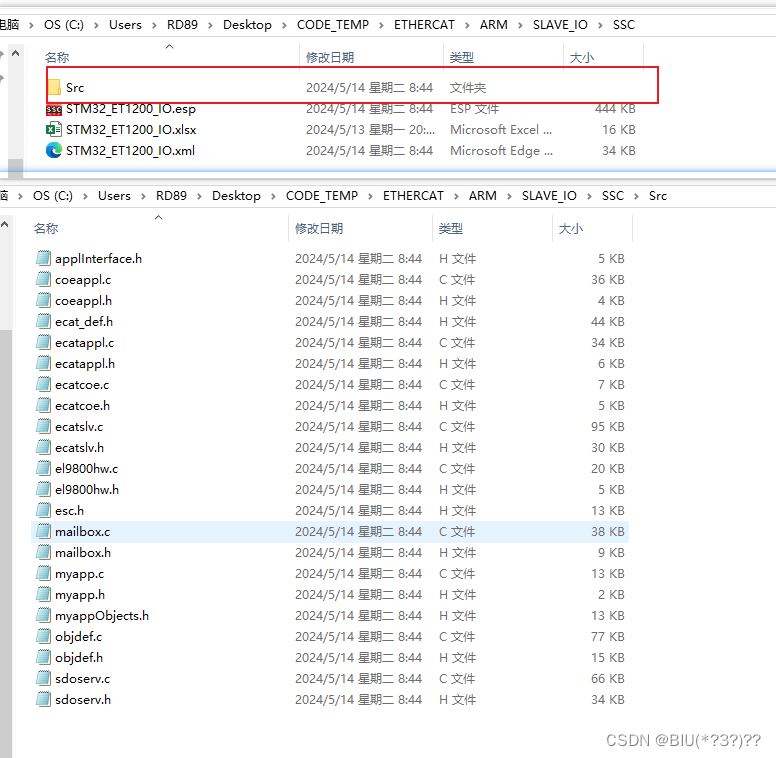

- 生成代码及位置如下所示

从站操作,修改STM32相应程序

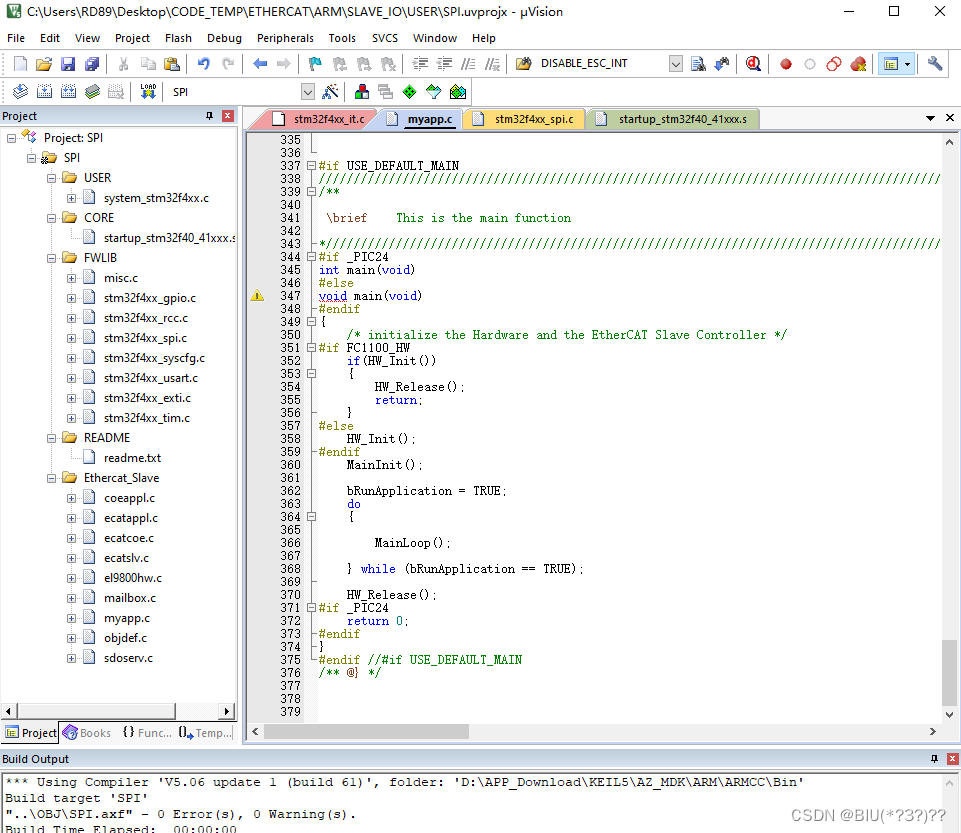

将生成的代码文件导入项目中,项目列表如下图。主函数在myapp.c的最底部 修改el9800hw.c文件:

修改el9800hw.c文件:

- 根据报错去添加define(由于没有用到SYNC1,所以SYNC1的定义不做任何处理)

- 添加spi、timer和exit初始化函数

- 修改RxTxSpiData函数,改成SPI先发送后接收函数

- 增加定时器中断处理函数

/*

* This source file is part of the EtherCAT Slave Stack Code licensed by Beckhoff Automation GmbH & Co KG, 33415 Verl, Germany.

* The corresponding license agreement applies. This hint shall not be removed.

*/

/**

\addtogroup EL9800_HW EL9800 Platform (Serial ESC Access)

@{

*/

/**

\file el9800hw.c

\author EthercatSSC@beckhoff.com

\brief Implementation

Hardware access implementation for EL9800 onboard PIC18/PIC24 connected via SPI to ESC

\version 5.12

<br>Changes to version V5.11:<br>

V5.12 EL9800 1: improve the SPI access<br>

<br>Changes to version V5.10:<br>

V5.11 ECAT10: change PROTO handling to prevent compiler errors<br>

V5.11 EL9800 2: change PDI access test to 32Bit ESC access and reset AL Event mask after test even if AL Event is not enabled<br>

<br>Changes to version V5.01:<br>

V5.10 ESC5: Add missing swapping<br>

V5.10 HW3: Sync1 Isr added<br>

V5.10 HW4: Add volatile directive for direct ESC DWORD/WORD/BYTE access<br>

Add missing swapping in mcihw.c<br>

Add "volatile" directive vor dummy variables in enable and disable SyncManger functions<br>

Add missing swapping in EL9800hw files<br>

<br>Changes to version V5.0:<br>

V5.01 HW1: Invalid ESC access function was used<br>

<br>Changes to version V4.40:<br>

V5.0 ESC4: Save SM disable/Enable. Operation may be pending due to frame handling.<br>

<br>Changes to version V4.30:<br>

V4.40 : File renamed from spihw.c to el9800hw.c<br>

<br>Changes to version V4.20:<br>

V4.30 ESM: if mailbox Syncmanger is disabled and bMbxRunning is true the SyncManger settings need to be revalidate<br>

V4.30 EL9800: EL9800_x hardware initialization is moved to el9800.c<br>

V4.30 SYNC: change synchronisation control function. Add usage of 0x1C32:12 [SM missed counter].<br>

Calculate bus cycle time (0x1C32:02 ; 0x1C33:02) CalcSMCycleTime()<br>

V4.30 PDO: rename PDO specific functions (COE_xxMapping -> PDO_xxMapping and COE_Application -> ECAT_Application)<br>

V4.30 ESC: change requested address in GetInterruptRegister() to prevent acknowledge events.<br>

(e.g. reading an SM config register acknowledge SM change event)<br>

GENERIC: renamed several variables to identify used SPI if multiple interfaces are available<br>

V4.20 MBX 1: Add Mailbox queue support<br>

V4.20 SPI 1: include SPI RxBuffer dummy read<br>

V4.20 DC 1: Add Sync0 Handling<br>

V4.20 PIC24: Add EL9800_4 (PIC24) required source code<br>

V4.08 ECAT 3: The AlStatusCode is changed as parameter of the function AL_ControlInd<br>

<br>Changes to version V4.02:<br>

V4.03 SPI 1: In ISR_GetInterruptRegister the NOP-command should be used.<br>

<br>Changes to version V4.01:<br>

V4.02 SPI 1: In HW_OutputMapping the variable u16OldTimer shall not be set,<br>

otherwise the watchdog might exceed too early.<br>

<br>Changes to version V4.00:<br>

V4.01 SPI 1: DI and DO were changed (DI is now an input for the uC, DO is now an output for the uC)<br>

V4.01 SPI 2: The SPI has to operate with Late-Sample = FALSE on the Eva-Board<br>

<br>Changes to version V3.20:<br>

V4.00 ECAT 1: The handling of the Sync Manager Parameter was included according to<br>

the EtherCAT Guidelines and Protocol Enhancements Specification<br>

V4.00 APPL 1: The watchdog checking should be done by a microcontroller<br>

timer because the watchdog trigger of the ESC will be reset too<br>

if only a part of the sync manager data is written<br>

V4.00 APPL 4: The EEPROM access through the ESC is added

*/

/*--------------------------------------------------------------------------------------

------

------ Includes

------

--------------------------------------------------------------------------------------*/

#include "ecat_def.h"

#include "ecatslv.h"

#define _EL9800HW_ 1

#include "el9800hw.h"

#undef _EL9800HW_

/*remove definition of _EL9800HW_ (#ifdef is used in el9800hw.h)*/

#include "ecatappl.h"

/*--------------------------------------------------------------------------------------

------

------ internal Types and Defines

------

--------------------------------------------------------------------------------------*/

typedef union

{

unsigned short Word;

unsigned char Byte[2];

} UBYTETOWORD;

typedef union

{

UINT8 Byte[2];

UINT16 Word;

}

UALEVENT;

#define EtherCAT_SPIx SPI1

#define SELECT_SPI GPIO_ResetBits(GPIOE, GPIO_Pin_1);

#define DESELECT_SPI GPIO_SetBits(GPIOE, GPIO_Pin_1);

#define ETHERCAT_SPI_INIT SPI1_Init()

#define EscIsr EXTI0_IRQHandler

#define Sync0Isr EXTI15_10_IRQHandler

#define Sync1Isr EXTI9_5_IRQHandler

#define TimerIsr TIM2_IRQHandler

#define ACK_TIMER_INT TIM_ClearITPendingBit(TIM2,TIM_IT_Update);

#define INIT_ESC_INT Esc_Init();

#define INIT_SYNC0_INT SYNC0_Init();

#define INIT_SYNC1_INT

#define ENABLE_SYNC0_INT

#define ENABLE_SYNC1_INT

#define INIT_ECAT_TIMER TIM2_Init(1000-1,168-1)

#define START_ECAT_TIMER TIM_Cmd(TIM2, ENABLE)

#define ENABLE_GLOBAL_INT __enable_irq()

#define DISABLE_GLOBAL_INT __disable_irq()

#define ACK_

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1998

1998

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?