原文章:https://blog.csdn.net/edadoc2013/article/details/51581565#commentBox

心得:

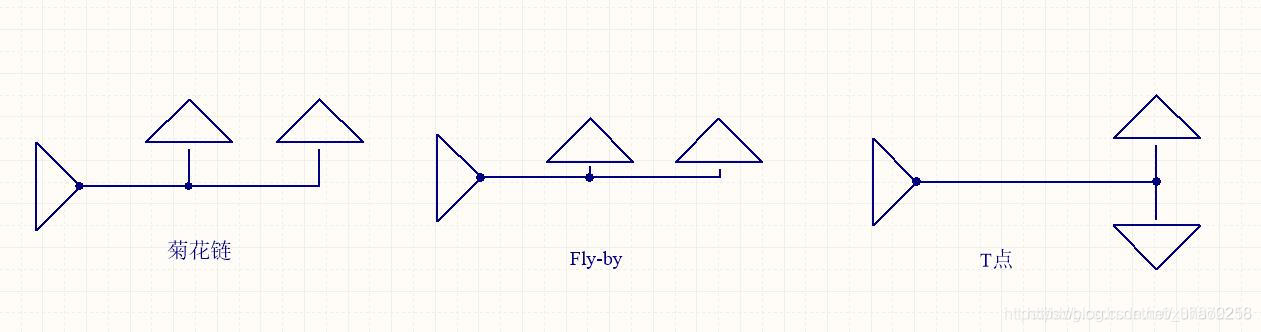

在高速电路中往往涉及到多个高速存储设备,因此合理的拓扑结构对布局走线非常重要。主流的拓扑模式有菊花链、fly-by与T点。

菊花链是相对最为常见的一种拓扑方式。菊花链拓扑的原理可以解释为:将所有的总线视作拓扑的干路,从处理器引出之后,每个存储设备所需要的总线视为支路,也称为“SUB线”。从微机原理的角度上讲,更像是将所有的总线视作一条“大总线”,每个内存设备需要总线的时候,直接从“大总线”中引入自己需要的数据总线、地址总线与控制总线。

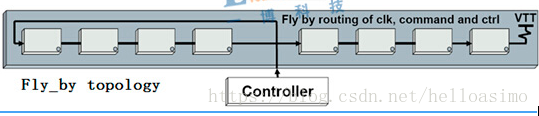

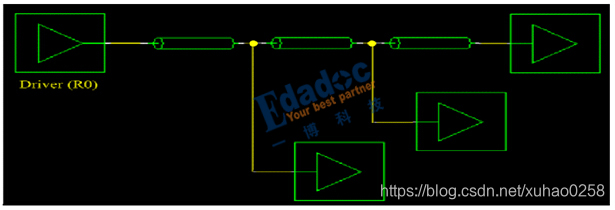

Fly-by拓扑实际上是菊花链拓扑中的一种特殊情况。当菊花链拓扑中的支路,也就是“SUB线”相当短的时候,可以将其称作为“fly-by”。Fly-by拓扑常见于DDR内存的设计中,由于DDR内存的存储速度极高,且DDR内存上的内存芯片往往是规则成行排布的,因此使用fly-by拓扑相对比较合适。

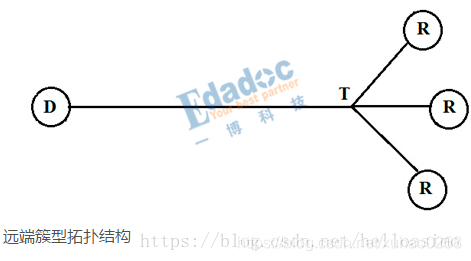

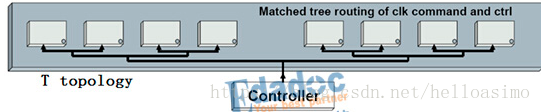

最后一种叫T点拓扑。从拓扑的模型上来看比较像一个二叉树,当遇到分支点后将总线分开为每个高速存储设备提供总线。该拓扑相对来讲比较占用电路板空间,但是方便做等长线。

1.

Flyby优点: 数据组不需要和时钟信号绕等长,这样就可以节省较多的布线空间,同时也可以支持更高的信号速率;

“数据组不需要和时钟信号绕等长”, 参考https://blog.csdn.net/helloasimo/article/details/81950120里面的这句话:

当然,Fly_by拓扑是针对DDR3的时钟、地址控制和命令信号而言,数据信号就不存在fly-ly拓扑的说法啦.

时钟(CK.CK#)、地址(A15~A0)、控制和命令信号(RAS#,CAS#,WE#)-----括号是我自己加的,不确定是否正确;

缺点:信号到达每片颗粒的时间不一致,带来了一定的skew。

T型特点(非优点):主控到每个颗粒的长度基本一致,也就是说每个颗粒的信号质量都差不多;

缺点:就是绕等长时需要更多的布线空间,所以不适合较多颗粒数目的情况,其次是需要同等地位的分支完全对称(包括长度及阻抗等),如果不对称那么信号质量的影响比较大。从信号速率来考虑。一般T型拓扑频率超过1GHz信号质量就会出现大幅的下降,所以此时应考虑使用fly_by拓扑结构。

2.

从上面的分析看,使用Flyby比T型好很多,因此我理解大部分情况都可以用Flyby;

但下面转载的这个文章,写到如果主控芯片不支持读写平衡功能,则必须用T型;我还没弄明白,如果你懂,请在文末给我评论/留言。

https://blog.csdn.net/helloasimo/article/details/81950160

3.

另外,文章提到的非常重要的一句话:

常用的端接方式是而Fly_by则是在最后一个颗粒处上拉50欧姆或其他端接电阻到Vtt;

T型拓扑在第一个分支节点处上拉50欧姆或其他端接电阻到Vtt;

除了端接电阻,其实当颗粒数目较多时,都可以将两种拓扑的主干线路阻抗降低到40欧姆左右,这样有利于提升信号的质量(前期文章也有讲到过,不再赘述)。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?